High-performance ECC coprocessor system resistant to power consumption attack

A co-processor, high-performance technology, applied in the architecture with a single central processor, electrical digital data processing, instruments, etc., can solve the problems of anti-power attack, power attack, long pipeline delay, etc. Area consumption, modularization of rules, easy modularization effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

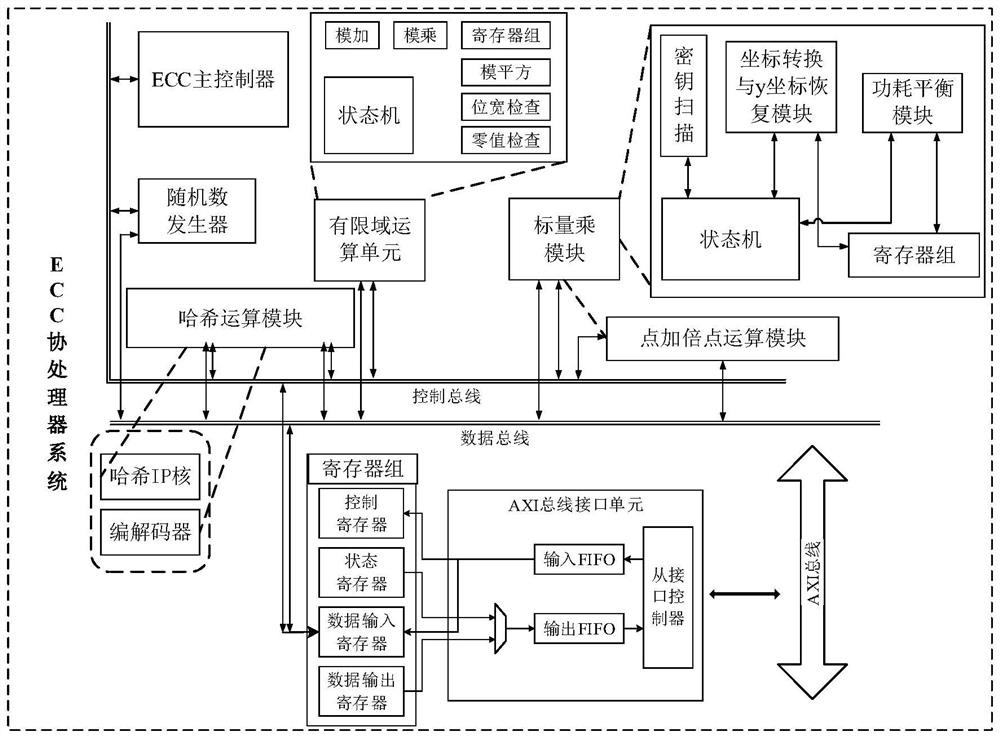

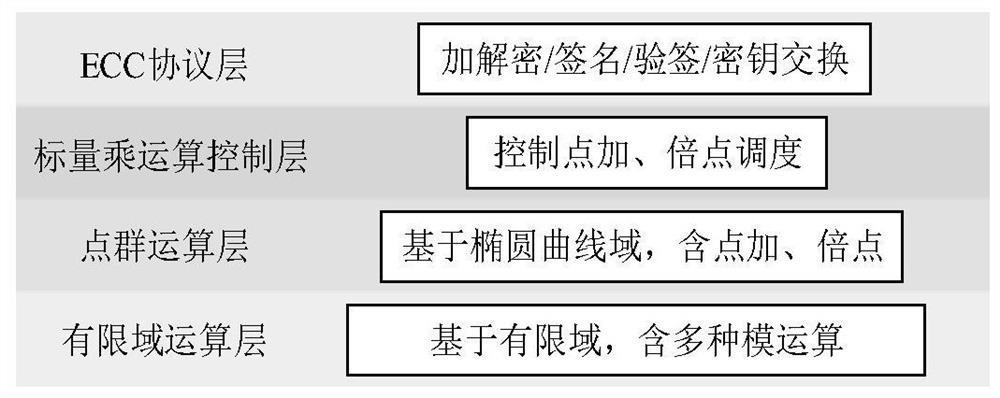

[0029] Such as Figure 1 to Figure 2 As shown, the present invention discloses a high-performance ECC coprocessor system resistant to power consumption attacks, including an ECC main controller, a finite field operation unit, a scalar multiplication module, a random number generator, a hash operation module, a register set and AXI bus interface unit. The function can be realized by mounting the designed coprocessor on the existing RSIC-V-based S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More