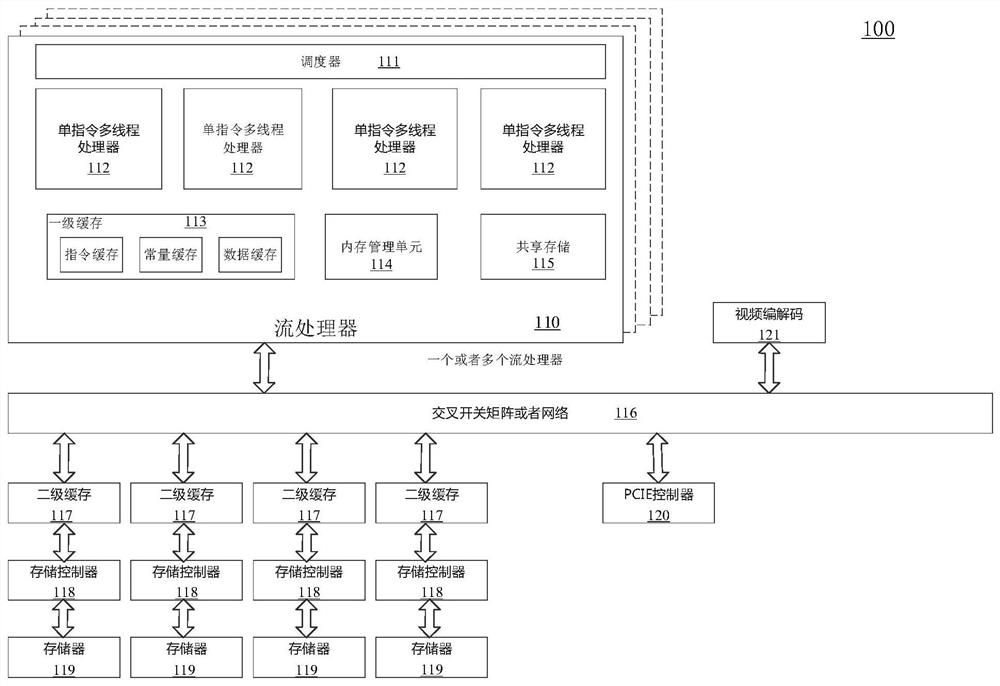

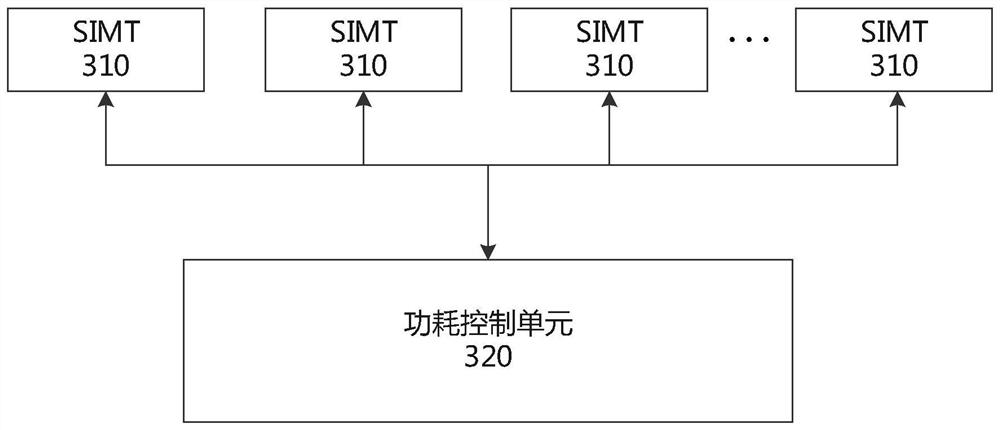

Multi-core processing device and power consumption control method thereof

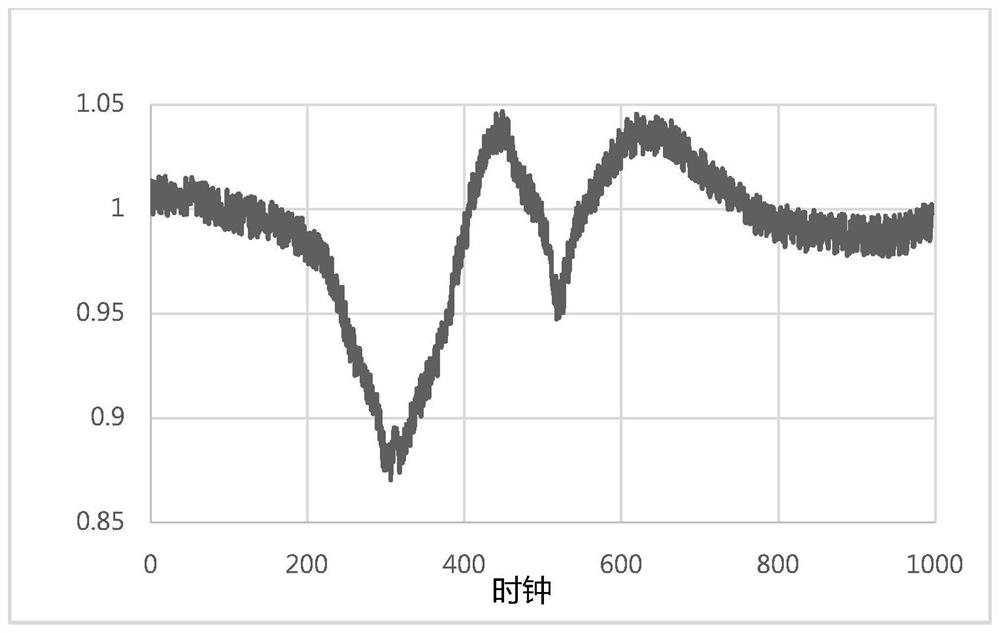

A technology of processing device and power consumption control, applied in the direction of electrical digital data processing, digital data processing components, instruments, etc., can solve the problems of capacitor packaging, large occupation area, easy to miss time points, etc., to reduce the overall power consumption , reduce the voltage drop, improve the processing frequency and the effect of performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0070] The technical solutions of the present application will be clearly and completely described below through the embodiments and in conjunction with the accompanying drawings, but the present application is not limited to the embodiments described below. Based on the following embodiments, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present application. For clarity, parts irrelevant to describing the exemplary embodiments are omitted in the drawings.

[0071] It should be understood that terms such as "comprising" or "having" in this application are intended to indicate the existence of features, numbers, steps, acts, components or combinations thereof disclosed in this specification, and do not exclude one or more other features. , numbers, steps, actions, parts, or combinations thereof exist or are added to. "Multiple" in this application can usually be interpreted as two or more...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More