Simulation ending mechanism based on UVM verification platform

A verification platform and mechanism technology, applied in special data processing applications, CAD circuit design, etc., can solve problems such as long simulation time, increase the difficulty of problem debugging, and difficult to determine the waiting time, and achieve accurate simulation end control and verification work efficiency. The effect of high and reduced debugging difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, and the present invention will be further elaborated.

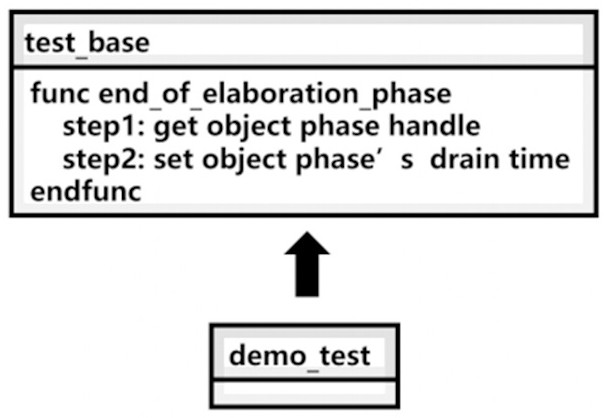

[0022] First, combine the Figure 2~4 Describe the simulation end mechanism based on the UVM verification platform according to the embodiment of the present invention, which is used to verify mobile phone chips, and has a wide range of application scenarios.

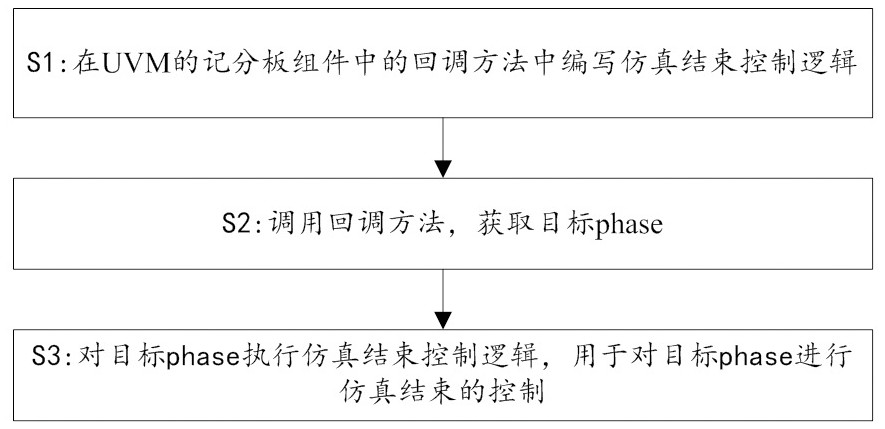

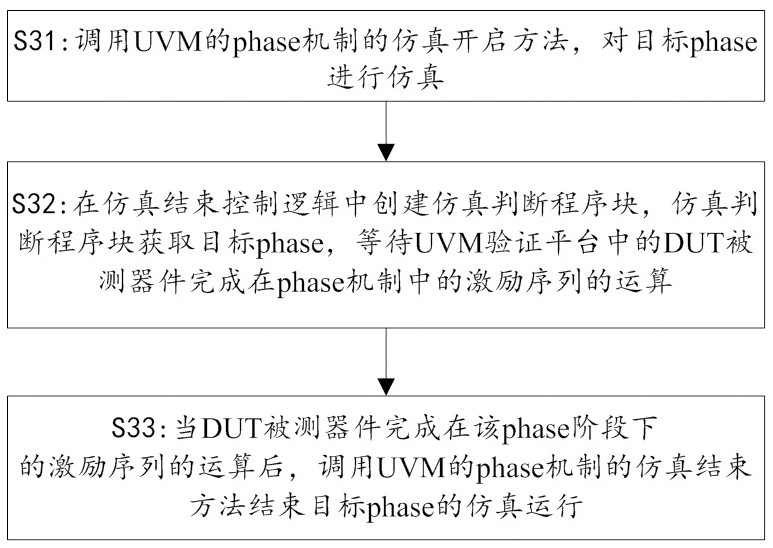

[0023] Such as figure 2 , 4 As shown, the simulation end mechanism based on the UVM verification platform of the embodiment of the present invention includes the following steps:

[0024] In S1, as in figure 2 , 4 As shown, the simulation end control logic is written in the callback method (phase_ready_to_end) in UVM's scoreboard component (scoreboard), so as to achieve the effect of controlling the end of the simulation in the simulation running phase of the project instead of the compilation phase.

[0025] In S2, as in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More