Semiconductor structure and forming method thereof

A semiconductor and gate structure technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of semiconductor structure damage, structural failure, and inability to protect metal gates well

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] It can be seen from the background art that the formation method of the semiconductor structure in the prior art is easy to cause damage to the gate structure, and the reason for the damage to the gate structure is analyzed in combination with a formation method of the semiconductor structure.

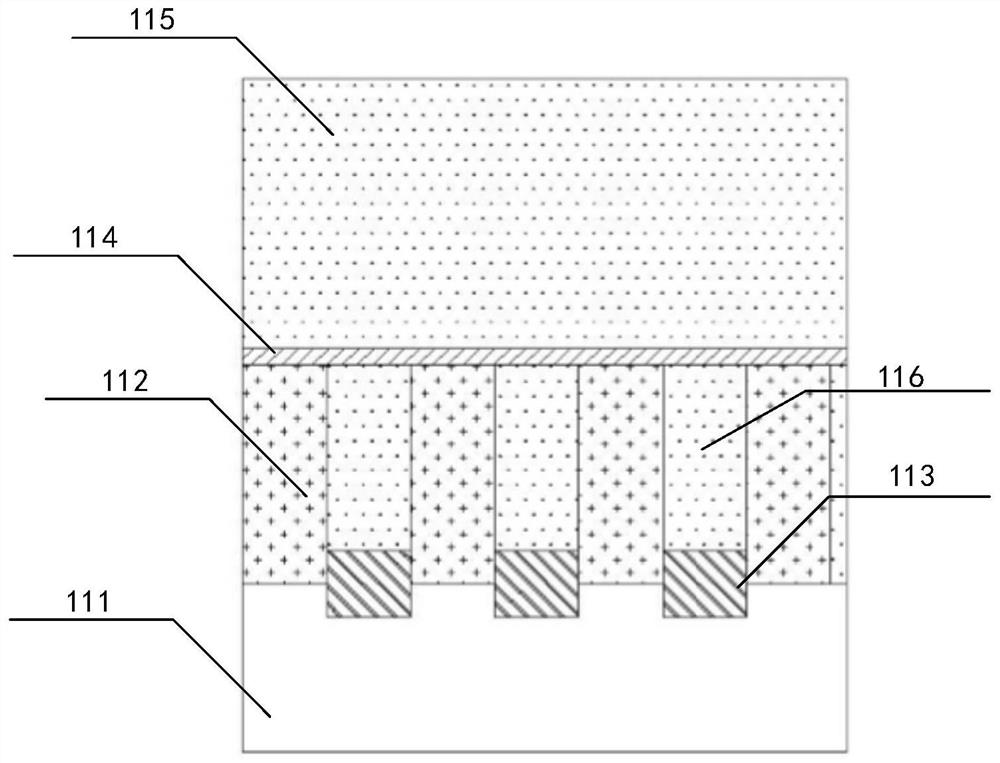

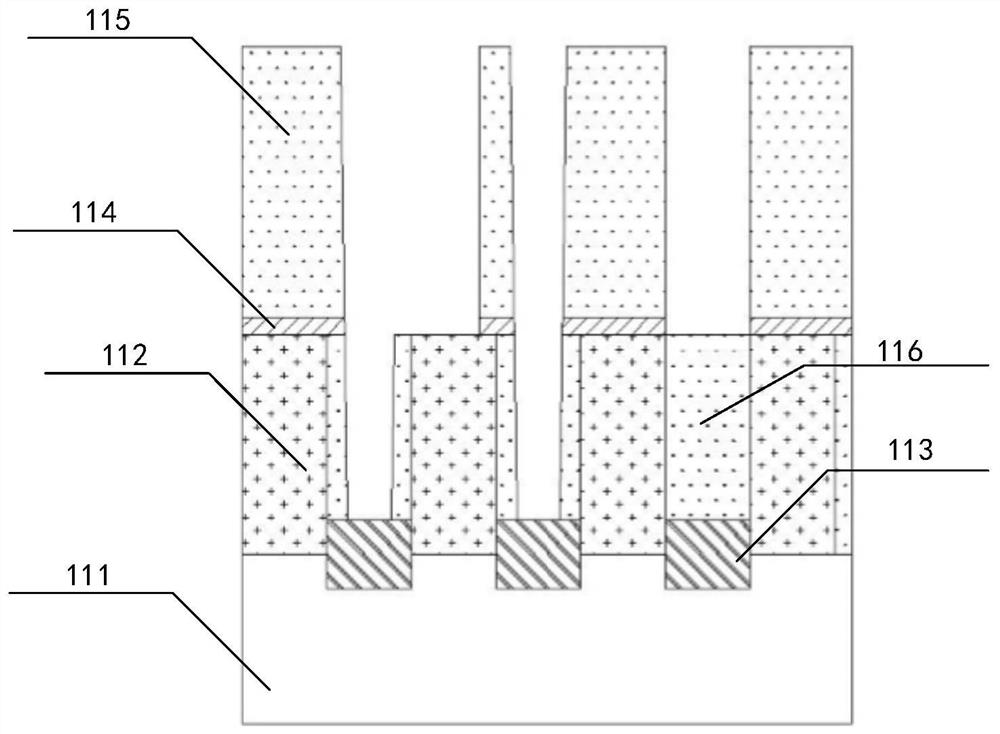

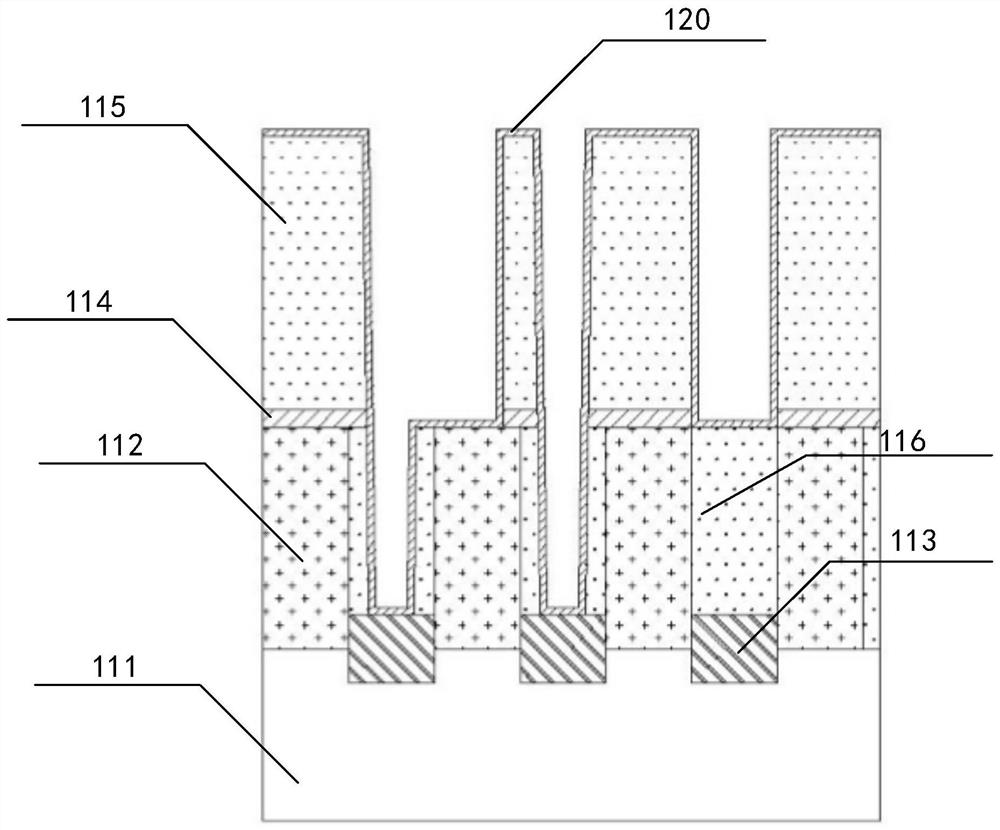

[0048] Please refer to Figure 1-Figure 5 , Figure 1 to Figure 5 It is a structural schematic diagram corresponding to each step in a method for forming a semiconductor structure.

[0049] Such as figure 1 As shown, a substrate is provided, and the substrate includes a substrate 111, a gate structure 112 on the substrate 111, source and drain doped regions 113 on both sides of the gate structure 112, and a 112 and the isolation layer 114 on the source-drain doped region 113, the first dielectric layer 115 and the second dielectric layer 116 above the isolation layer 114, and the second dielectric layer 116 is located adjacent to the gate between the electrode structures 112 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More