Simulation domain near memory computing array structure based on magnetic random access memory

A technology of random access memory and computing array, which is applied in the circuit design of multi-bit multiplication and accumulation calculation based on memory, and in the field of near-memory computing array structure in the analog domain, which can solve the problem of low TMR in the near-memory computing in the analog domain and non-standard computing in the analog near-memory computing. Linear and other issues, to achieve the effect of improving the equivalent TMR of MRAM, improving the accuracy of calculation results, and high quantization accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

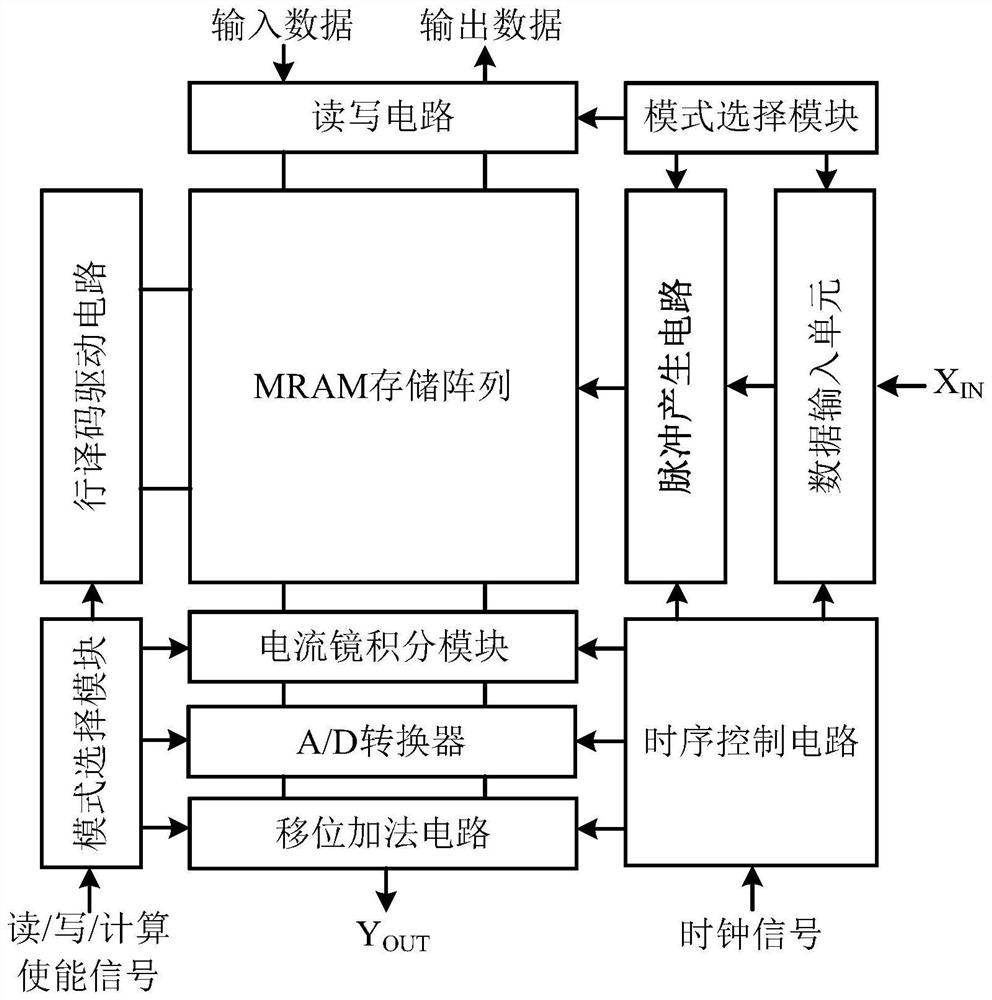

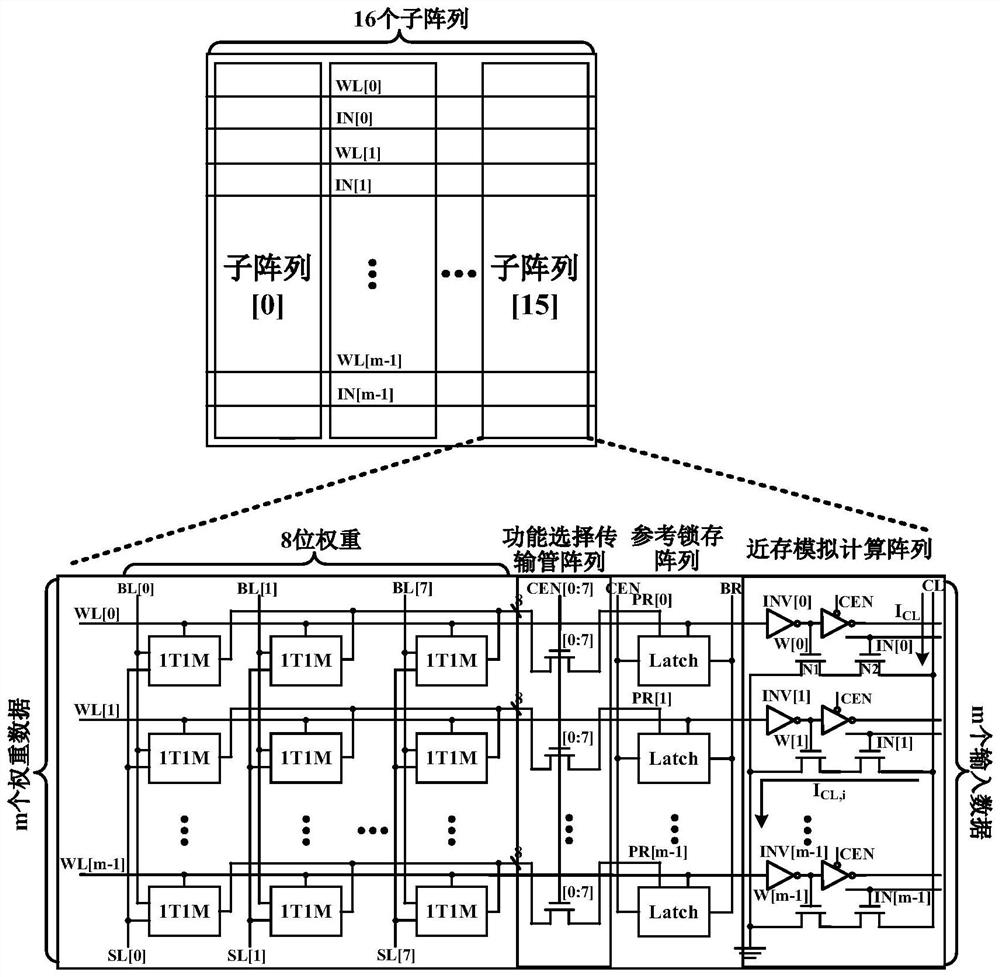

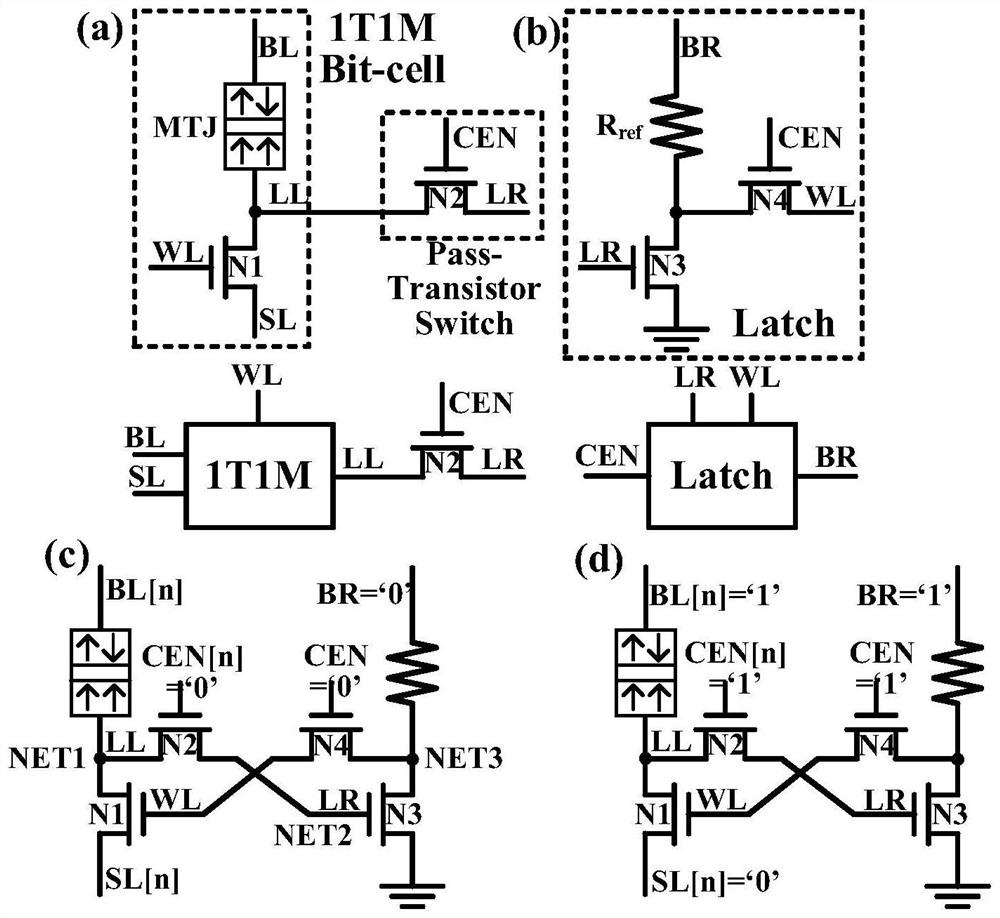

[0096] An MRAM-based analog domain computing array structure described in the present invention includes a 6T2M storage array, a read-write circuit, a row decoding drive circuit, a data input unit, a pulse generation circuit, a current mirror integration module, an A / D converter, a shift A bit addition circuit, a timing control circuit and a mode selection module.

[0097] Such as figure 1 The analog domain storage computing structure shown includes: 1T1M storage units are arranged in a matrix. In the read-write mode, the storage function equivalent to the 1T1M storage array is realized. In the calculation mode, the calculation function of the 1T1M is realized; the row decoding drive circuit and the read The writing circuit is used for row and column decoding and data reading and writing of the storage array in the read-write mode; the data input unit and the pulse generation circuit realize the input of activation data in the calculation mode, and convert the activation data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com