Formation method of semiconductor structure

A semiconductor and patterning technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of uneven key dimensions and poor semiconductor structure performance, and achieve the effect of improving uniformity and performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] It can be seen from the background art that the size uniformity of the pattern structure formed by the current photolithography and etching process is poor. The reasons for the poor uniformity of the graphics are now analyzed in conjunction with the specific drawings.

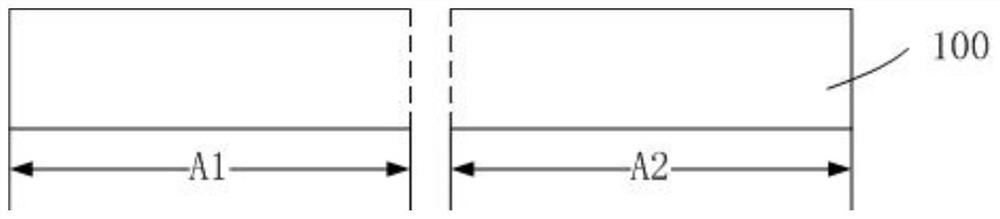

[0031] refer to figure 1 , provide a wafer 100, and the wafer 100 includes several chip regions.

[0032] In a specific embodiment, the wafer 100 located in the chip area can form various semiconductor components, such as various appropriate transistors, memories, field effect transistors, and the like.

[0033] For the convenience of subsequent description, in the semiconductor formation process of this embodiment, two of the chip areas are taken as an example for illustration, including the first chip area A1 and the second chip area A2.

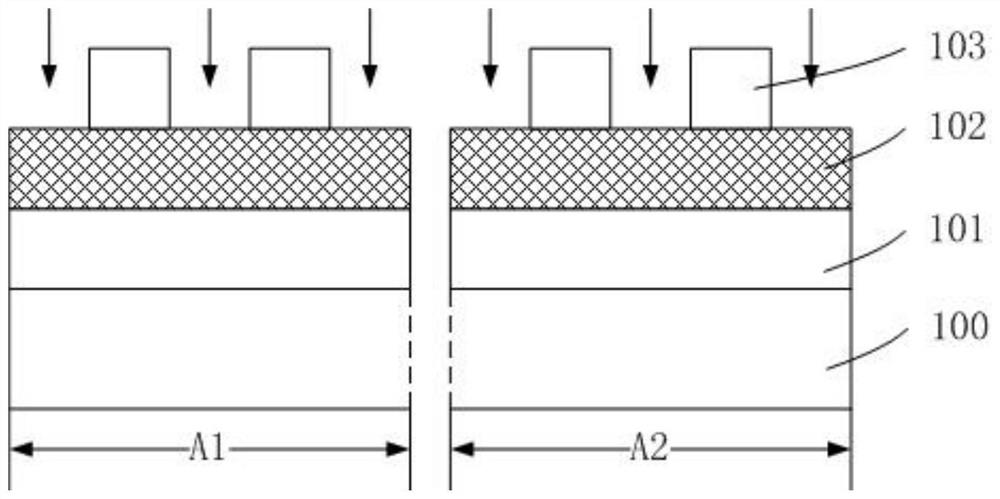

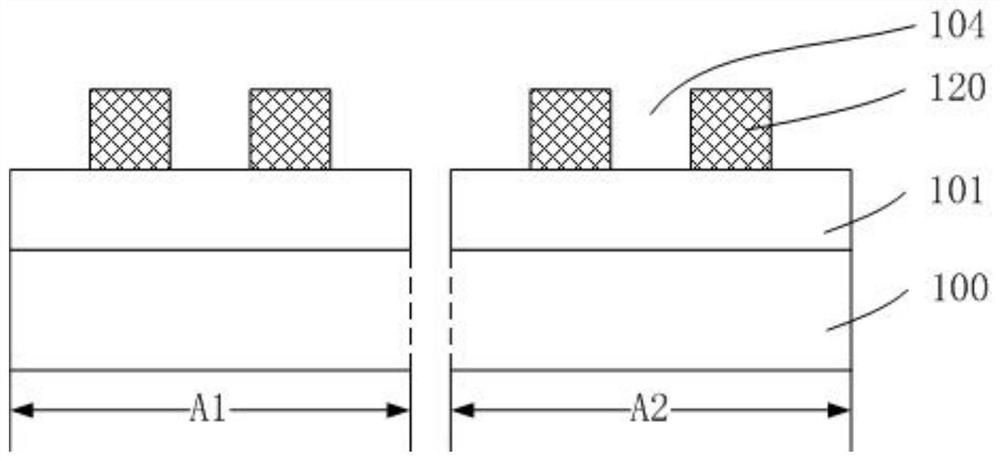

[0034] refer to figure 2 A layer to be etched 101 and a sacrificial material layer 102 are sequentially formed on the wafer 100 in the chip region; a first patt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com