Compiler design implementation method based on risc-v

A technology of risc-v and implementation method, which is applied in the field of compiler design and can solve problems such as compiler performance loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

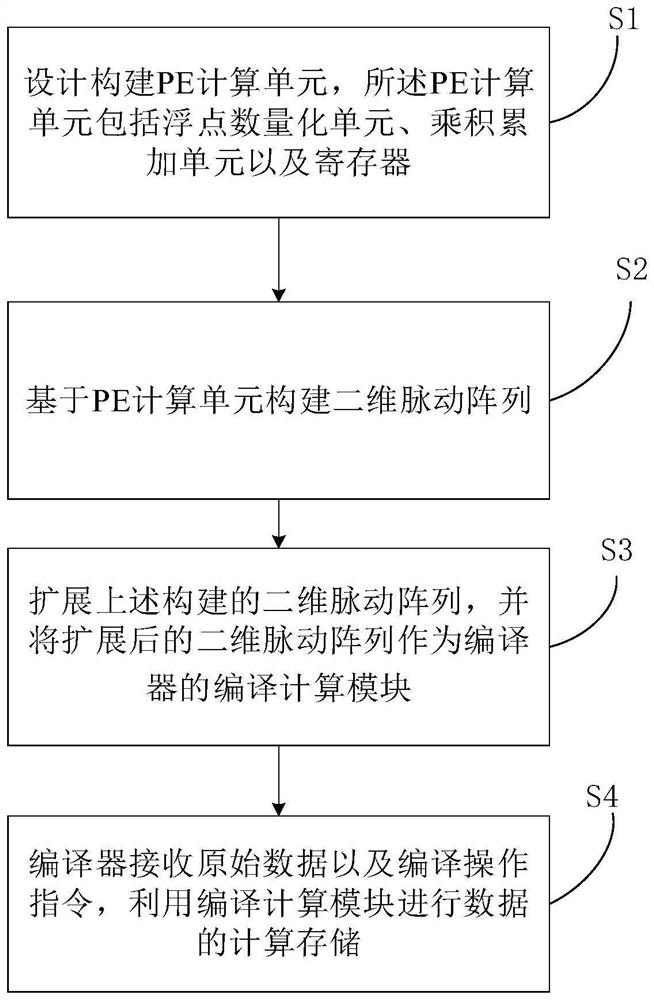

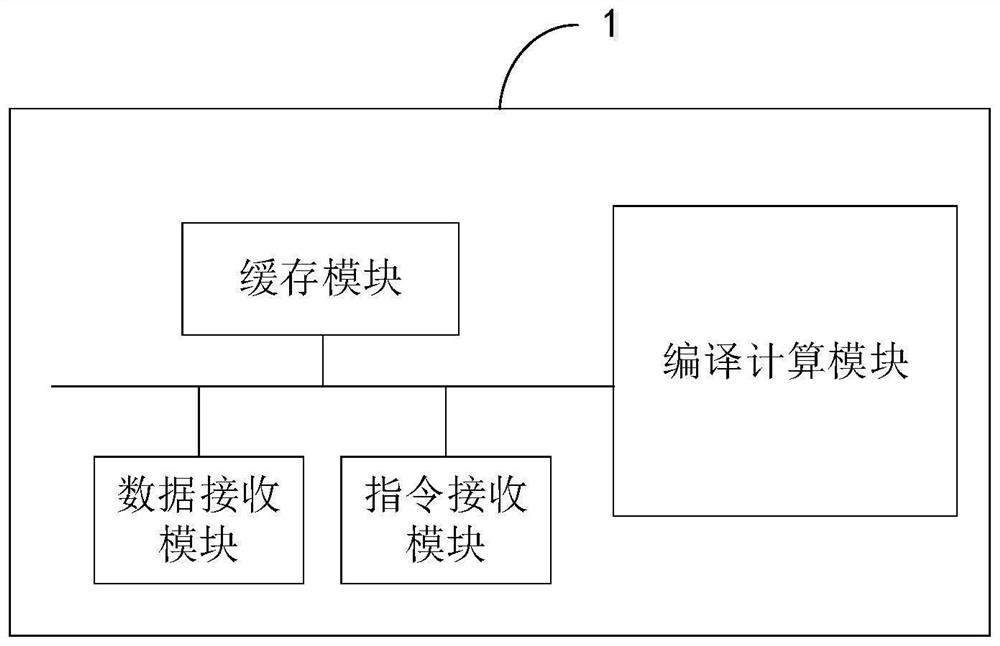

[0063] S1: Design and construct a PE calculation unit, which includes a floating-point quantization unit, a multiply-accumulate unit, and a register.

[0064] In the S1 step, the floating-point quantization unit in the PE calculation unit is designed and constructed, including:

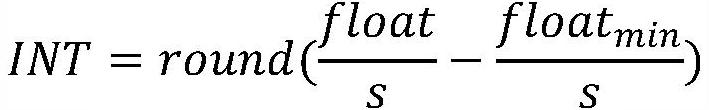

[0065] The floating-point quantization unit performs quantization processing on the floating-point numbers calculated in the multiply-accumulate unit in real time, and the formula of the floating-point quantization processing is:

[0066]

[0067]

[0068] in:

[0069] float represents the floating-point number calculated in the multiply-accumulate unit, and the precision of the floating-point number is FLOAT32;

[0070] INT represents the quantization result of the floating-point number float by the floating-point quantization unit, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More