Function verification method and system of clock domain crossing asynchronous circuit and computer readable storage medium

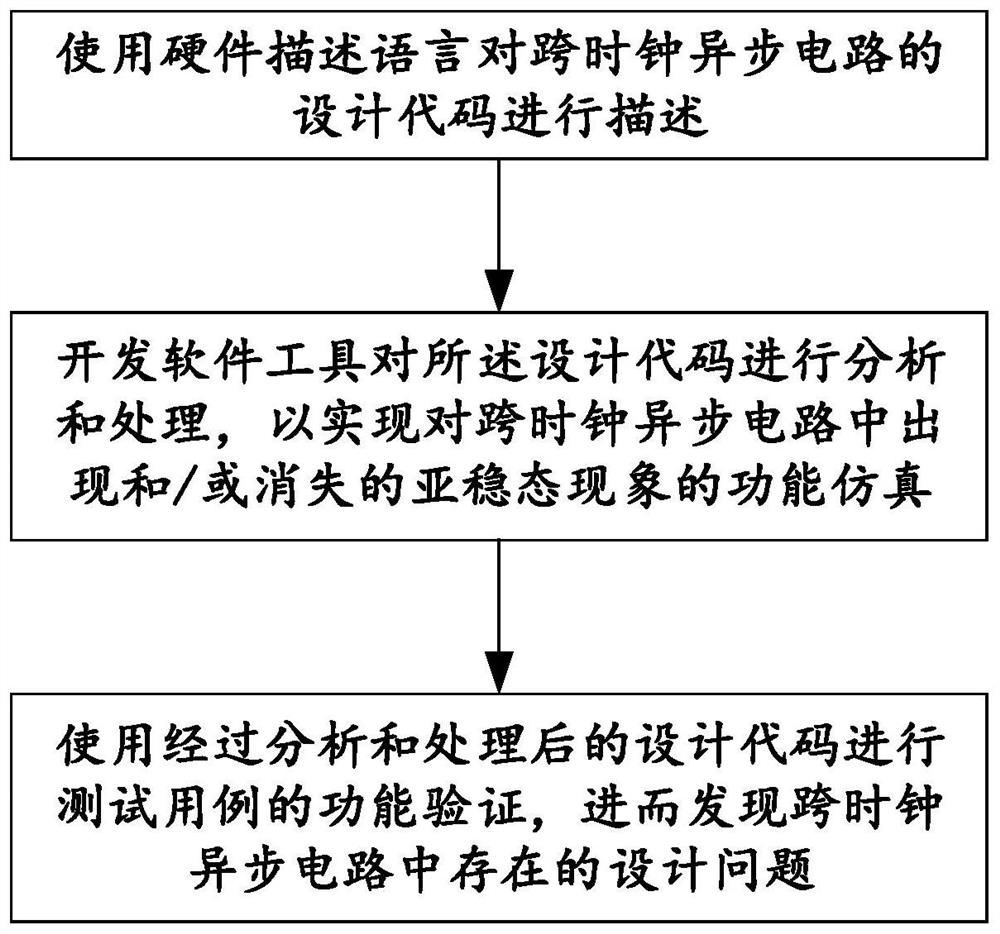

A function verification and asynchronous circuit technology, applied in the computer field, can solve the problems of high time cost, unreasonable timing constraints, and disregard of circuit timing information, etc., to avoid high time cost and solve cross-clock domain asynchronous circuit design problems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

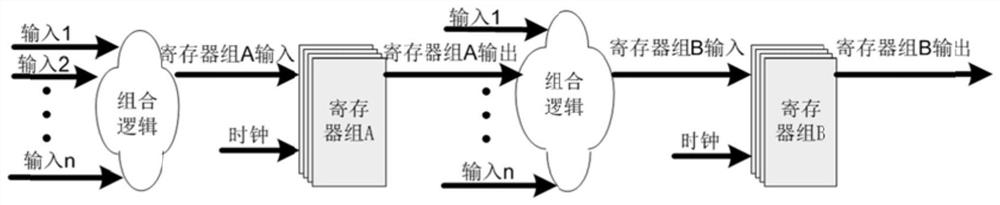

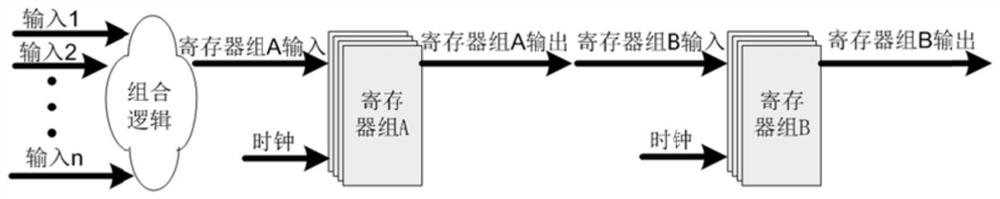

[0035] To make the object, technical scheme and advantages of the present invention more clearly understood, the following in conjunction with the embodiments and accompanying drawings, the present invention will be further elaborated in detail, schematic embodiments of the present invention and description thereof is used to explain the present invention, but not as a limitation of the present invention. Herein, it should also be noted that, in order to avoid obscuring the present invention due to unnecessary details, the accompanying drawings only show a structure and / or processing steps closely related to the embodiment of the present invention, while omitting other details that have little to do with the present invention.

[0036] It should be emphasized that the term "comprising / including" as used herein refers to the presence of features, features, steps or components, but does not exclude the presence or addition of one or more other features, features, steps or compon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More