High-luminous-efficiency LED chip and preparation method thereof

A LED chip, high light efficiency technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of production yield decline, small process window, high production yield, etc., to reduce light absorption, increase process window, light efficiency Enhanced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

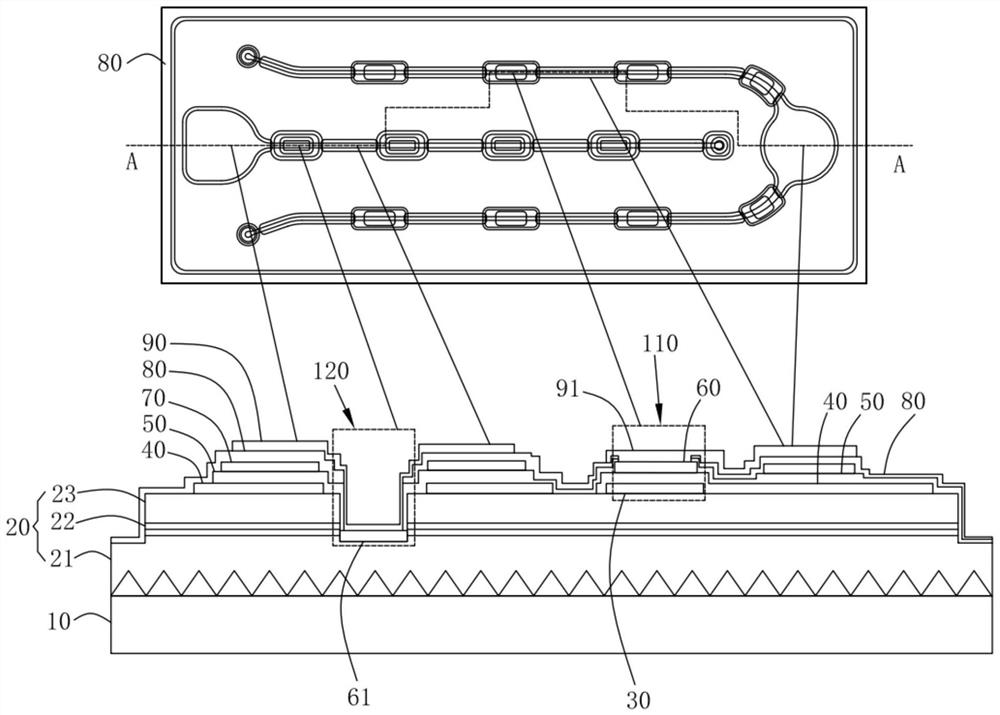

[0033] see figure 1 , the first embodiment of this aspect provides a high light efficiency LED chip, the chip includes a substrate 10 and an epitaxial layer 20, the epitaxial layer 20 includes an N-type semiconductor layer 21, a multiple quantum well region 22 and a P-type semiconductor layer layer 23;

[0034] The chip further includes a current blocking layer 30 provided on the P-type semiconductor layer 23 , a transparent conductive layer 40 provided on the current blocking layer 30 , and a first metal barrier provided on the transparent conductive layer 40 . layer 60 and the second metal barrier layer 61 provided on the N-type semiconductor layer 21 , the first insulating layer 50 provided on the transparent conductive layer 40 , the high reflection layer provided on the first insulating layer 50 a metal layer 70 and a second insulating layer 80 disposed on the high-reflection metal layer 70, the high-reflection metal layer 70 is kept insulated from the metal barrier laye...

Embodiment 2

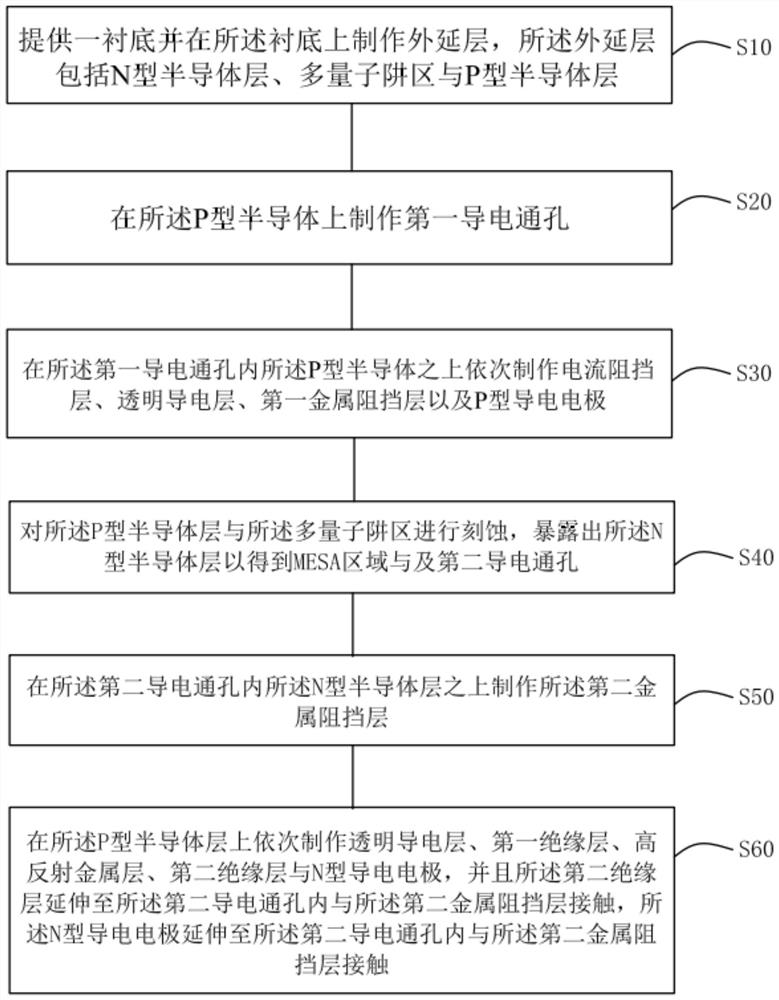

[0041] see figure 2 , the second embodiment of the present invention provides a preparation method of a high light efficiency LED chip, the preparation method is used to prepare the high light efficiency LED chip described in the first embodiment, and the preparation method includes steps S10-S60:

[0042] Step S10, providing a substrate and fabricating an epitaxial layer on the substrate, the epitaxial layer including an N-type semiconductor layer, a multiple quantum well region and a P-type semiconductor layer;

[0043] Step S20, forming a first conductive via on the P-type semiconductor;

[0044] Step S30, forming a current blocking layer, a transparent conductive layer, a first metal blocking layer and a P-type conductive electrode in sequence on the P-type semiconductor in the first conductive via;

[0045] Step S40, etching the P-type semiconductor layer and the multiple quantum well region to expose the N-type semiconductor layer to obtain a MESA region and a second c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More