Virtual inking method for wafer

A wafer and wafer testing technology, applied in the field of integrated circuit manufacturing, can solve the problems of poor ink printing accuracy, error-prone, low efficiency, etc., and achieve the effects of improving efficiency, avoiding differences and misoperations, and unifying rules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

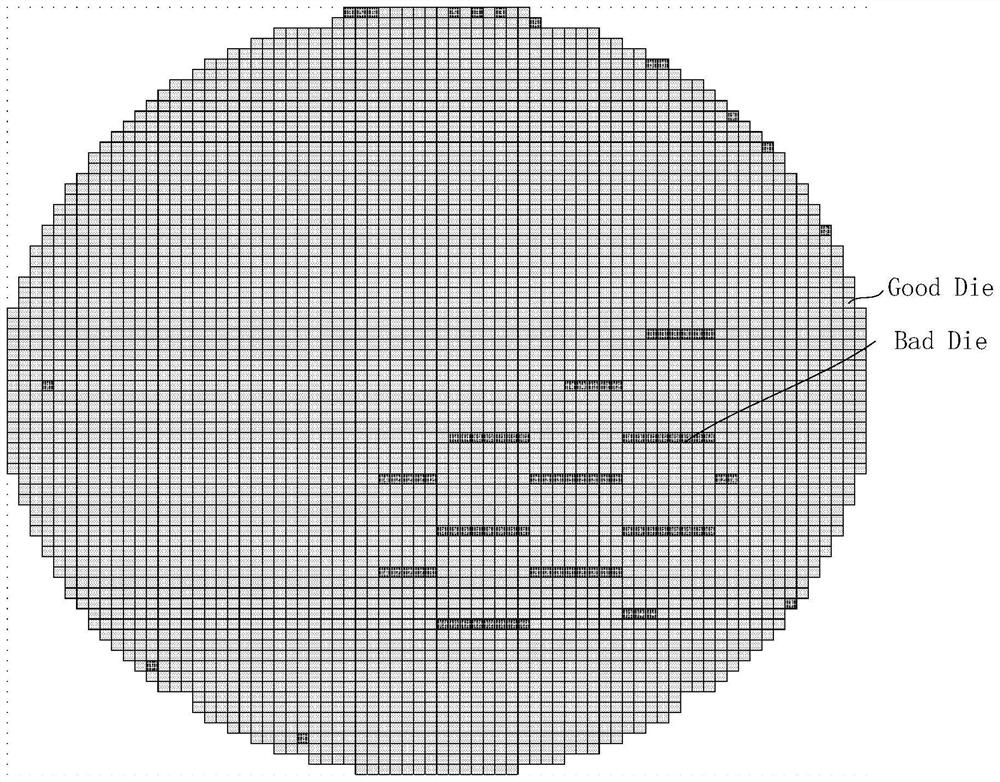

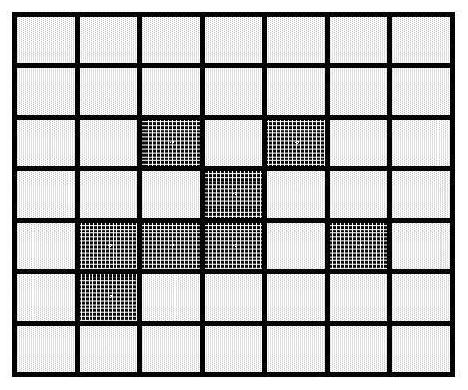

[0042] The specific embodiments of the present invention will be described in more detail below with reference to the schematic diagrams. The advantages and features of the present invention will become more apparent from the following description. It should be noted that, the accompanying drawings are all in a very simplified form and in inaccurate scales, and are only used to facilitate and clearly assist the purpose of explaining the embodiments of the present invention.

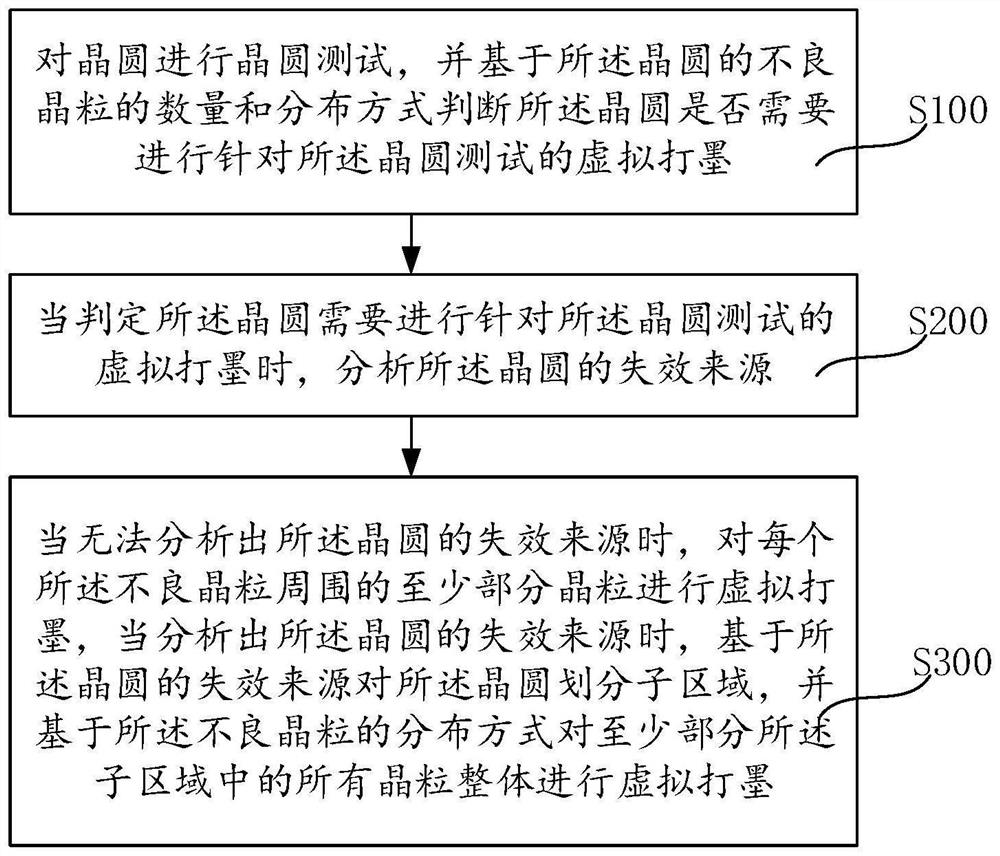

[0043] figure 1 This is a flowchart of the method for virtual inking of wafers provided in this embodiment. like figure 1 As shown, the virtual inking method for a wafer provided by this embodiment includes step S100, step S200 and step S300.

[0044]Step S100 is performed to perform a wafer test on the wafer, and based on the number and distribution of defective die of the wafer, it is determined whether the wafer needs to be subjected to virtual inking for the wafer test.

[0045] in particular, f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com