Method for forming copper layer on semiconductor chip

A chip and copper layer technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as expensive, unreliable, time-consuming, etc., to optimize productivity, reduce utilization rate, improve performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

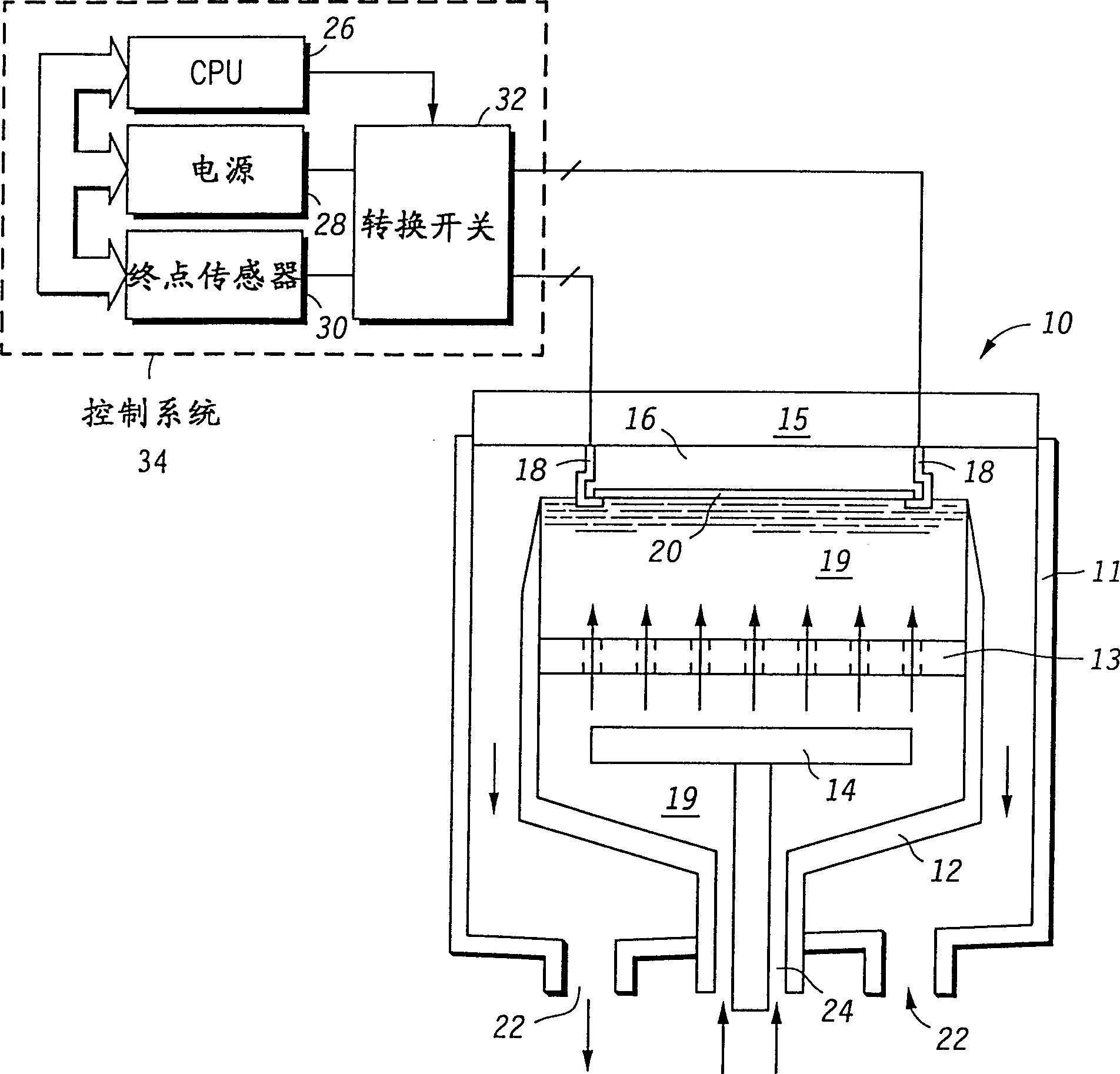

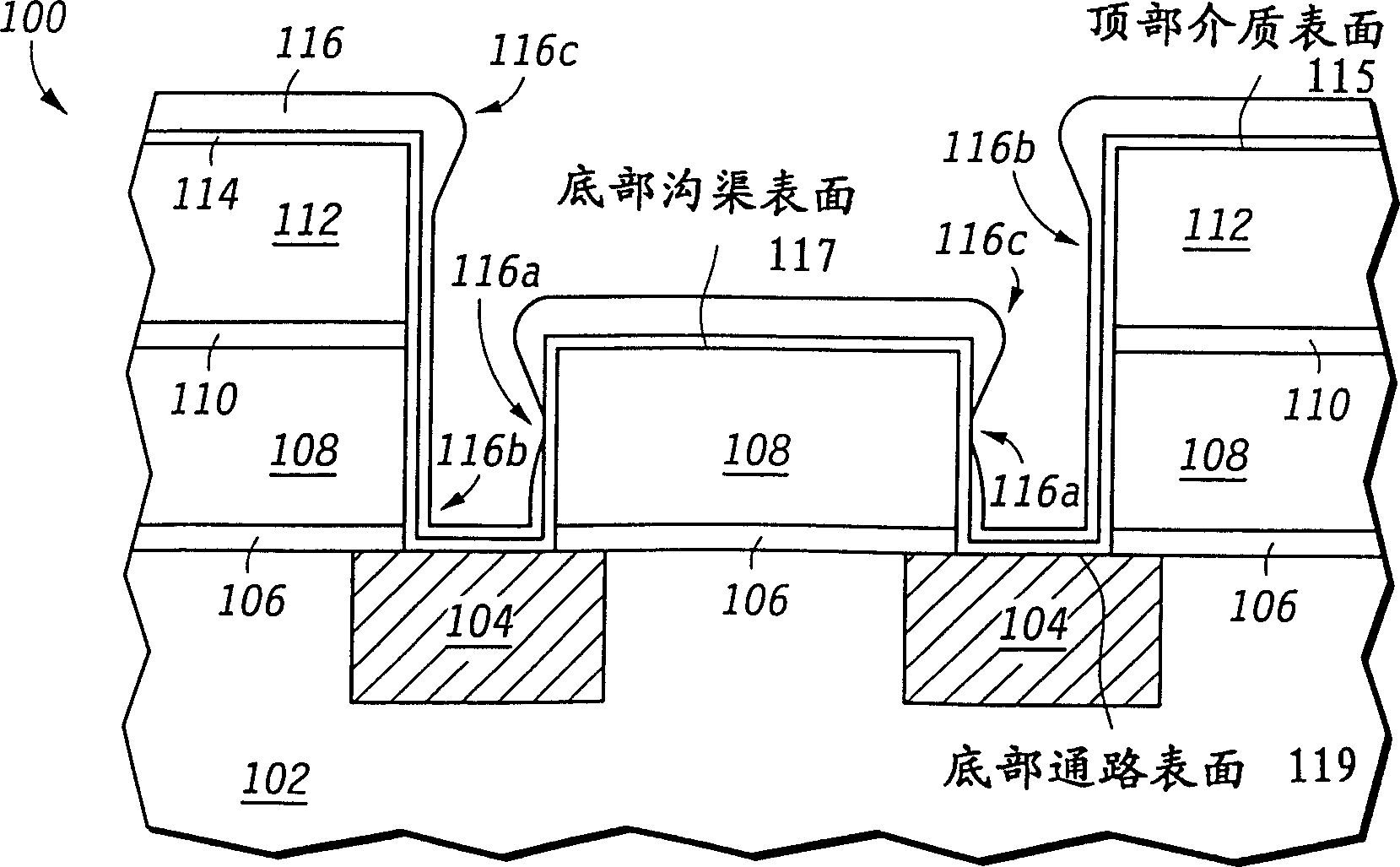

[0021] In general, the present invention is a method and apparatus for controlling the cathode and / or anode of a copper electroplating chamber to improve the quality of copper (Cu or Cu alloy) interconnects formed on semiconductor wafers through copper electroplating operations. It has been found that various pulsed positive and / or negative current waveform sequences with various optional direct current (DC) bias cycle inclusions can have significant effects on copper uniformity, copper resistance to electromigration (EM), plating productivity, One or more of copper voiding, copper grain structure, and / or similar properties can adversely affect the aforementioned various optional DC bias cycles applied to the cathode and / or anode of the copper electroplating chamber.

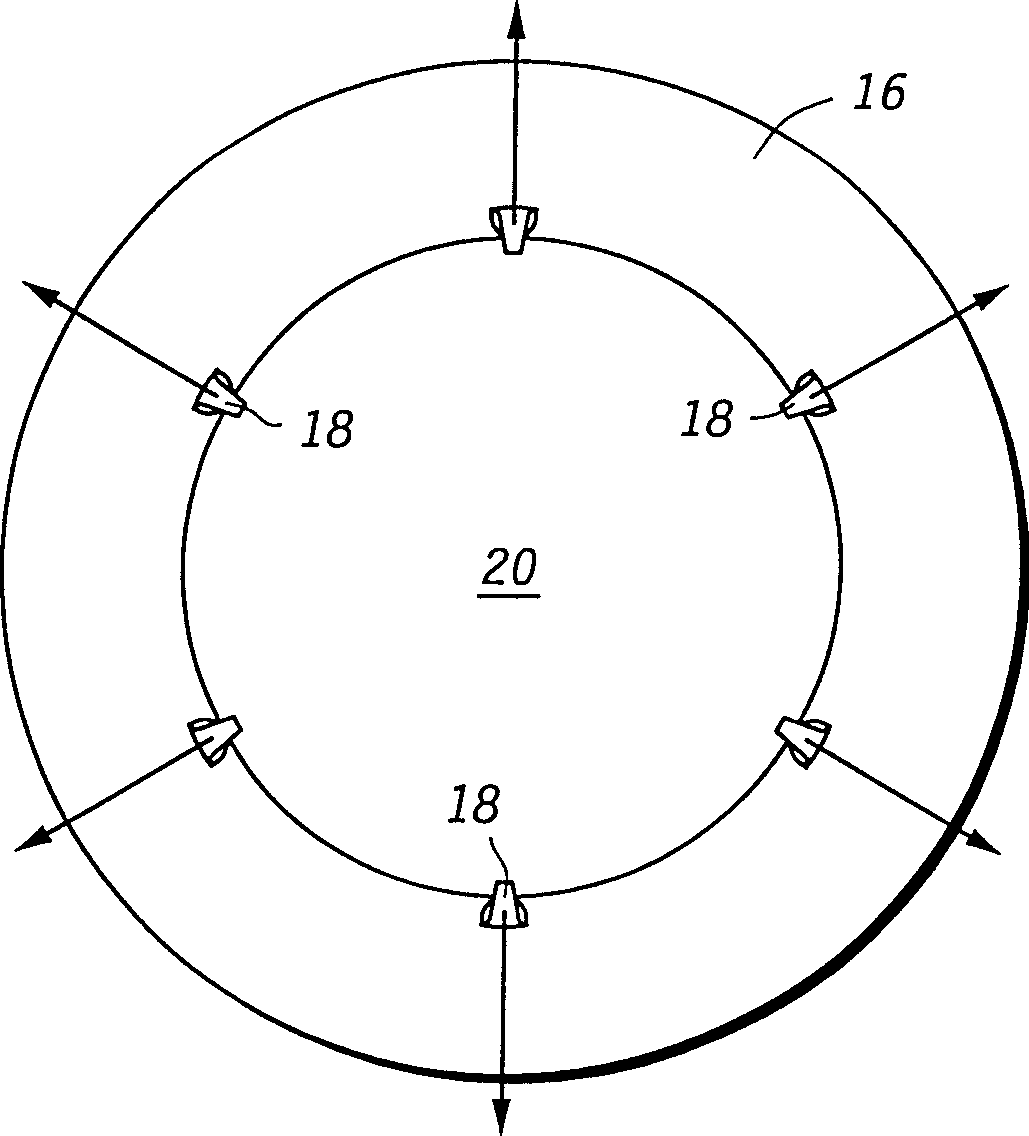

[0022] The improved copper electroplating method taught herein is by specific reference to Figure 1-13 can be better understood.

[0023] figure 1 A cross-sectional view of an electroplating system or chamber...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More