32-bit embedded microprocessor adopting double instruction set

A microprocessor and embedded technology, applied in the direction of concurrent instruction execution, machine execution device, etc., can solve the problems of slow execution speed and unrealistic, and achieve the effect of improving efficiency, increasing area and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be described in further detail below in conjunction with the accompanying drawings.

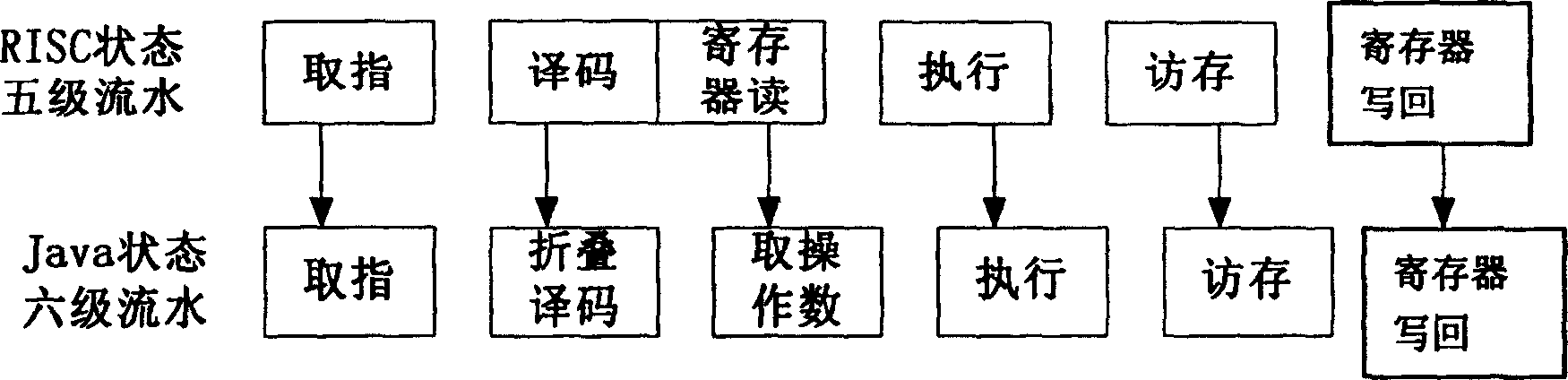

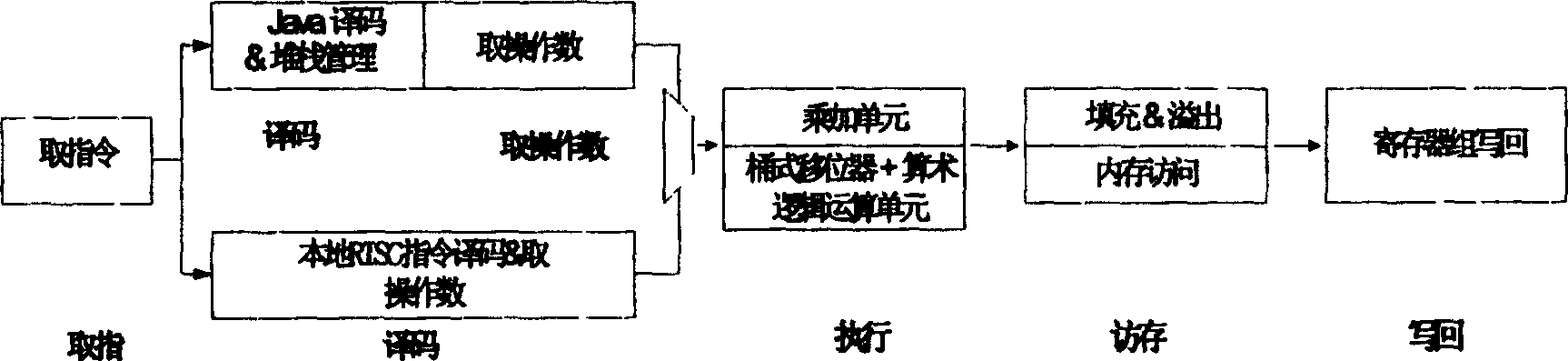

[0034] For the five-stage pipeline structure of RISC state and the six-stage pipeline structure of Java state, see figure 1 and figure 2 shown. in:

[0035] IF (fetch instruction), take the instruction out of the instruction memory and lock it in the latch of the IF / ID stage. The RISC state has the same function as the Java state;

[0036] ID (instruction decoding), in the RISC state, the instruction latched in the IF / ID stage is taken out for decoding, and the control signal of the subsequent stage is generated, and all control signals are locked in the latch of the ID / EXE stage, from Read the operands in the register file; in the Java state, perform instruction length interception, instruction folding, and instruction decoding to generate control signals in the subsequent stages. All control signals are locked in the latches of the ID / OF stage, and at ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More