Dummy error addition circuit

An error, emulation technique for electrical components, error prevention, transmission modification based on link quality, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The simulation error adding circuit of the present invention will be described below according to an embodiment.

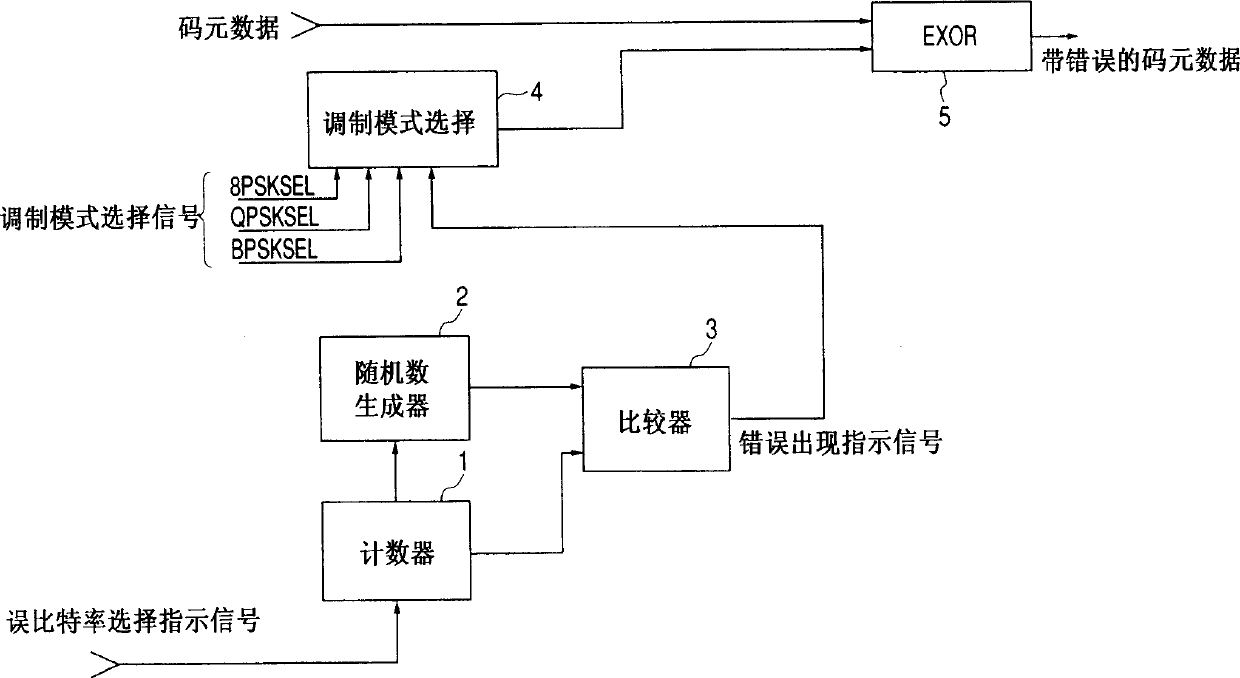

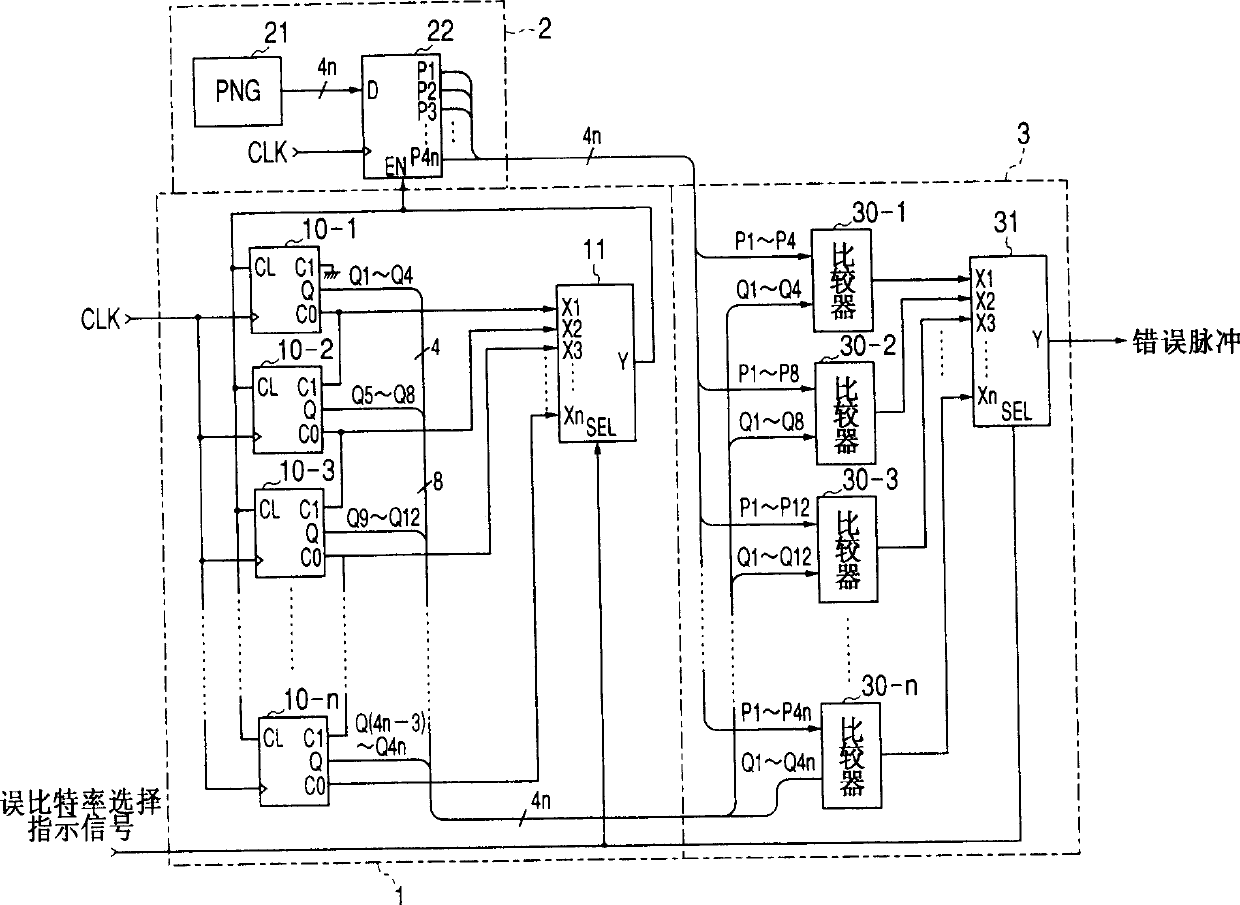

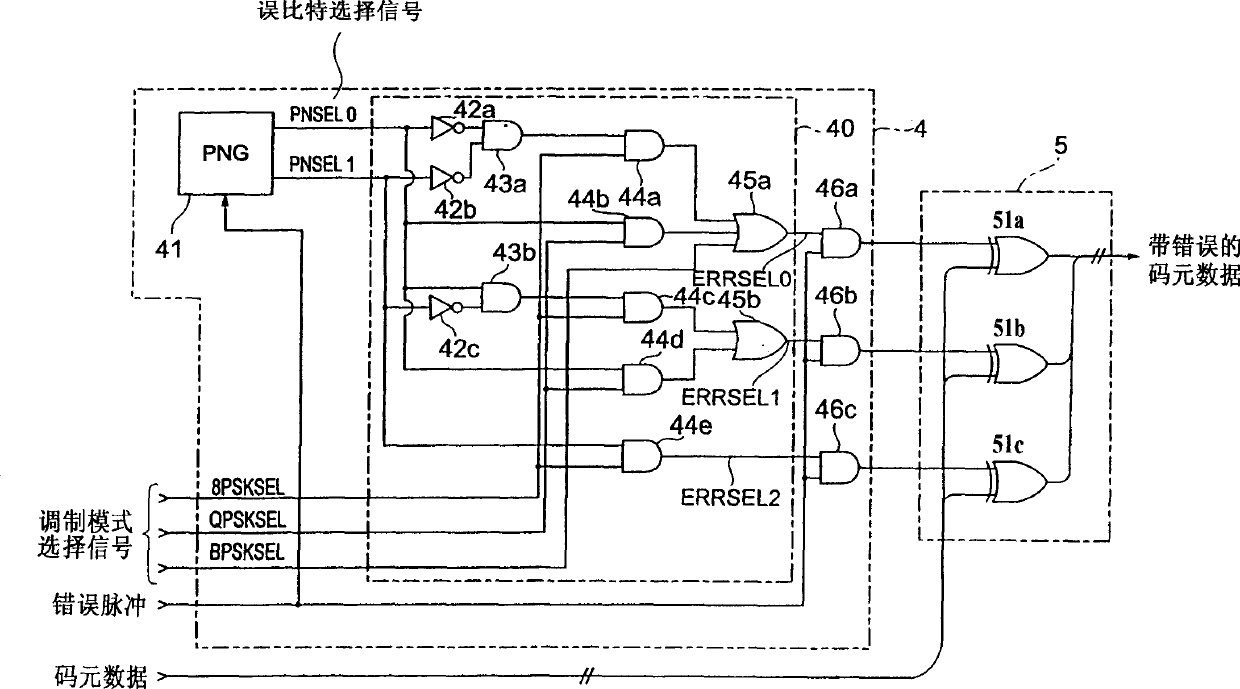

[0018] 1 is a block diagram showing the structure of a simulation error addition circuit according to an embodiment of the present invention, and is configured to correspond to 8PSK modulated by quadrature phase shift keying (PSK) according to an embodiment of the present invention. modulation, QPSK modulation and BPSK modulation as examples to illustrate.

[0019] The purpose of the artificial error adding circuit according to the embodiment of the present invention is to take PSK modulation symbol data as an object, and output modulation symbols randomly added with artificial errors. In digital broadcasting employing the above-mentioned hierarchical transmission system, an error correction code as an outer code is added to and interleaved with information signals for broadcasting such as voice signals and data signals, and a convolutional code as an inner...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More