Non-synchronous first in first out controller using biedge sampling processing control signal

A control signal, processing and control technology, applied in the field of asynchronous first-in-first-out controllers, can solve problems related to setup time or hold time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

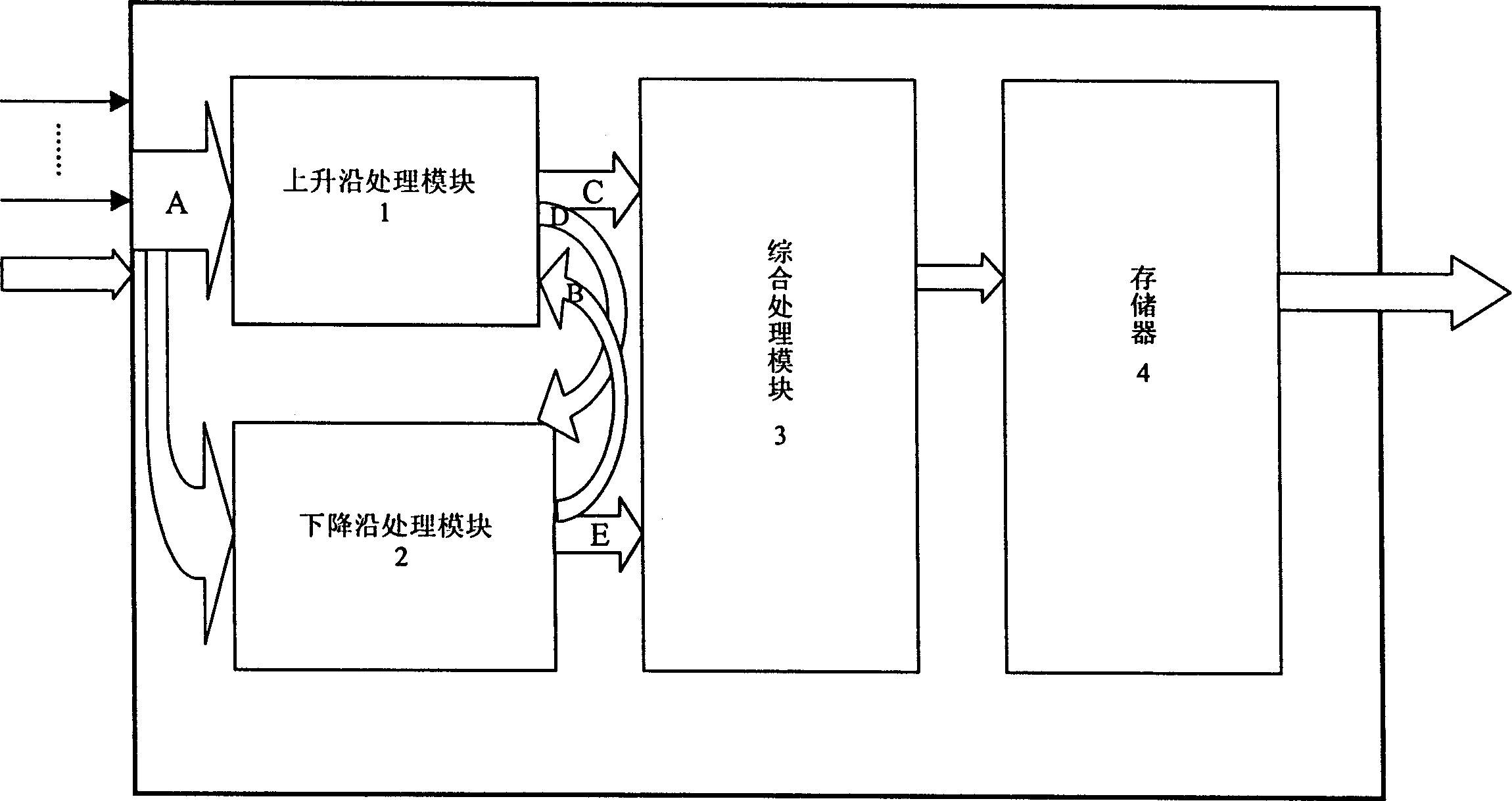

[0014] See figure 1 , shows a structural block diagram of an asynchronous FIFO controller using double-edge sampling to process control signals, which consists of a rising edge processing module 1, a falling edge processing module 2, an integrated processing module 3 and a memory 4.

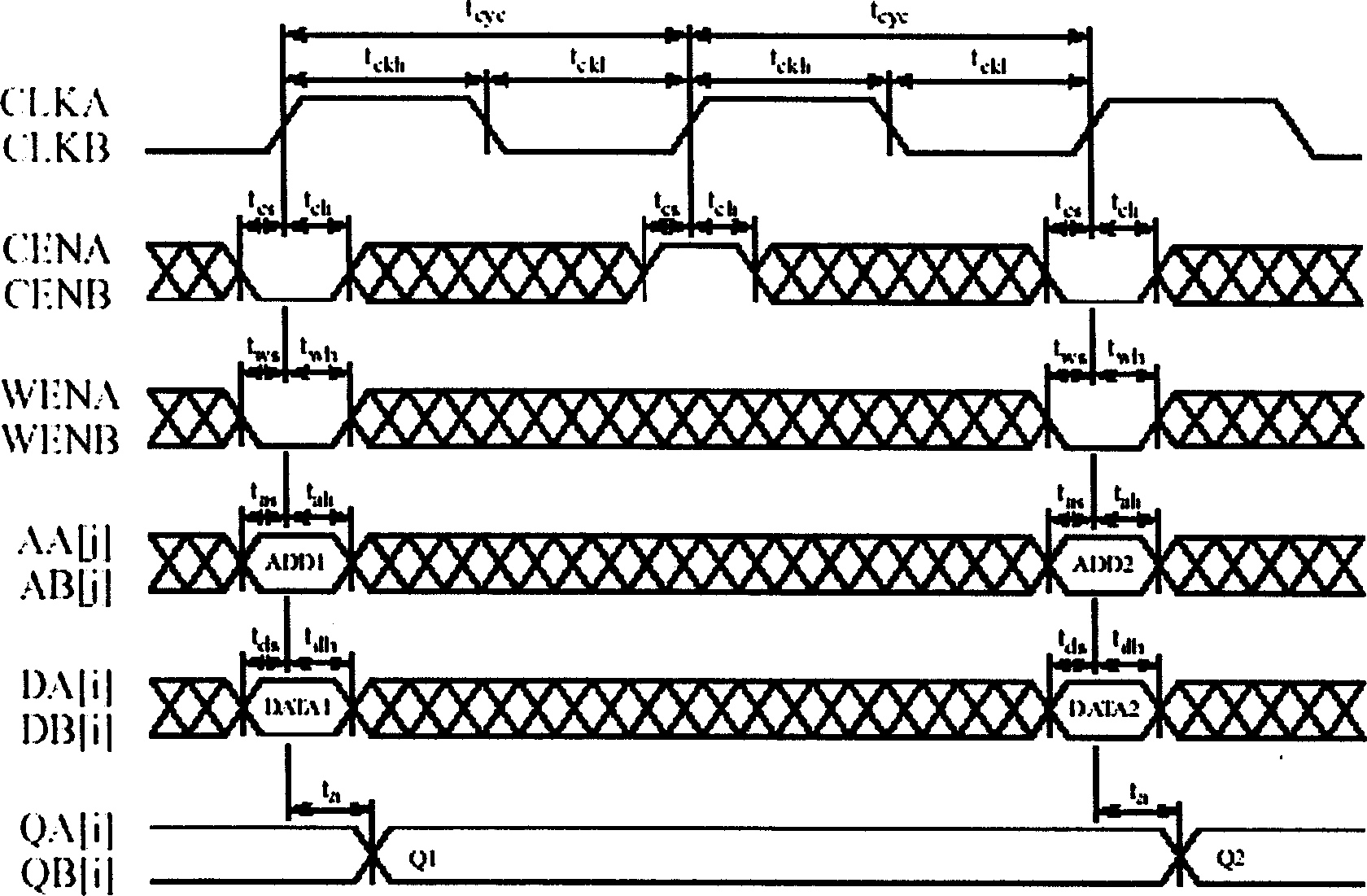

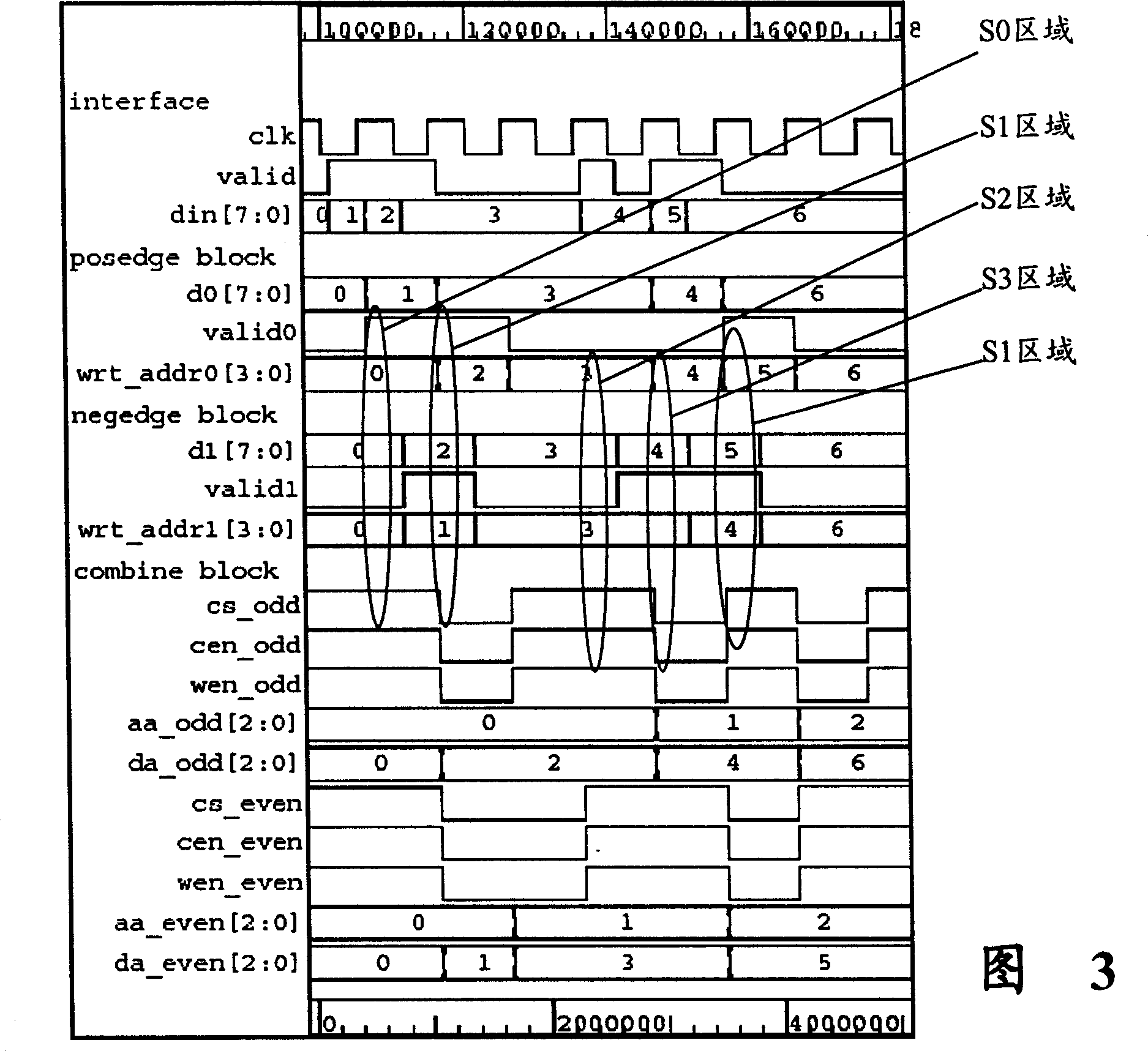

[0015] Among them, the rising edge and falling edge processing modules 1 and 2 respectively directly use the rising and falling edges of the DDR clock signal as the latch time to latch the received external control signal and data A, and then the rising edge processing module 1 will lock the The stored signal is processed with the external control signal and data latched by the falling edge processing module 2 and the address obtained after processing to obtain the output signal C of the rising edge processing module 1. The whole process of the falling edge processing module 2 is also similar, and the falling edge processing The module 2 processes the latched signal, the external control signal a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More