Memory shortage diagnostic method using failure mode as guide and its system

A failure mode and defect diagnosis technology, which is applied to the generation of response errors, error detection of redundant data in hardware, etc., can solve problems such as insufficient test algorithms and poor accuracy of diagnosis results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Generally speaking, the fault model needs to be selected as the target of error detection before executing the test algorithm. General memory fault models include: Stuck-At Fault (SAF), Transition Fault (TF), Stuck-Open Fault (SOF), Address Decoder Fault (AF) , Coupling Fault (Coupling Fault, CF) and Read Disturb Fault (Read Disturb Fault, RDF). The defects in the memory can be detected by the fault model, and the cause of the defects can be further analyzed.

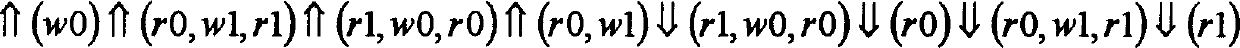

[0026] Among many test algorithms, the MARCH-based test and diagnosis algorithm is one of the easier to implement, whether it is applied to test equipment or the built-in self-test circuit of the system-on-chip is quite simple. The following calculation formula is the MARCH-17N algorithm adopted by an embodiment of the present invention.

[0027] ⇑ ( w 0 ) ⇑ ( r 0 , ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More