Patents

Literature

54 results about "Memory defects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

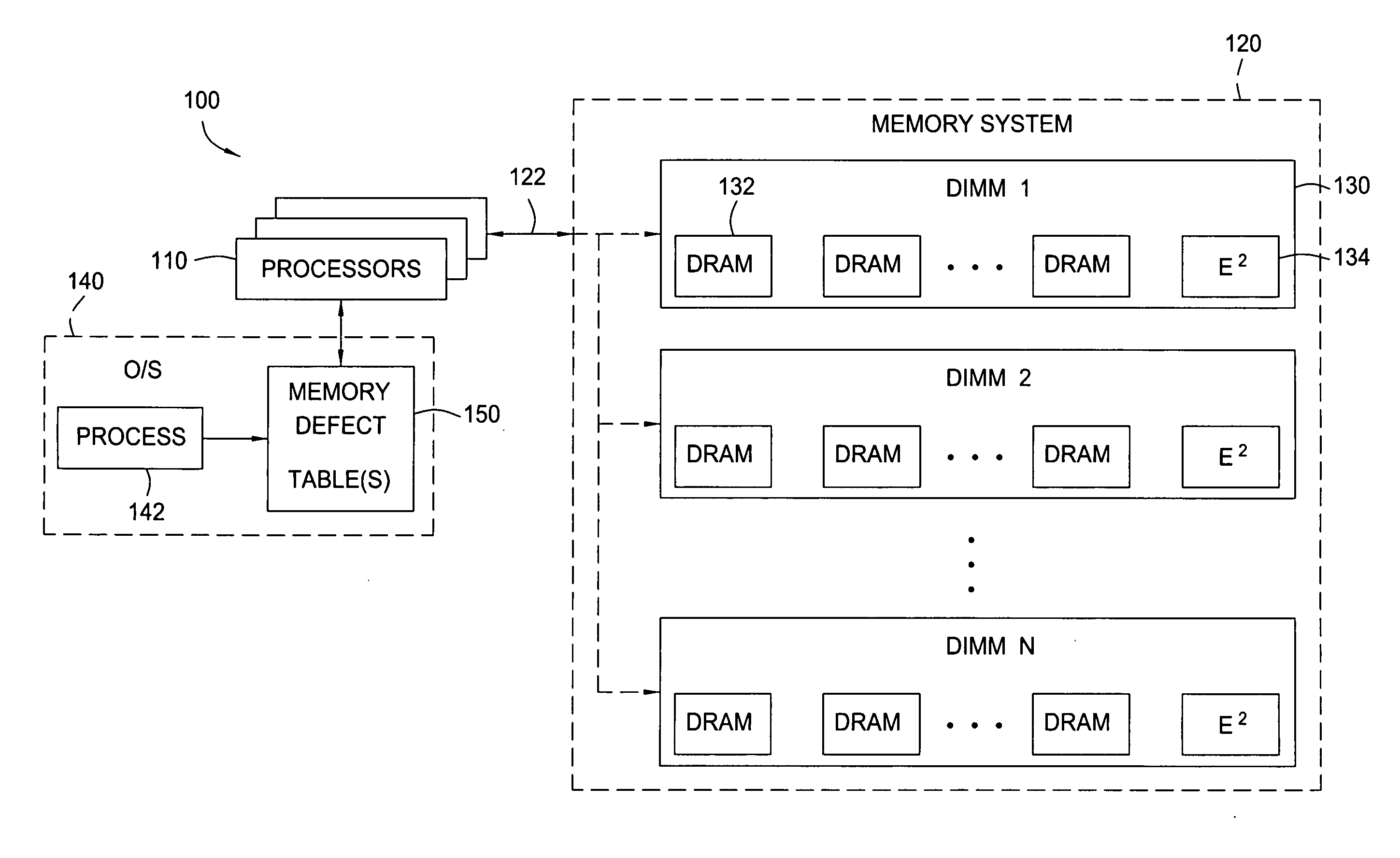

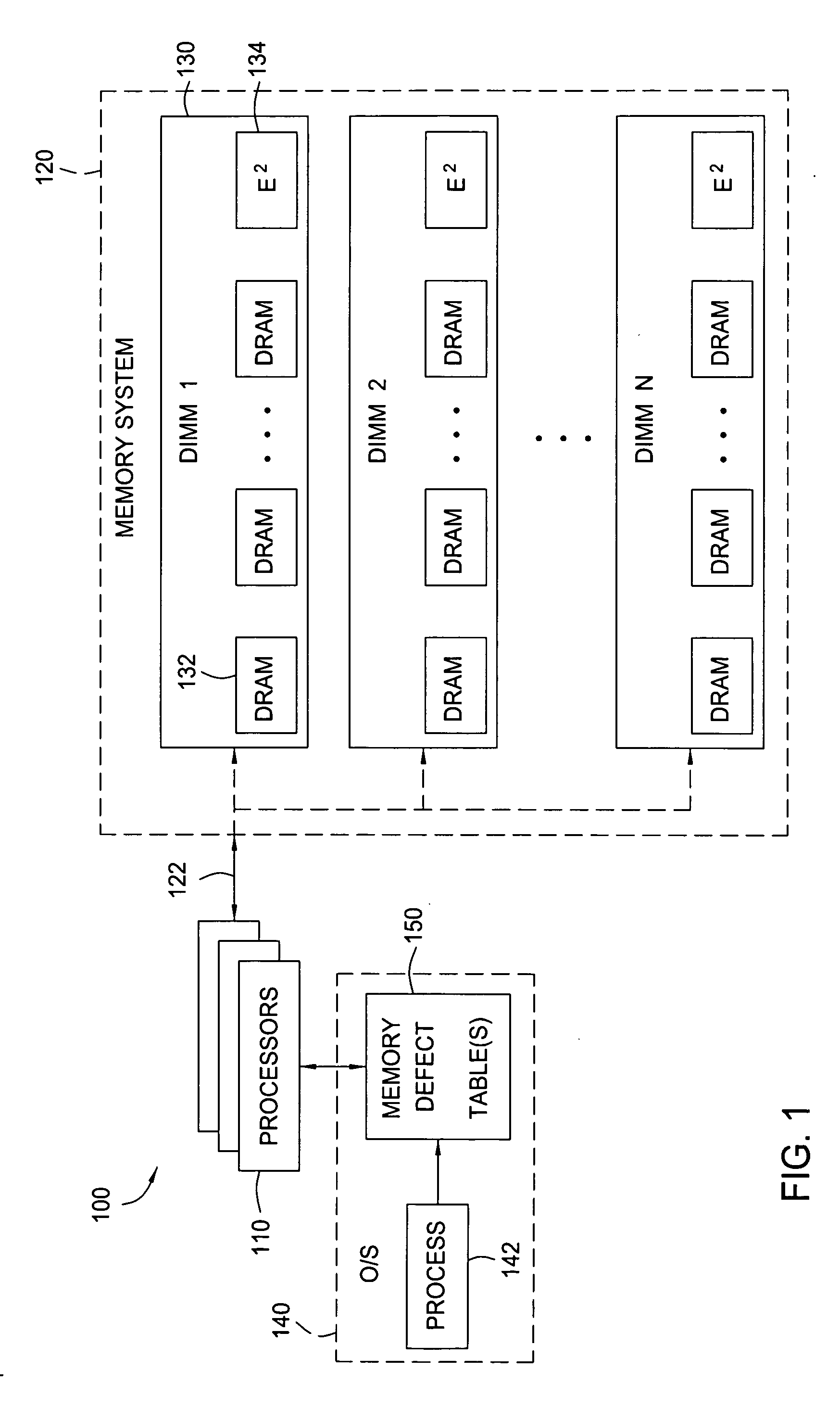

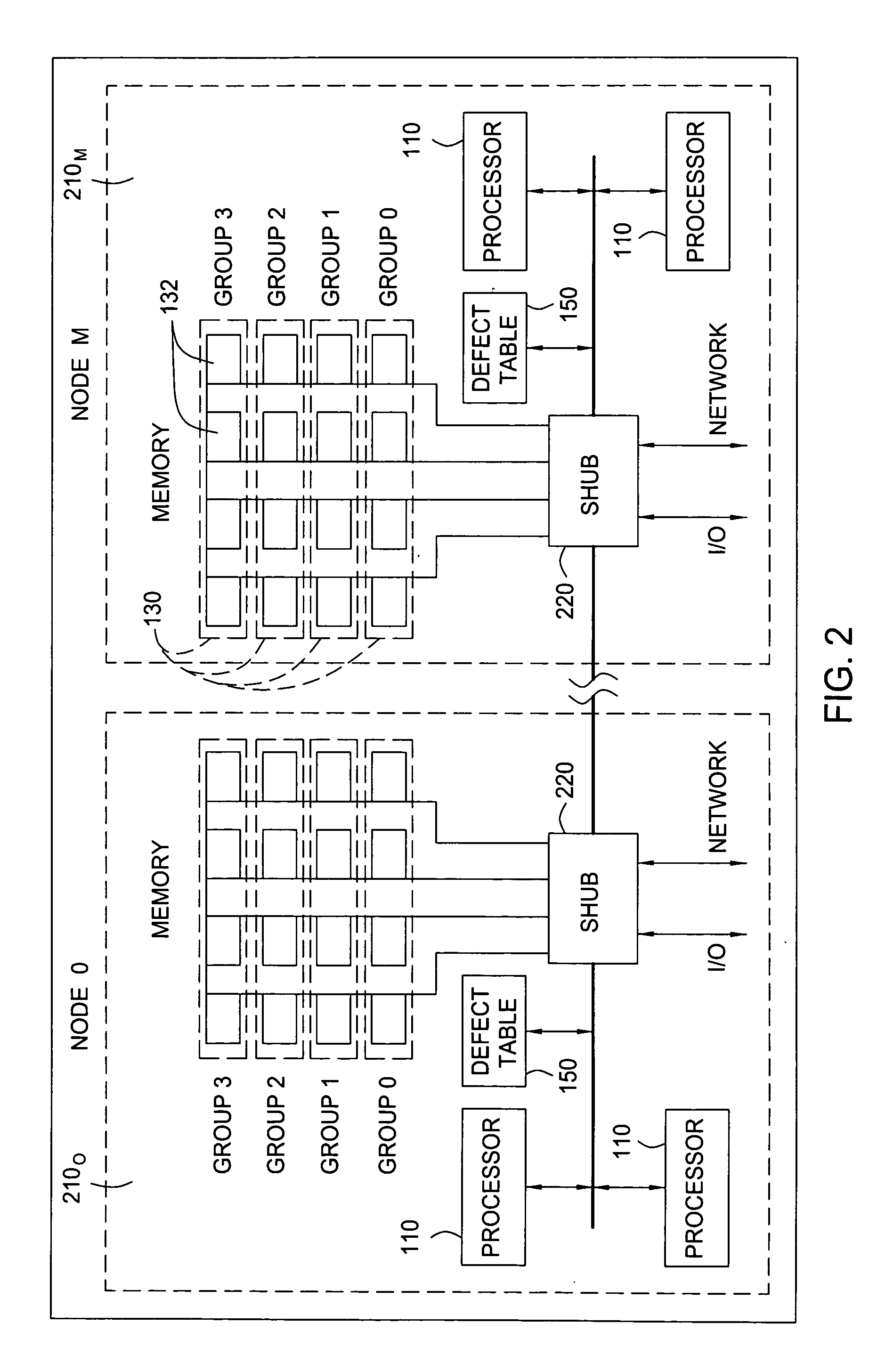

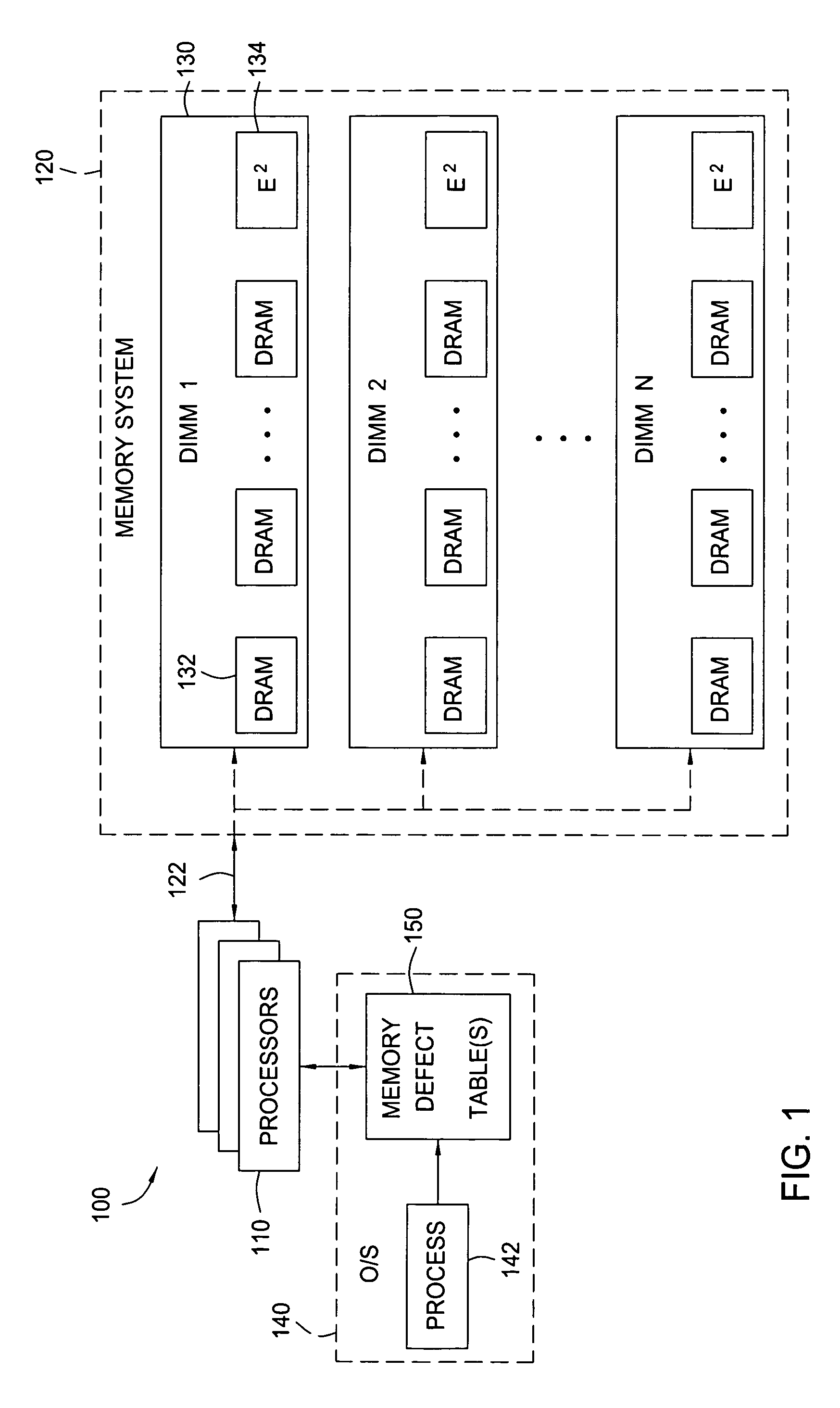

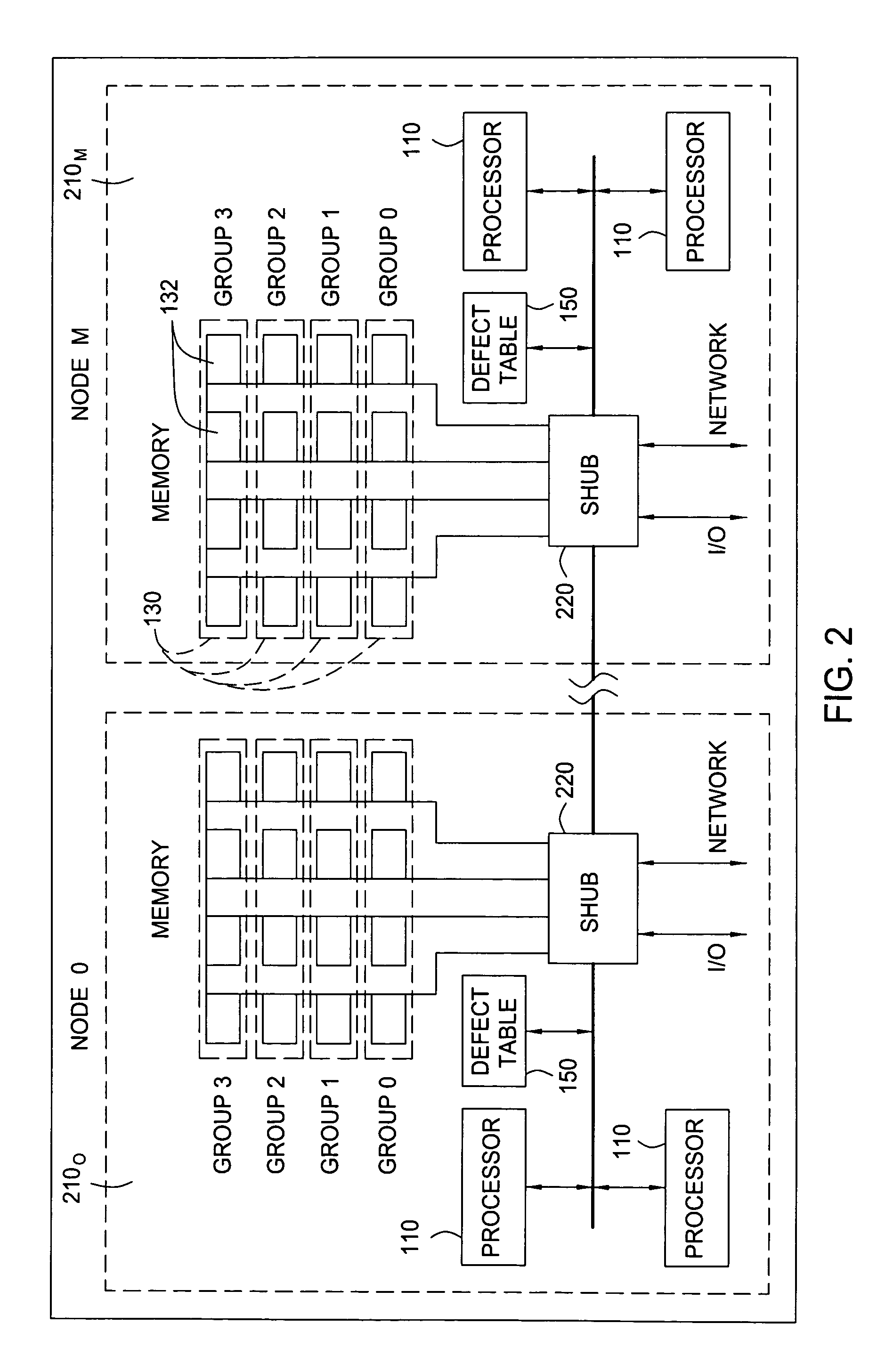

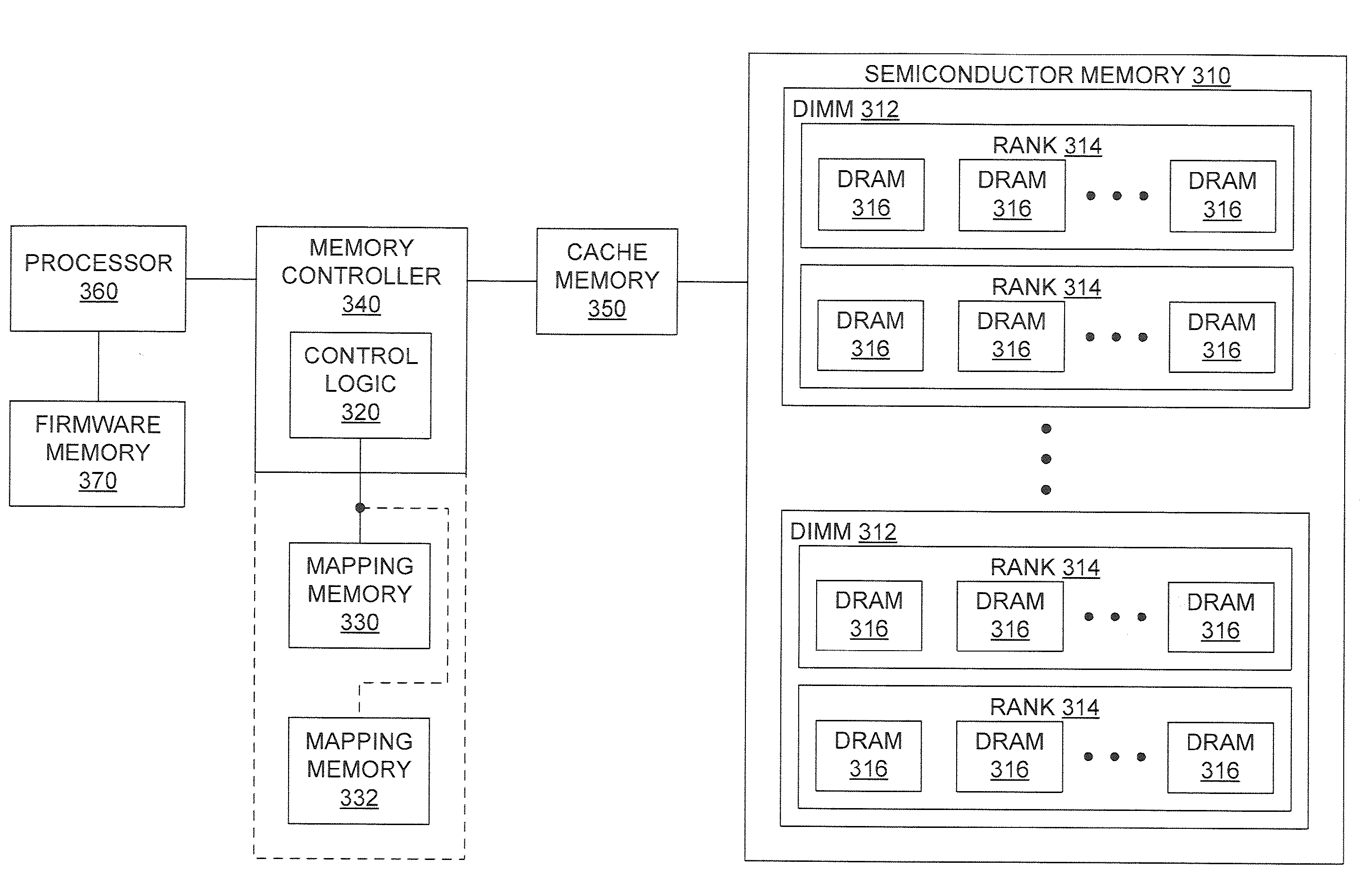

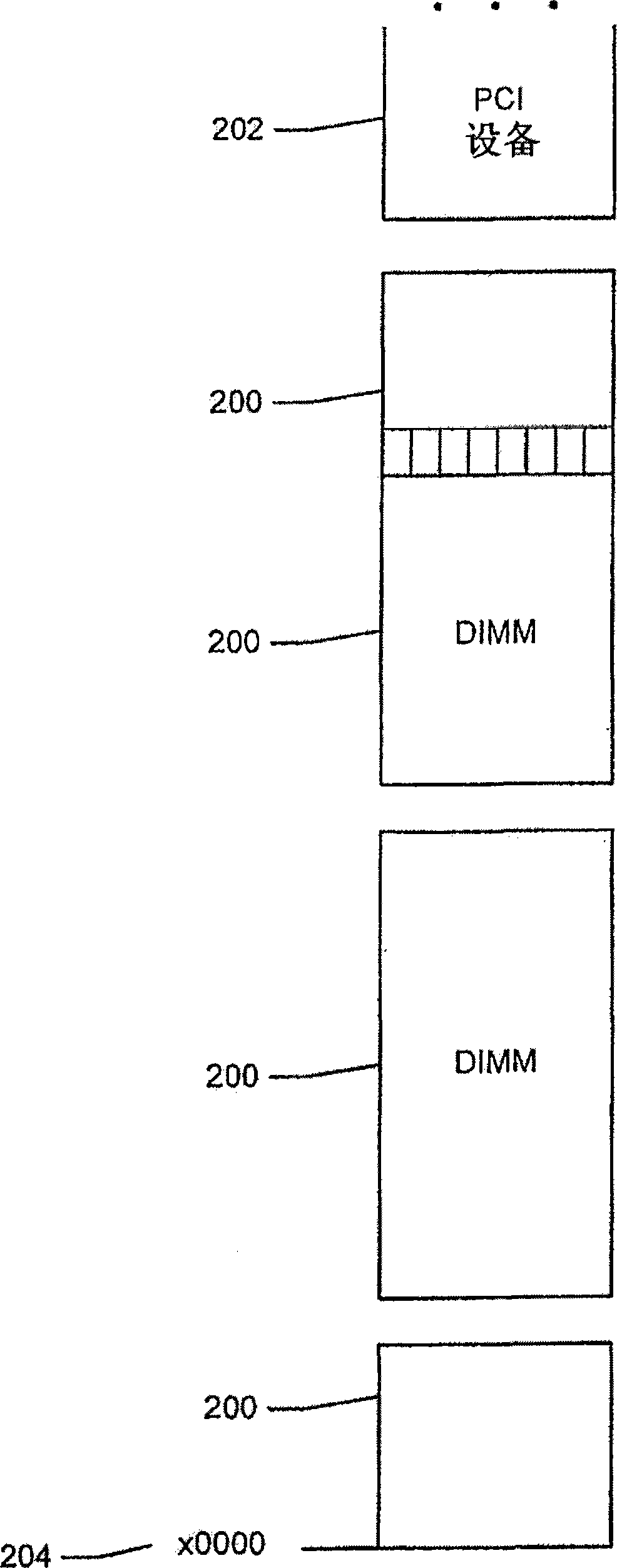

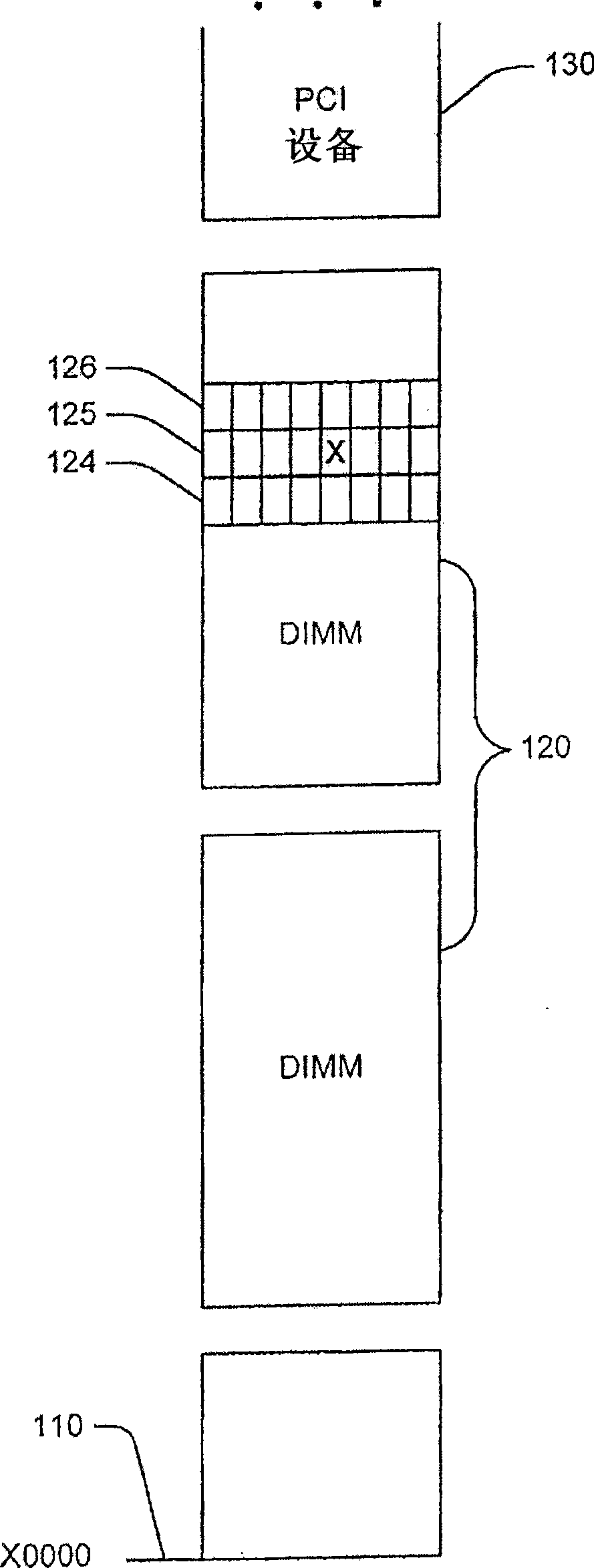

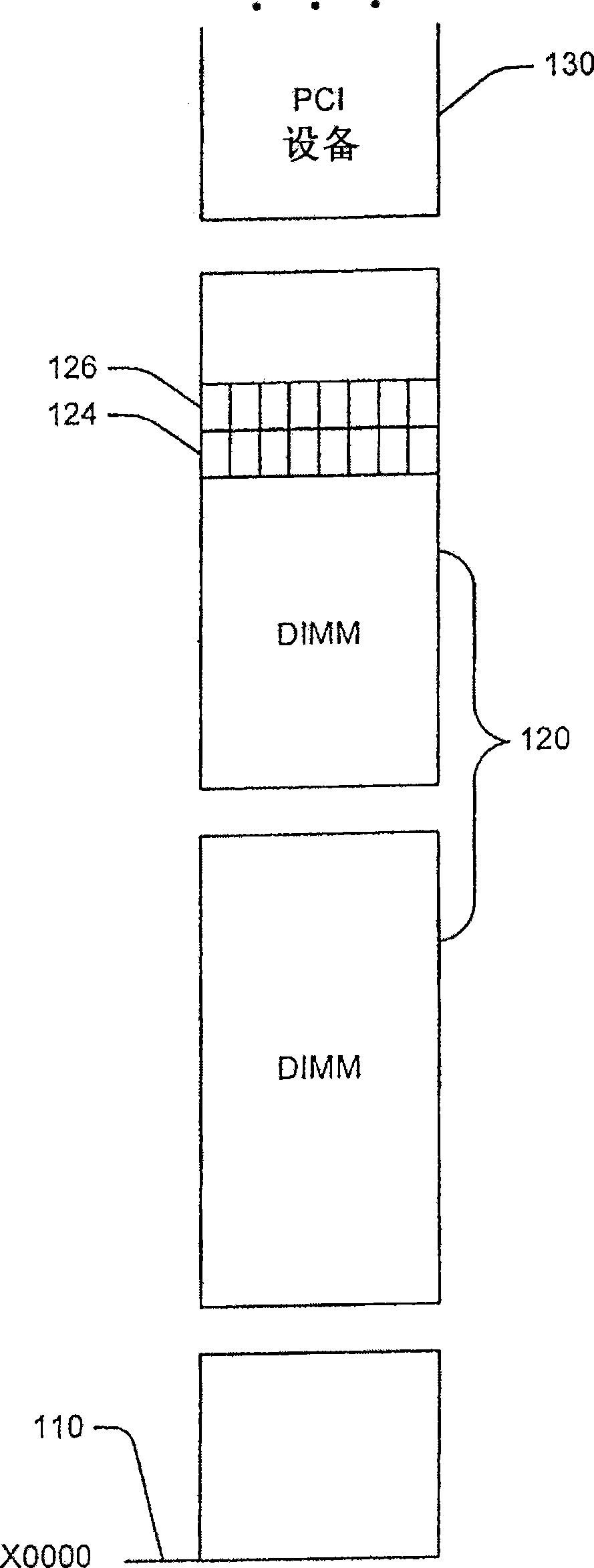

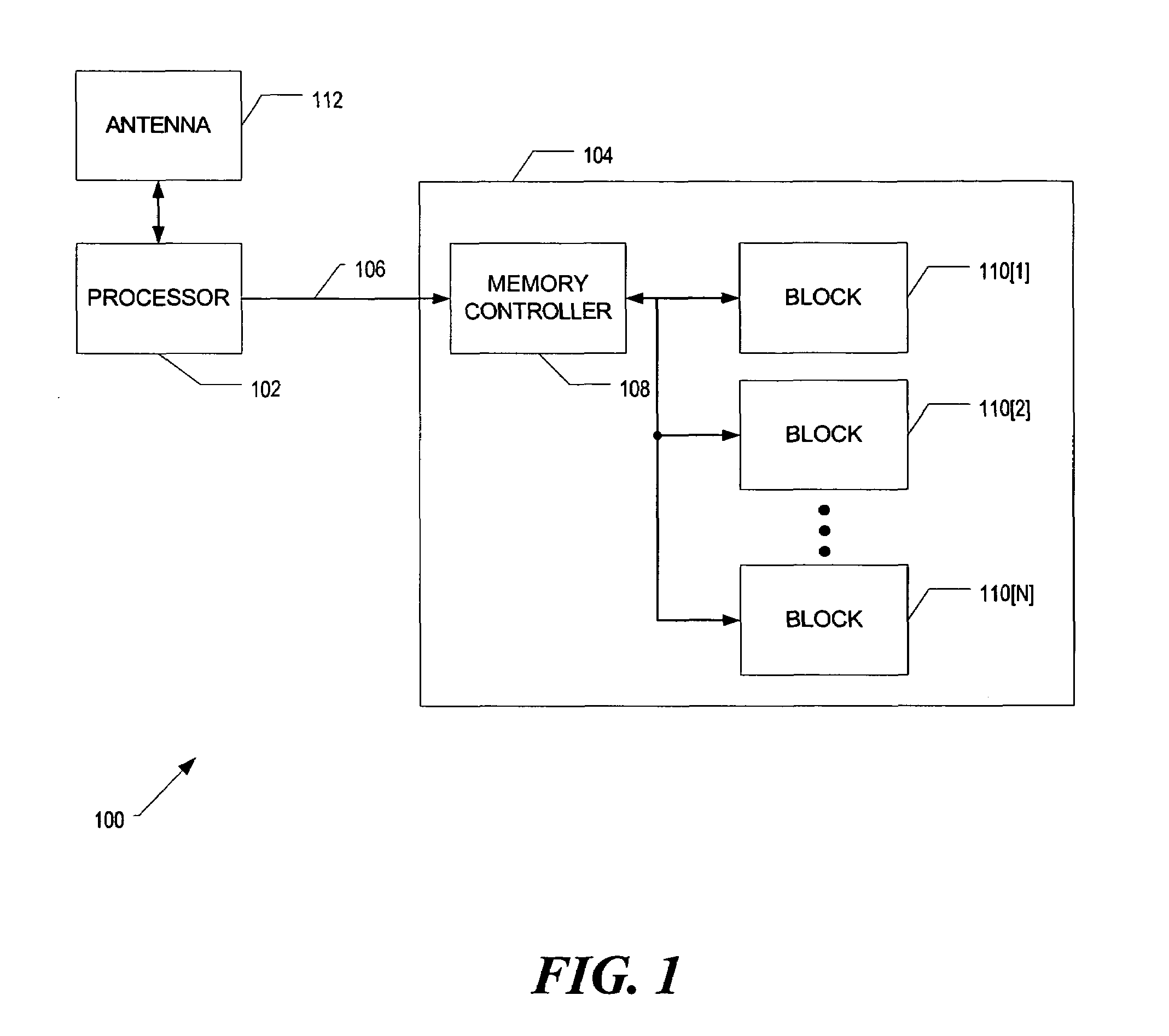

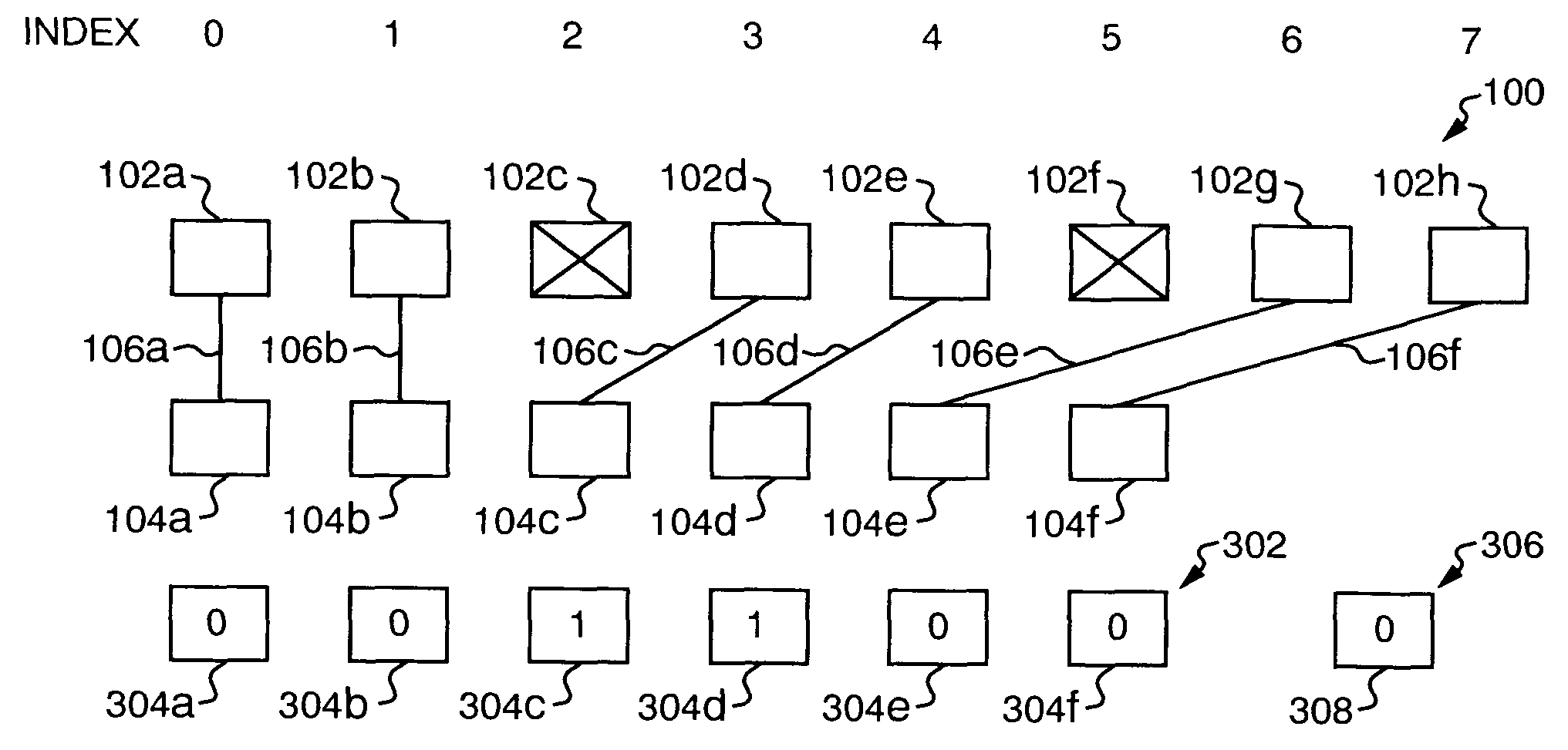

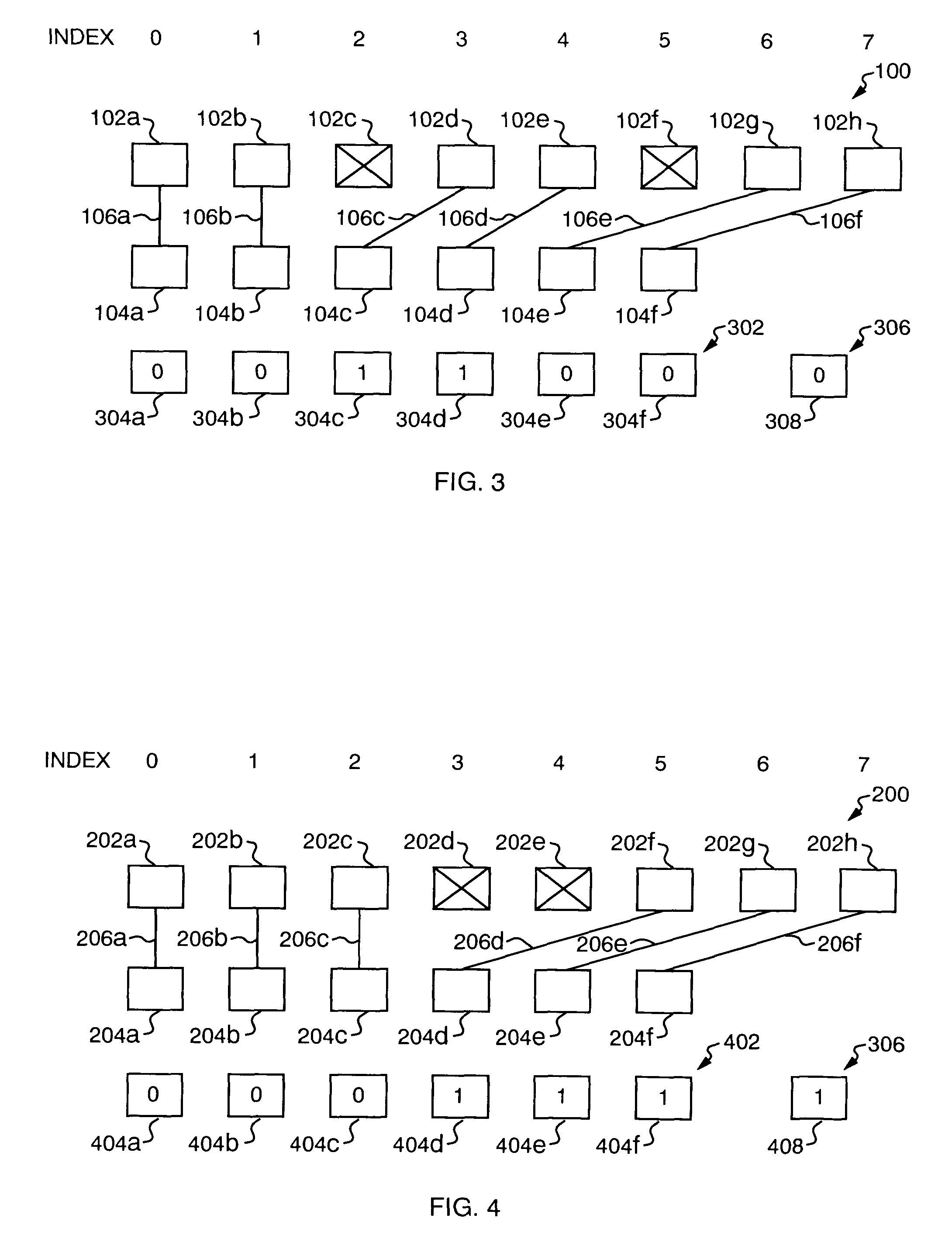

Generation and use of system level defect tables for main memory

ActiveUS20070174718A1Improve reliabilityDC motor speed/torque controlError detection/correctionParallel computingSystem level

Methods and apparatus for maintaining and utilizing system memory defect tables that store information identifying defective memory locations in memory modules. For some embodiments, the defect tables may be utilized to identify and re-map defective memory locations to non-defective replacement (spare) memory locations as an alternative to replacing an entire memory module. For some embodiments, some portion of the overall capacity of the memory module may be allocated for such replacement.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Generation and use of system level defect tables for main memory

ActiveUS7478285B2Improve reliabilityDC motor speed/torque controlError detection/correctionParallel computingSystem level

Methods and apparatus for maintaining and utilizing system memory defect tables that store information identifying defective memory locations in memory modules. For some embodiments, the defect tables may be utilized to identify and re-map defective memory locations to non-defective replacement (spare) memory locations as an alternative to replacing an entire memory module. For some embodiments, some portion of the overall capacity of the memory module may be allocated for such replacement.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

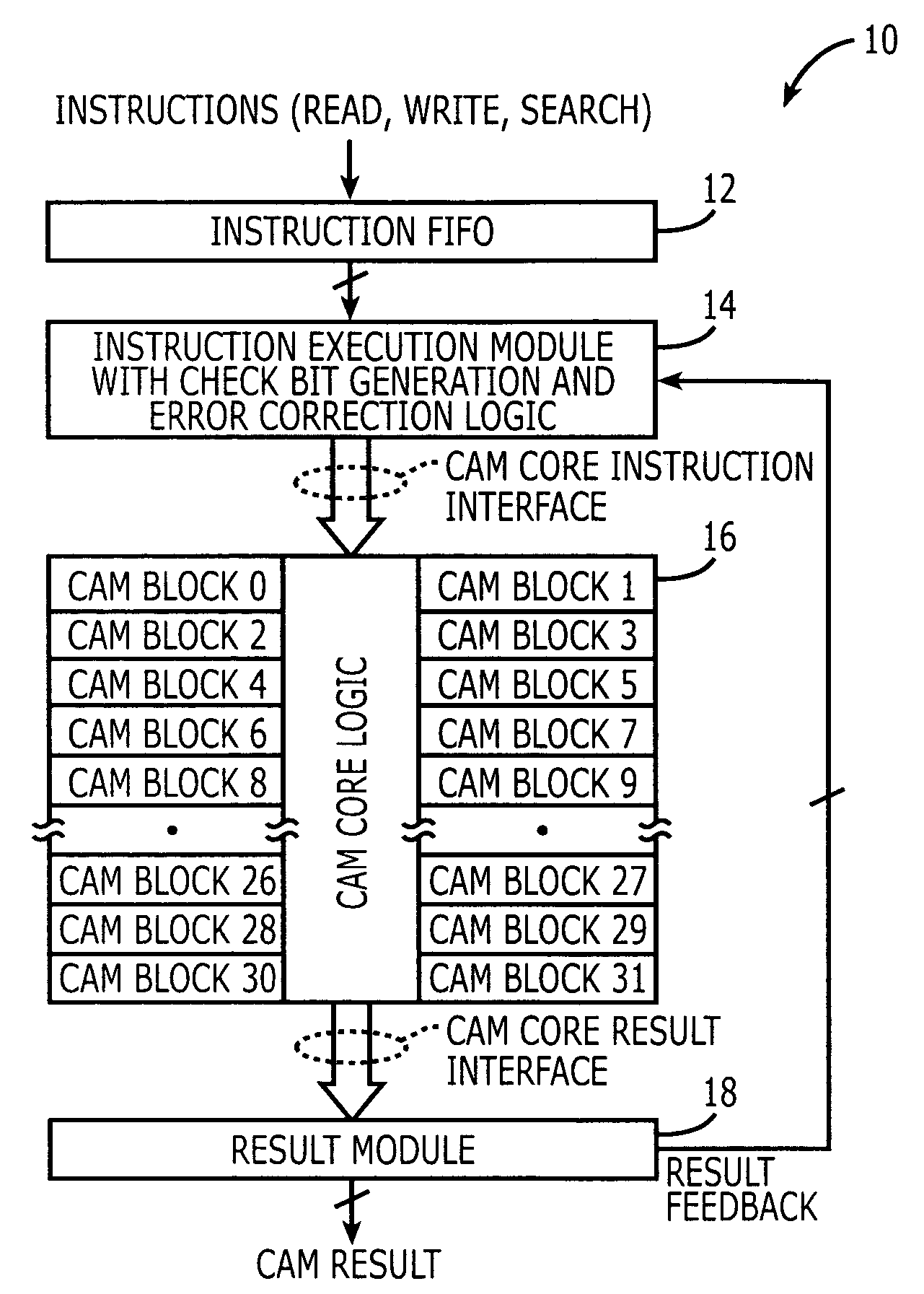

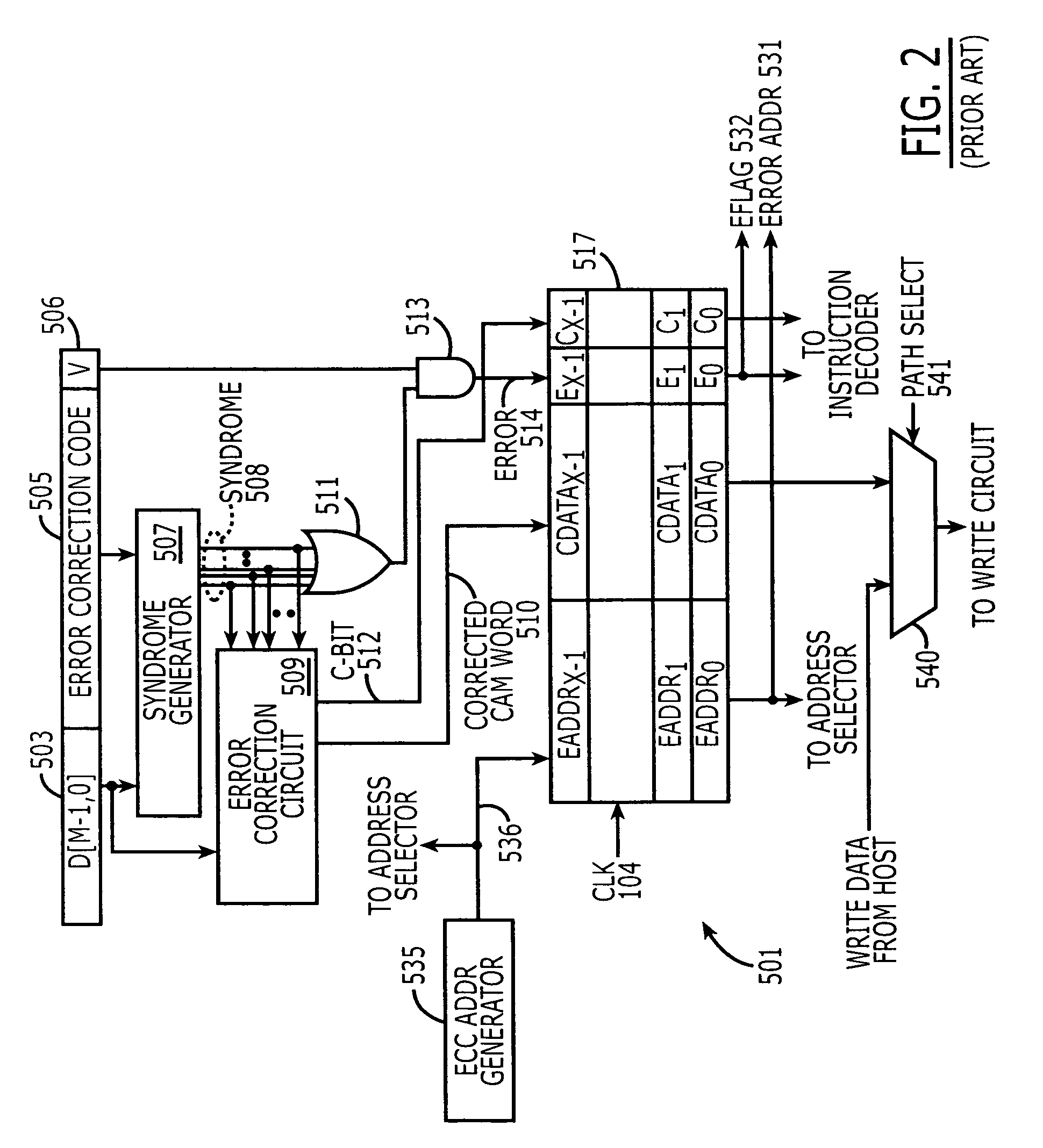

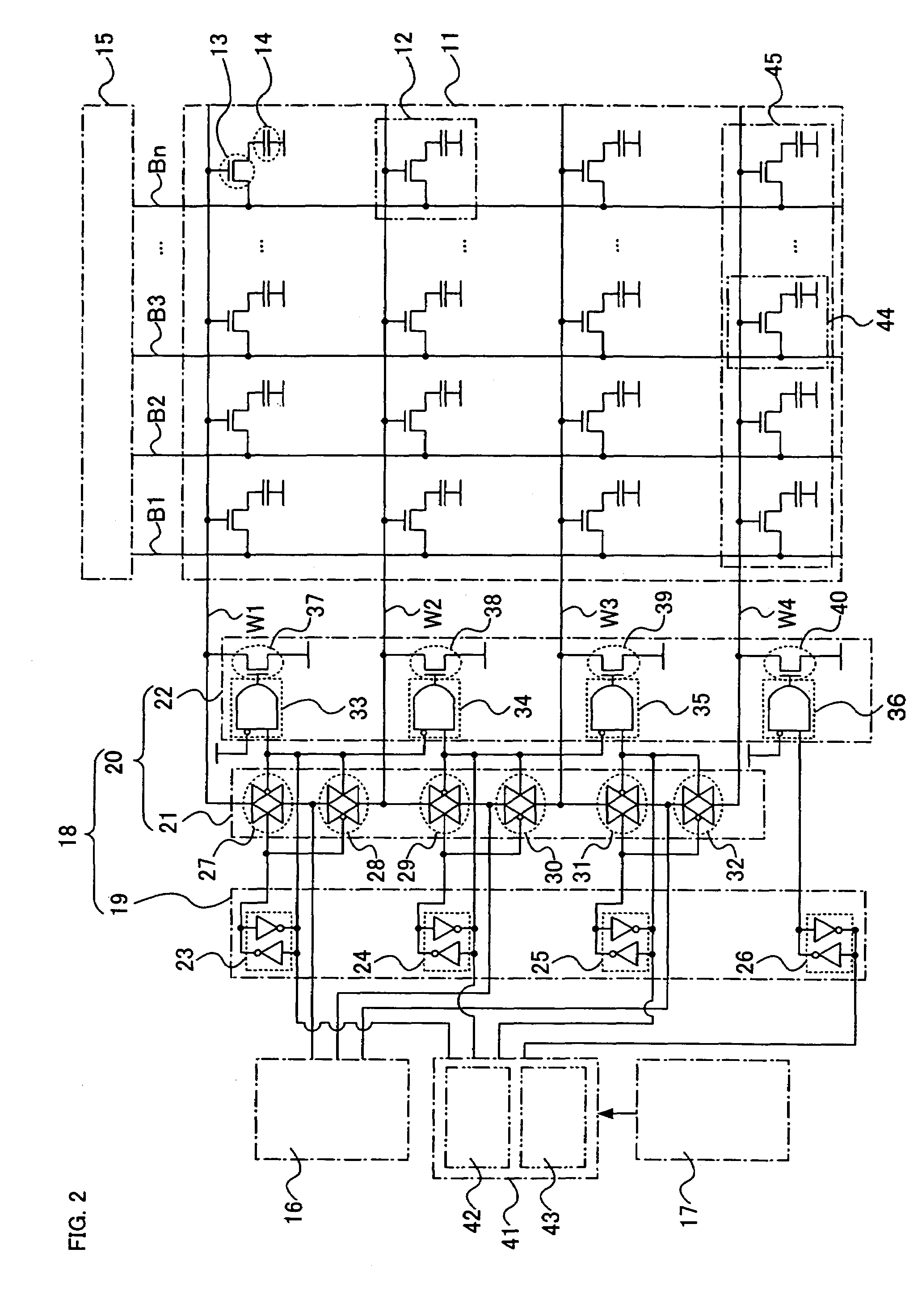

Content addressable memory (CAM) devices that support background BIST and BISR operations and methods of operating same

Search engine devices include a content addressable memory (CAM) core having a plurality of CAM array blocks therein and a control circuit. The control circuit, which is electrically coupled to the plurality of CAM array blocks, is configured to perform built-in self repair (BISR) of hard memory defects and / or compare logic defects in the plurality of CAM array blocks concurrently with operations to search entries in the plurality of CAM array blocks.

Owner:AVAGO TECH INT SALES PTE LTD

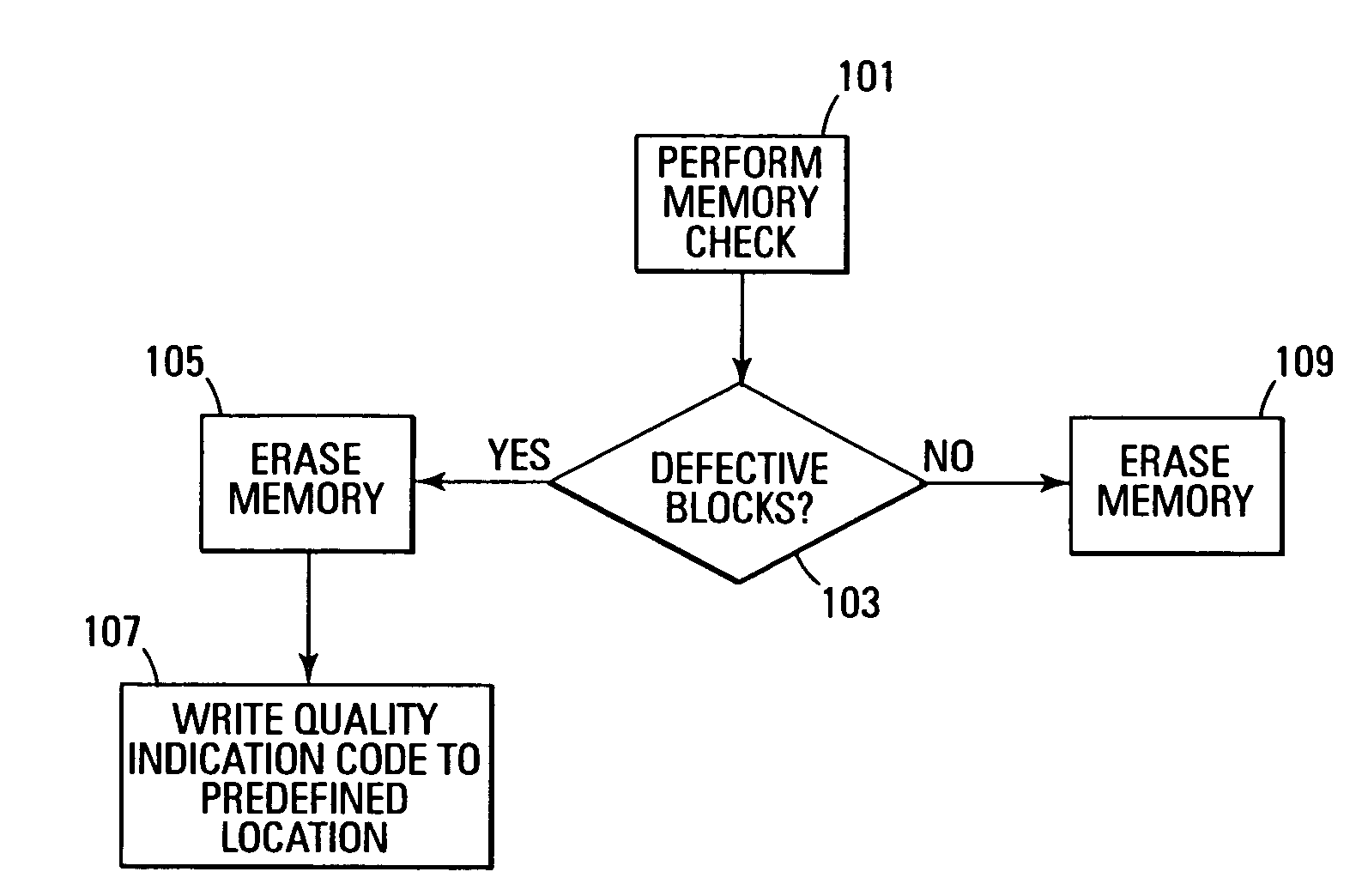

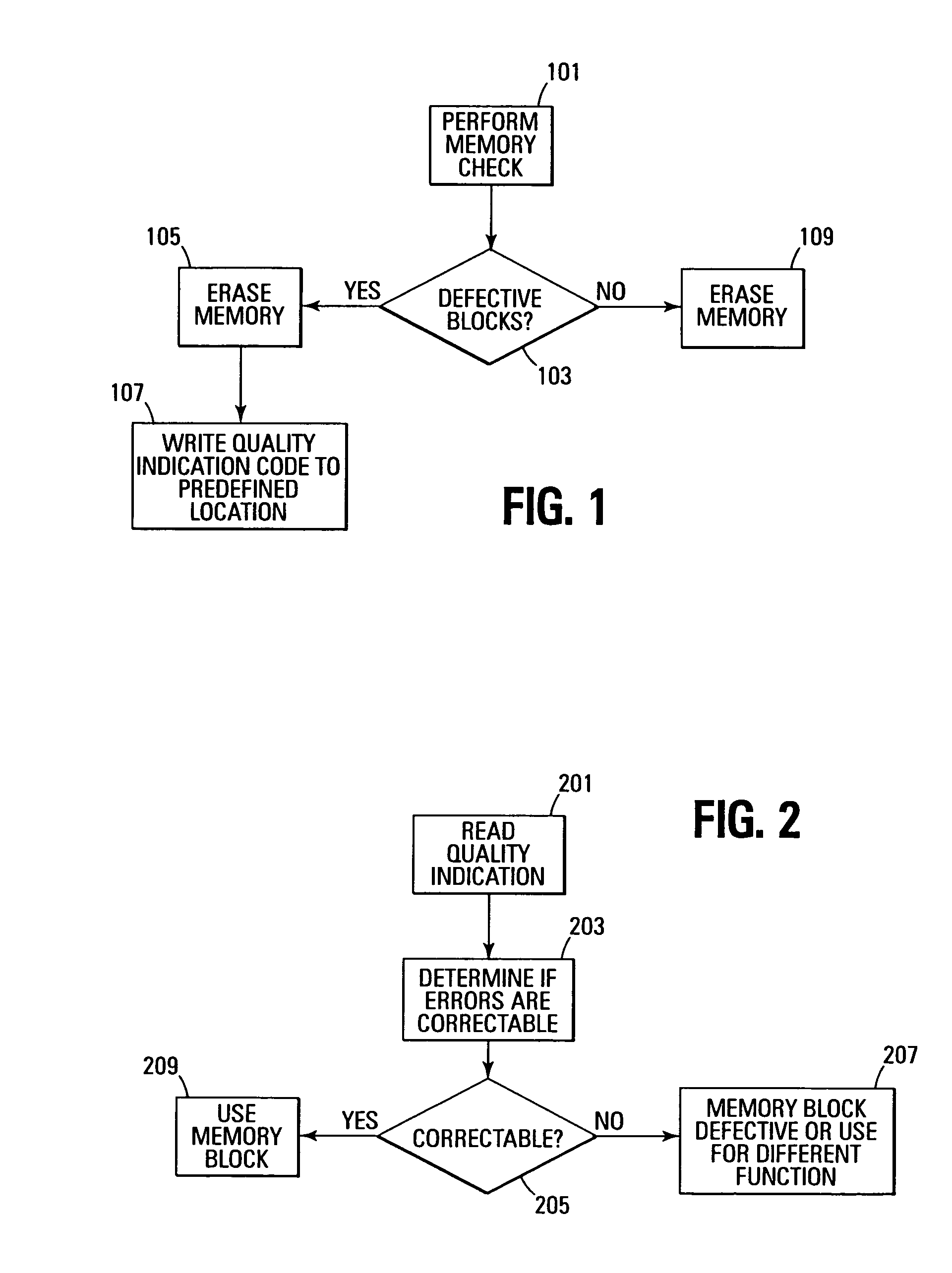

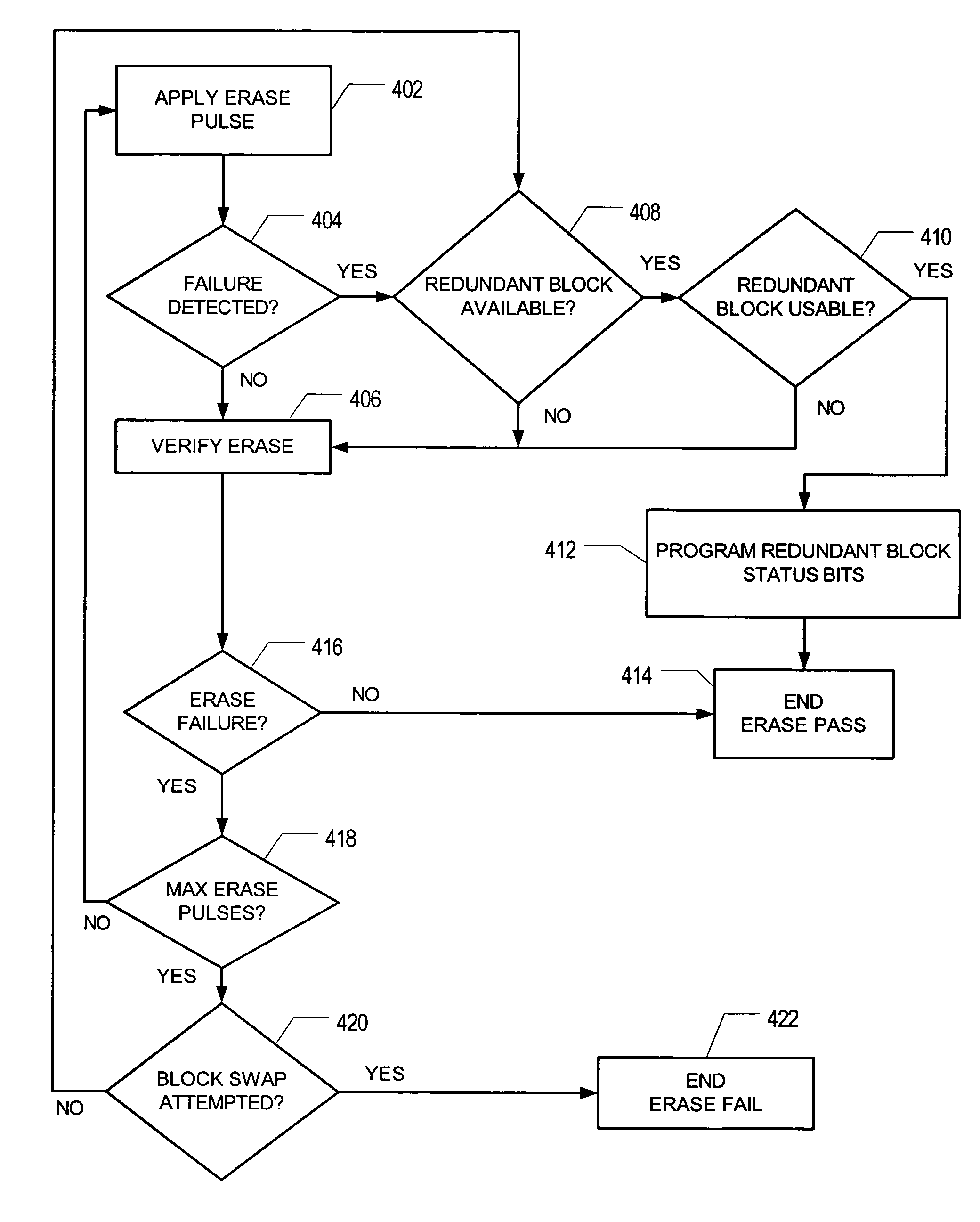

Memory block quality identification in a memory device

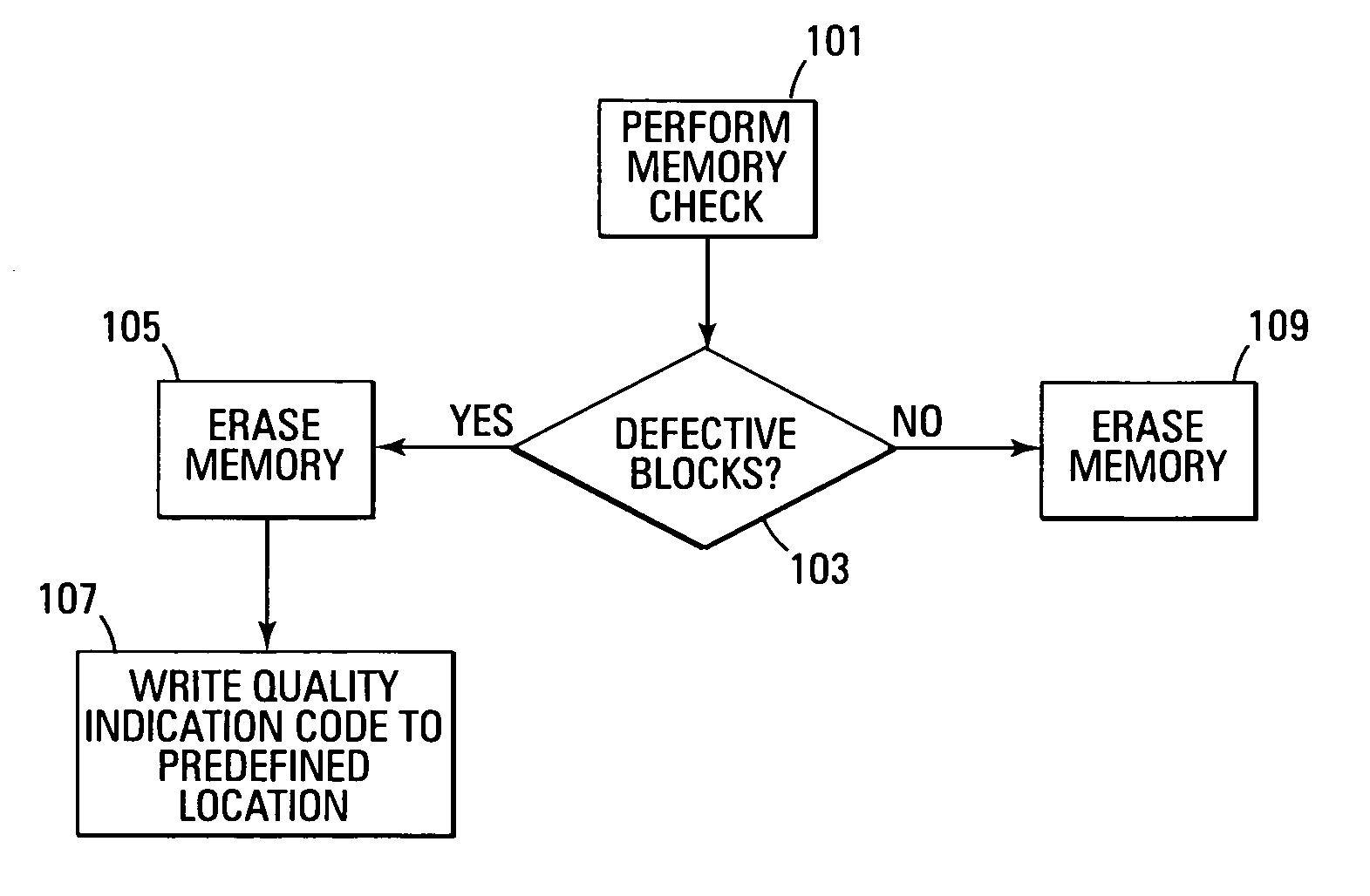

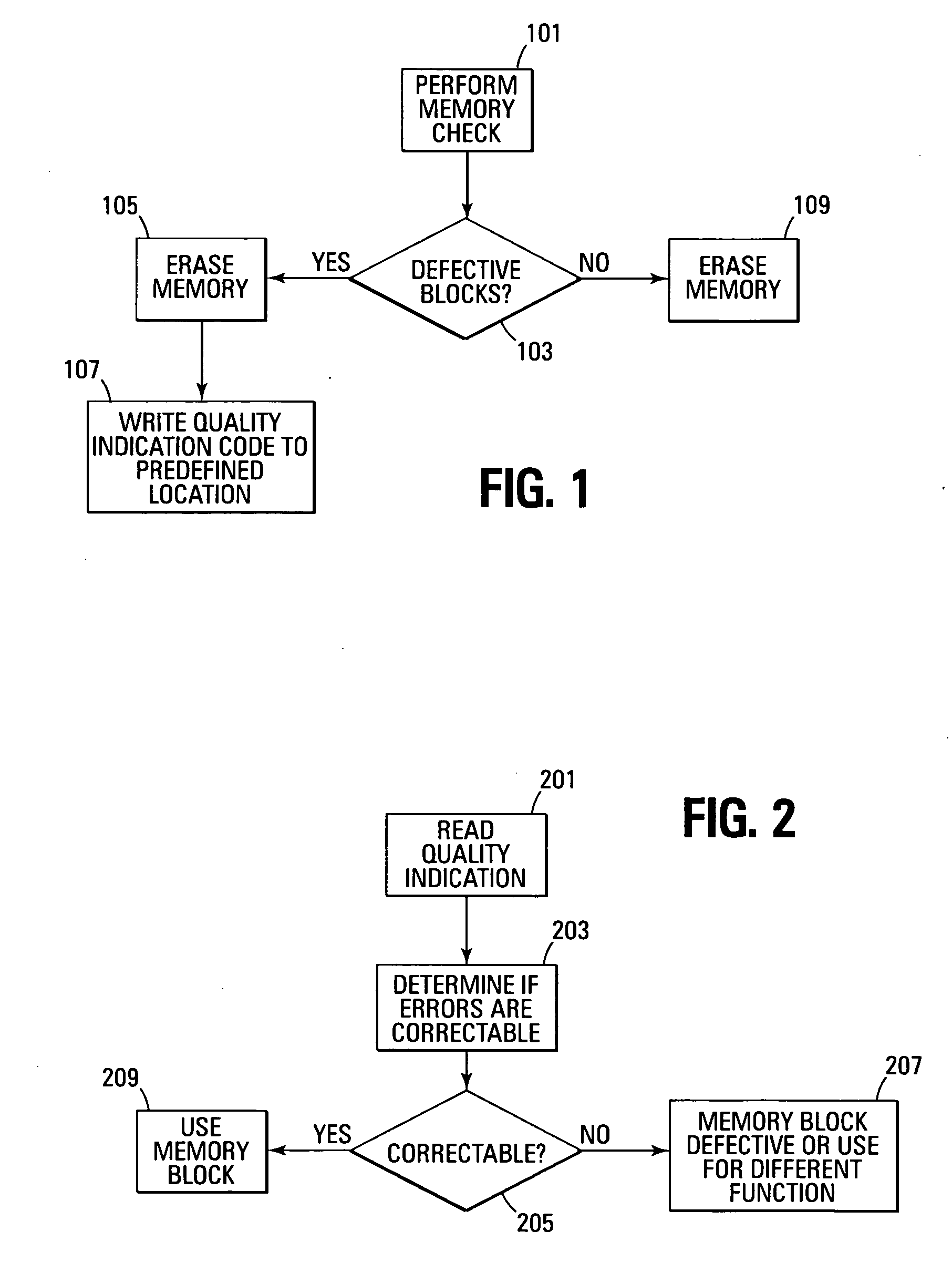

If a memory block in a flash memory device is found to have a defect, a memory block quality indication is generated in response to the type of memory defect. This indication is stored in the memory device. In one embodiment, the quality indication is stored in a predetermined location of the defective memory block. Using the quality indication, it can be determined if a system's error correction code scheme is capable of correcting data errors resulting from the defect.

Owner:MICRON TECH INC

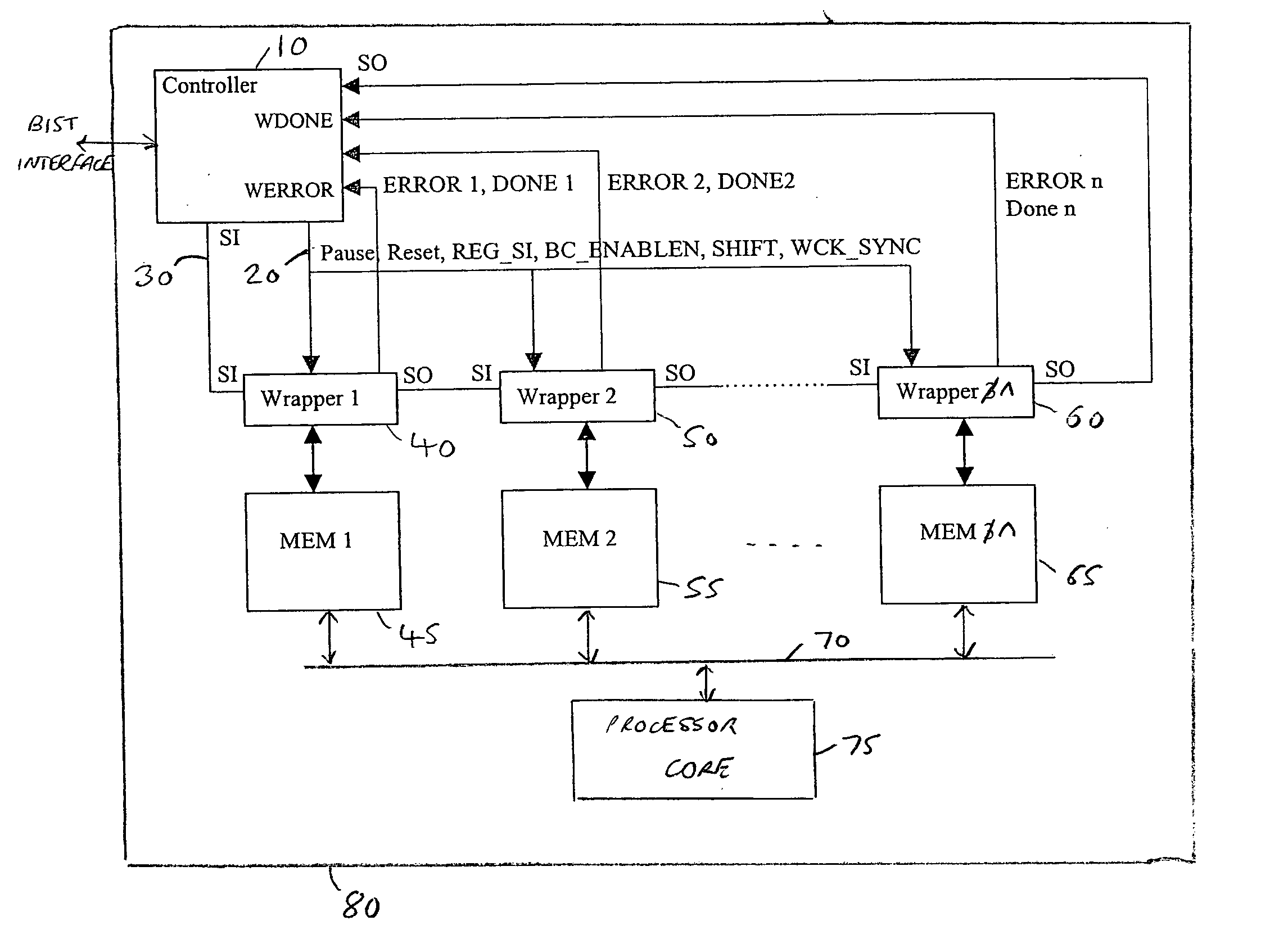

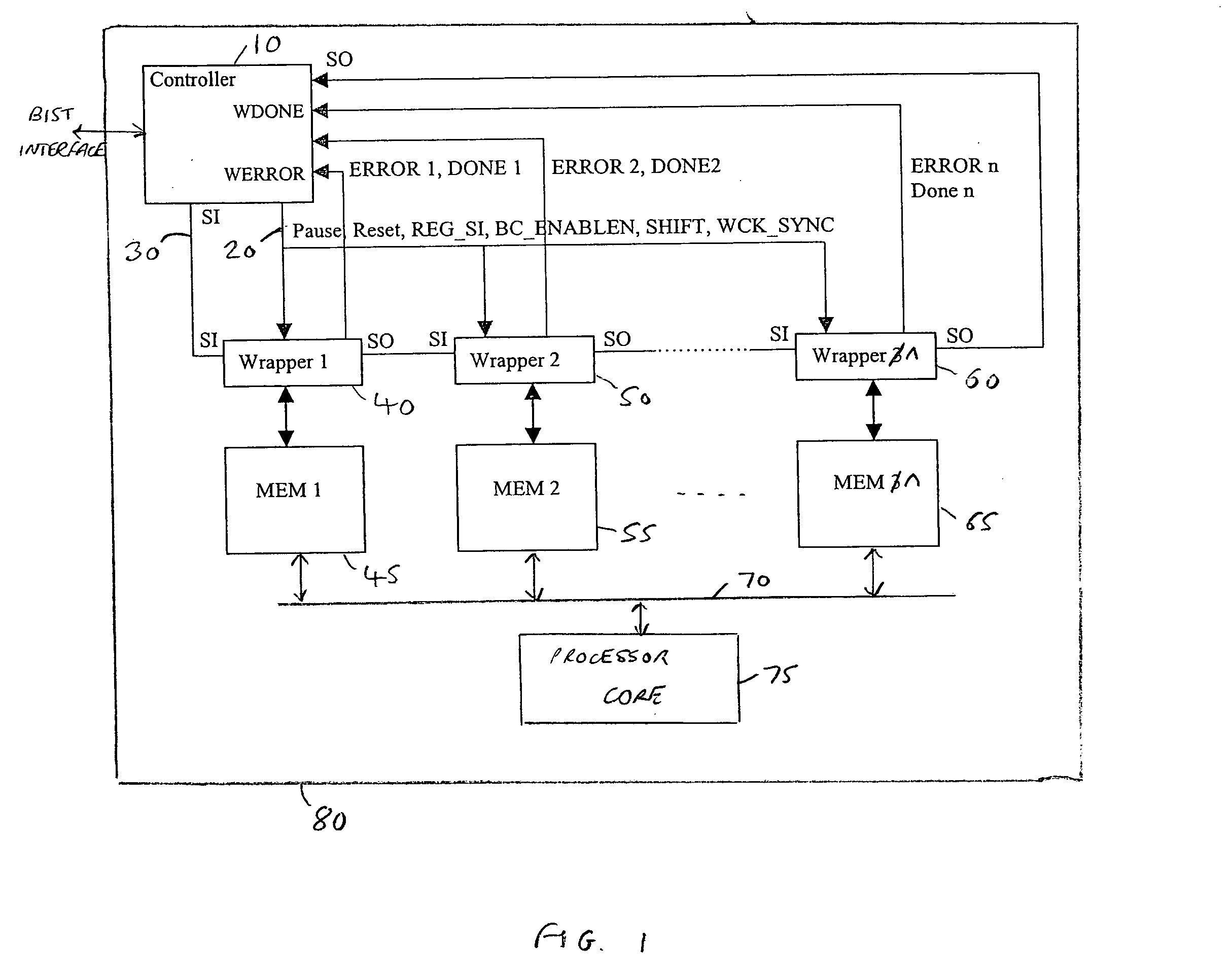

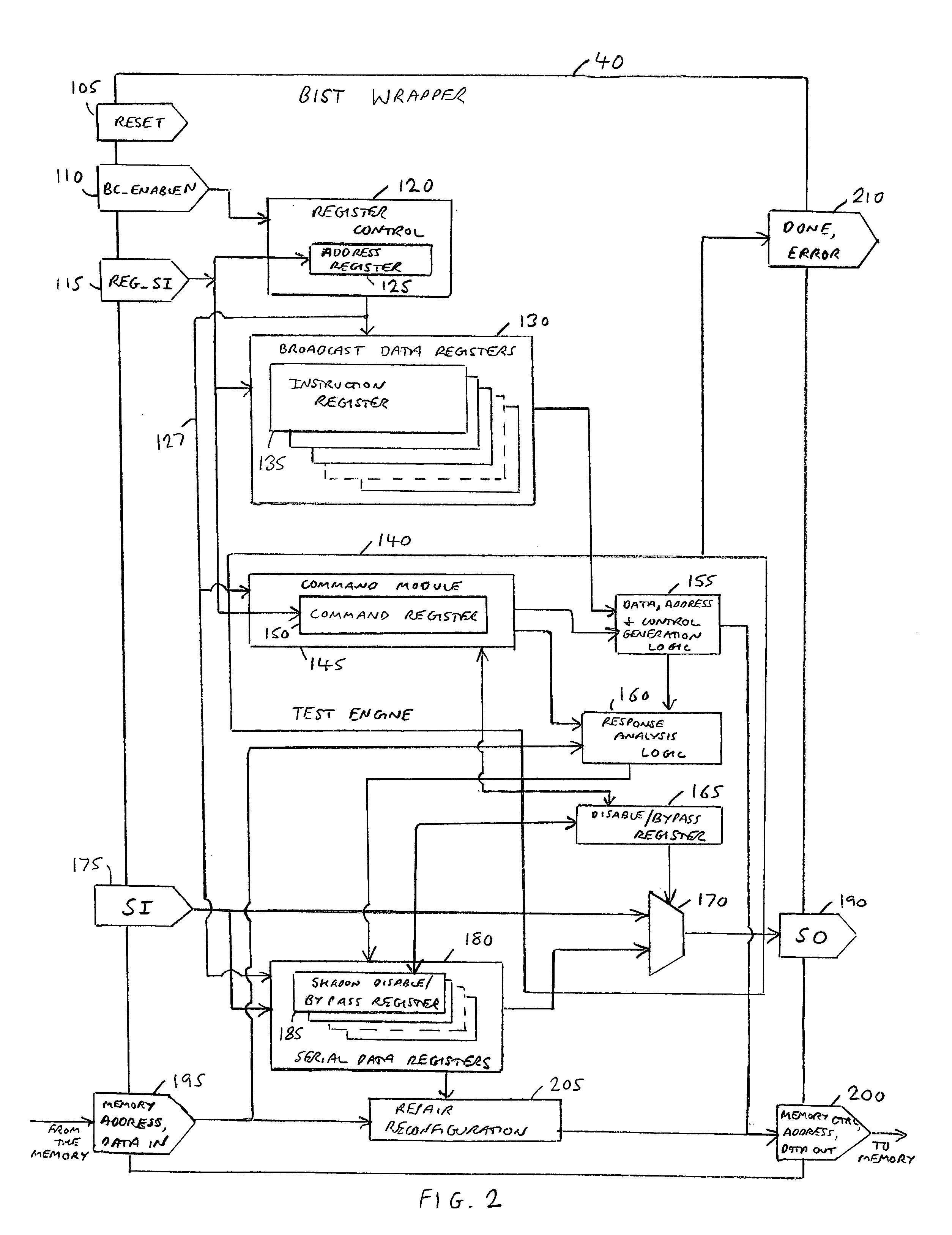

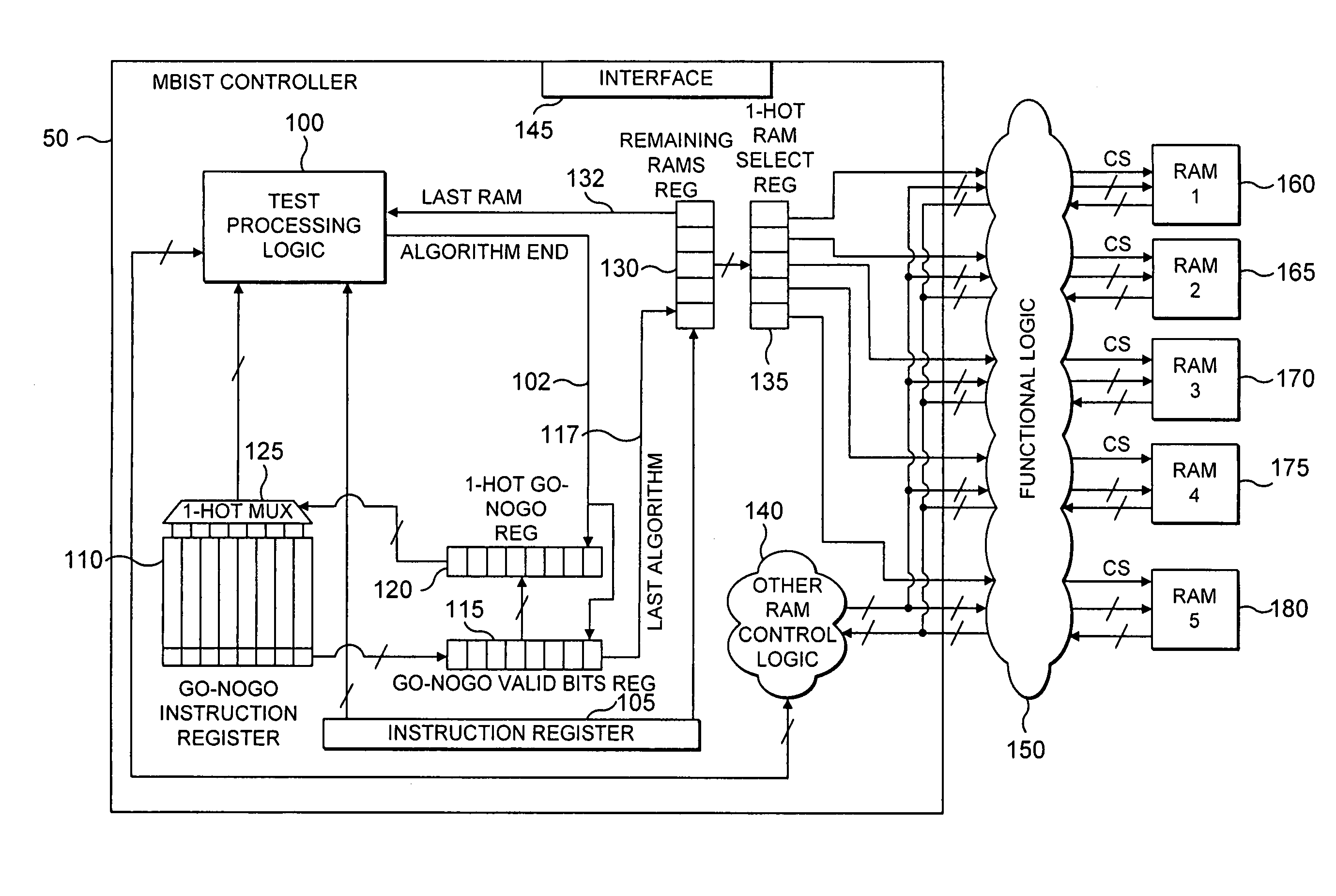

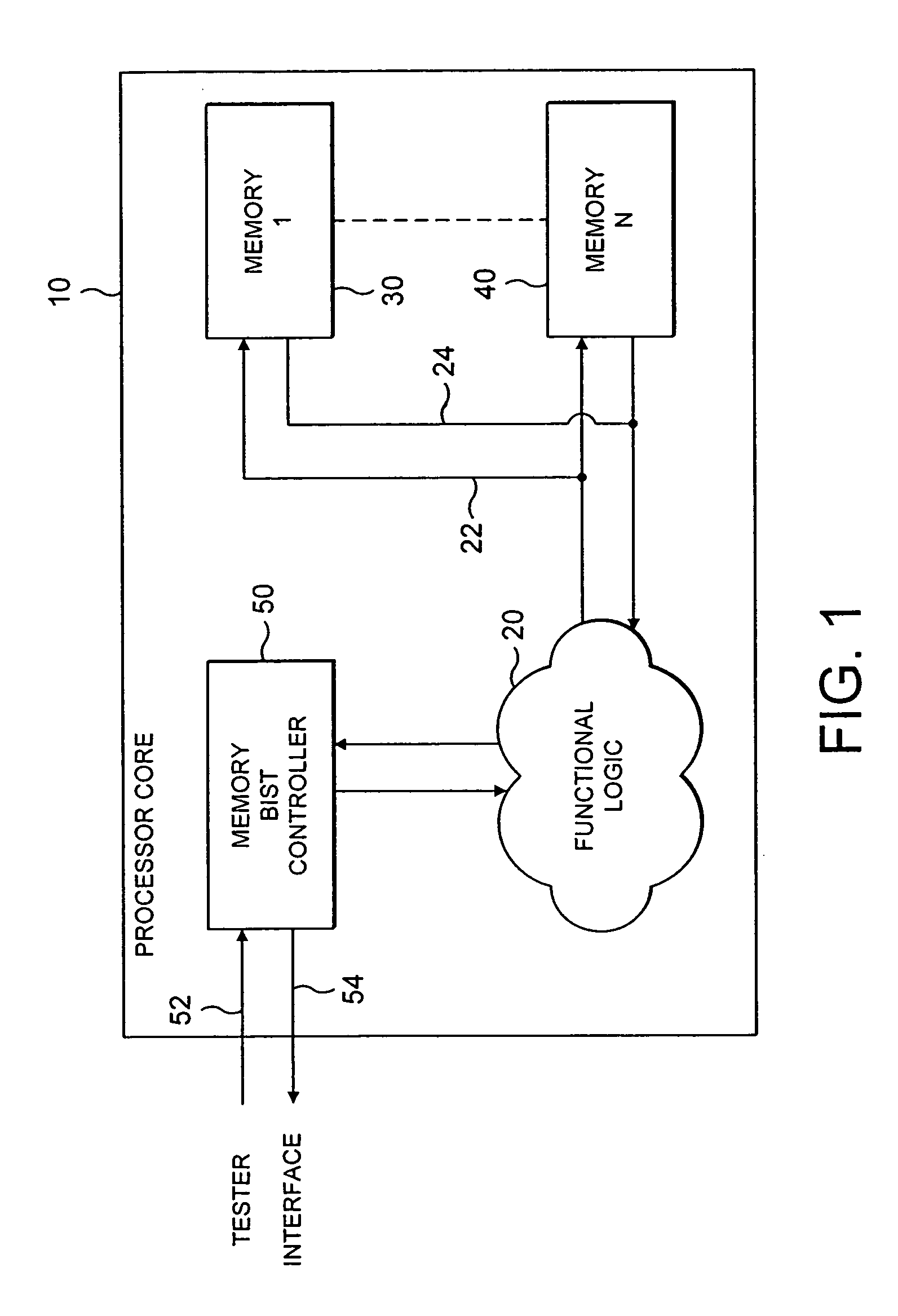

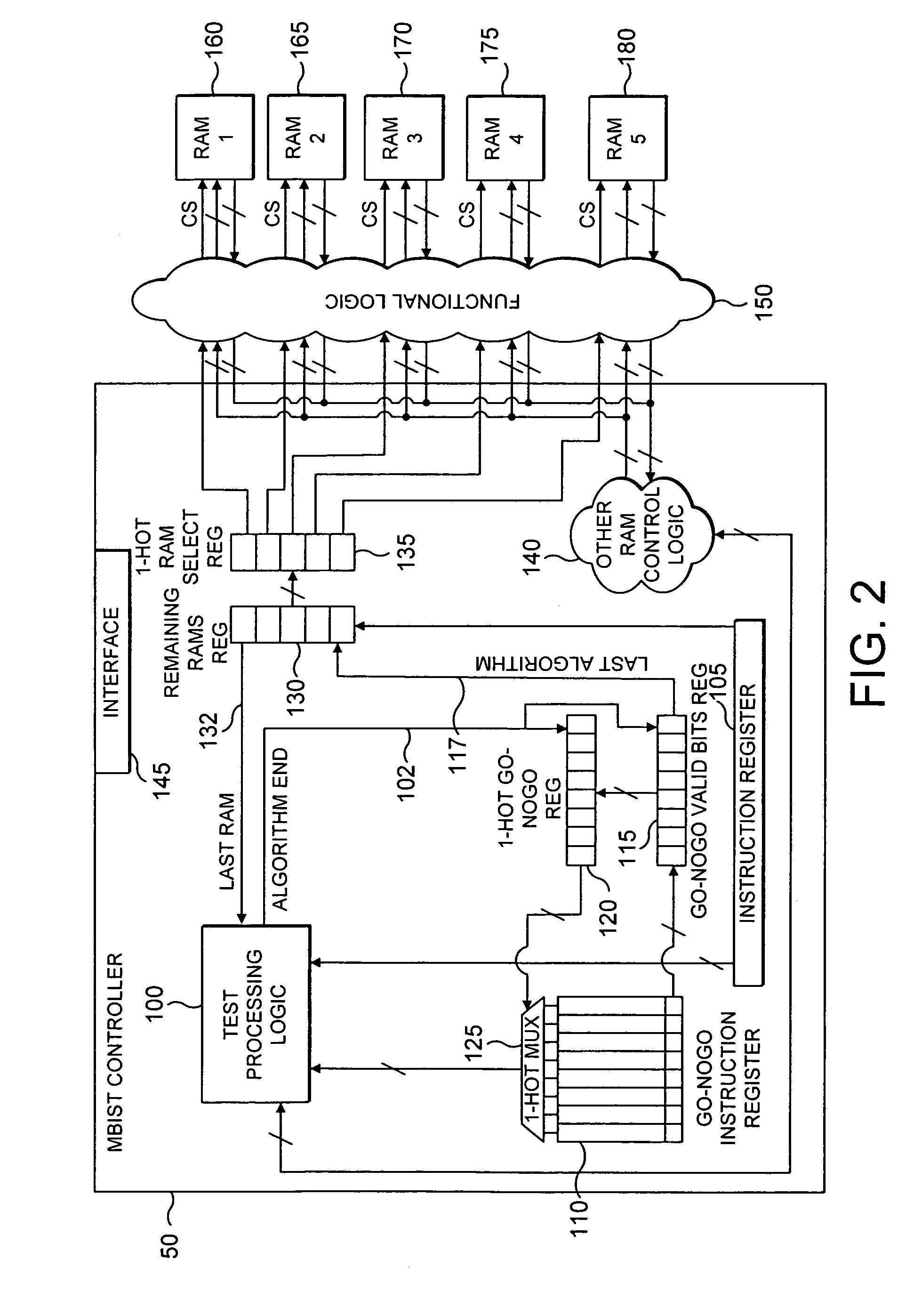

Integrated circuit and method for testing memory on the integrated circuit

ActiveUS20070106923A1Improve scalabilityIncrease the number ofElectronic circuit testingError detection/correctionComputer hardwareCommunication link

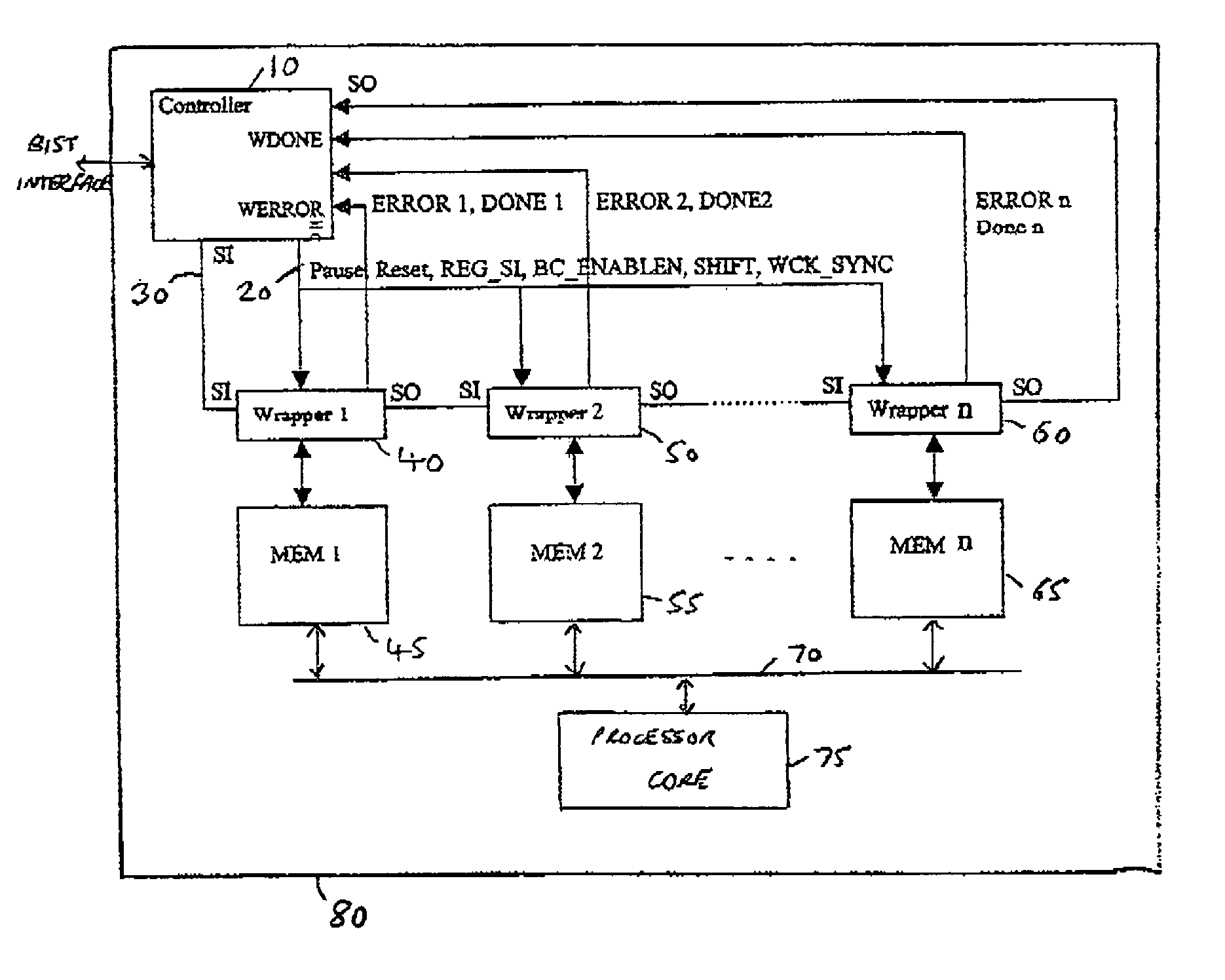

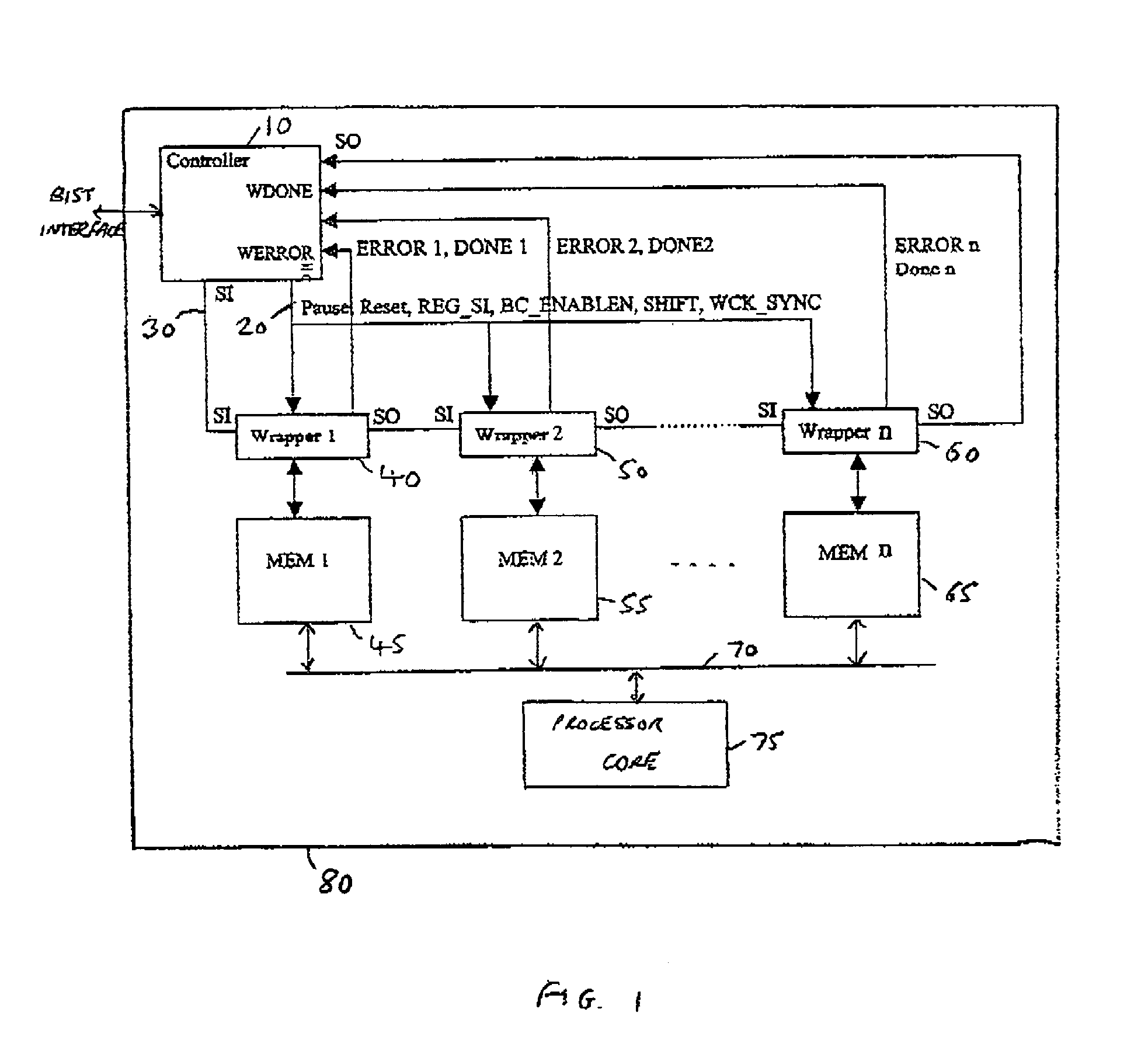

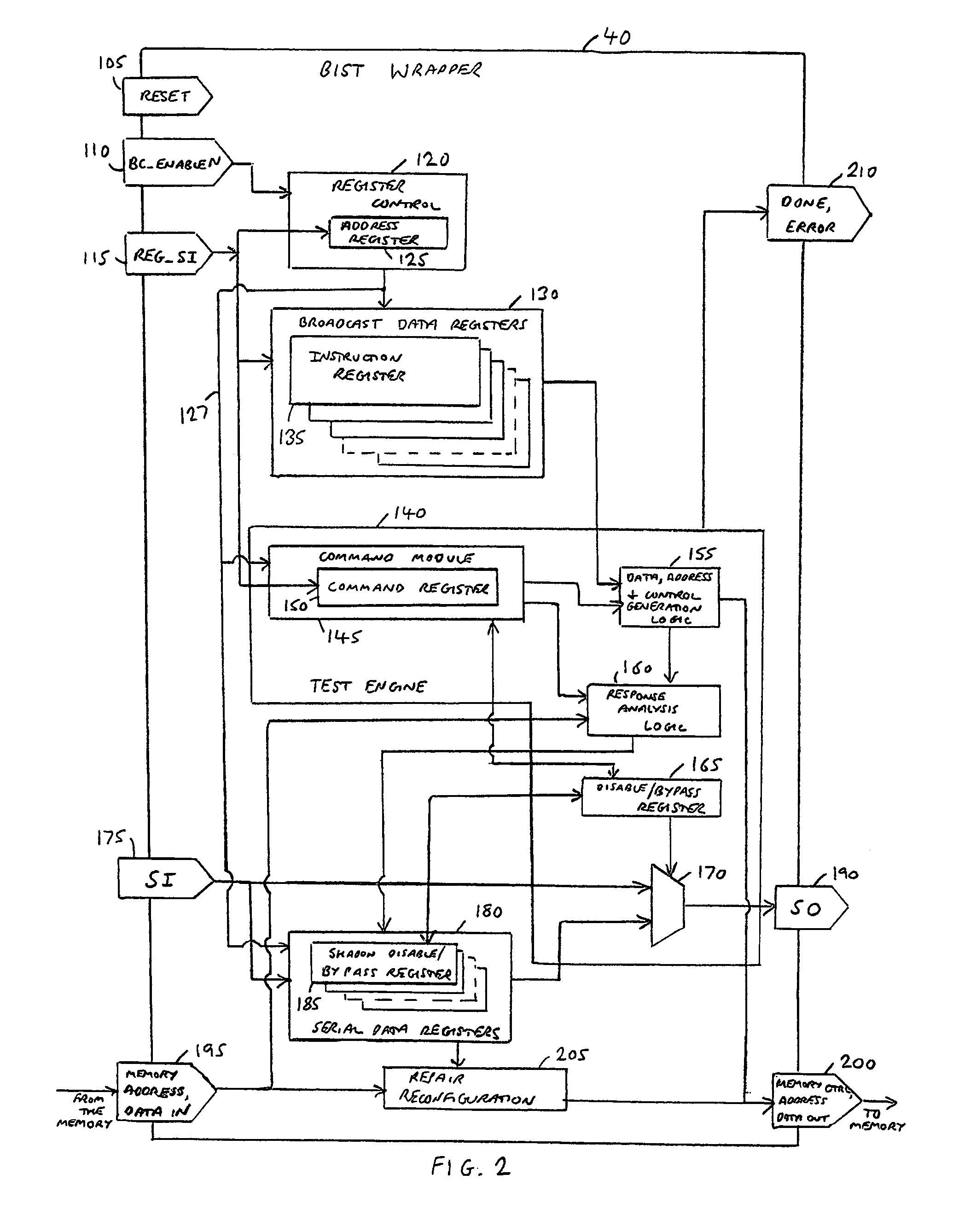

An integrated circuit and method for testing memory on the integrated circuit are provided. The integrated circuit has processing logic for performing data processing operations on data, and a plurality of memory units for storing data for access by the processing logic. Further, memory test logic is provided to perform a sequence of tests in order to seek to detect memory defects in the memory units. The memory test logic comprises a plurality of test wrapper units, each test wrapper unit associated with one of the memory units and being operable to execute tests on the associated memory unit, and a test controller for controlling performance of the sequence of tests by communicating with each of the test wrapper units to provide test data defining each test to be executed by that test wrapper unit. Further, a first communication link is provided for connecting each of the test wrapper units directly to the test controller, and a second communication link is provided for connecting each test wrapper unit in an ordered sequence with the test controller. When controlling performance of the sequence of tests, the test controller provides first test data via the first communication link and second test data via the second communication link. It has been found that such an approach provides a particularly efficient and flexible technique for performing BIST functions within the integrated circuit.

Owner:ARM LTD

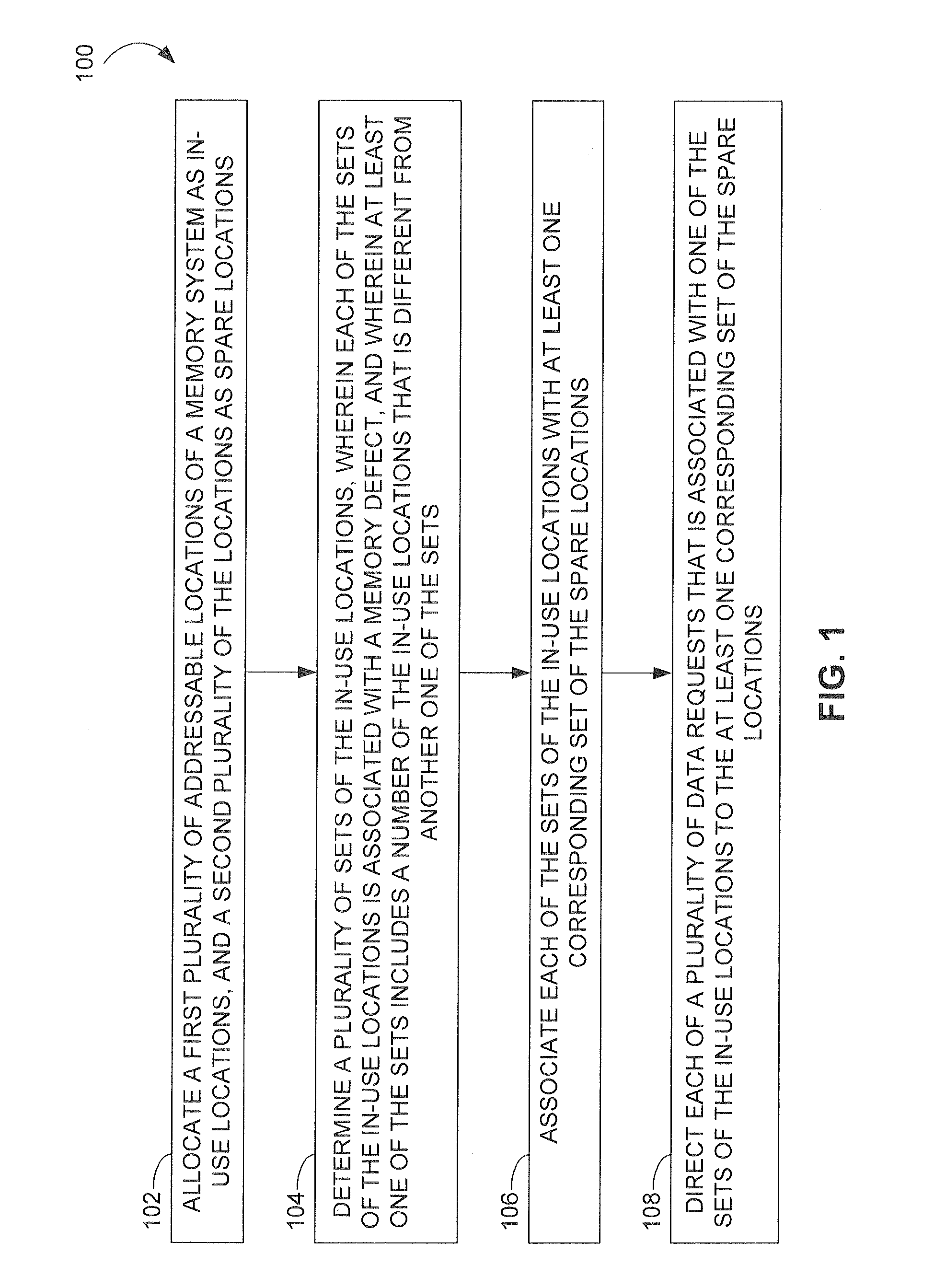

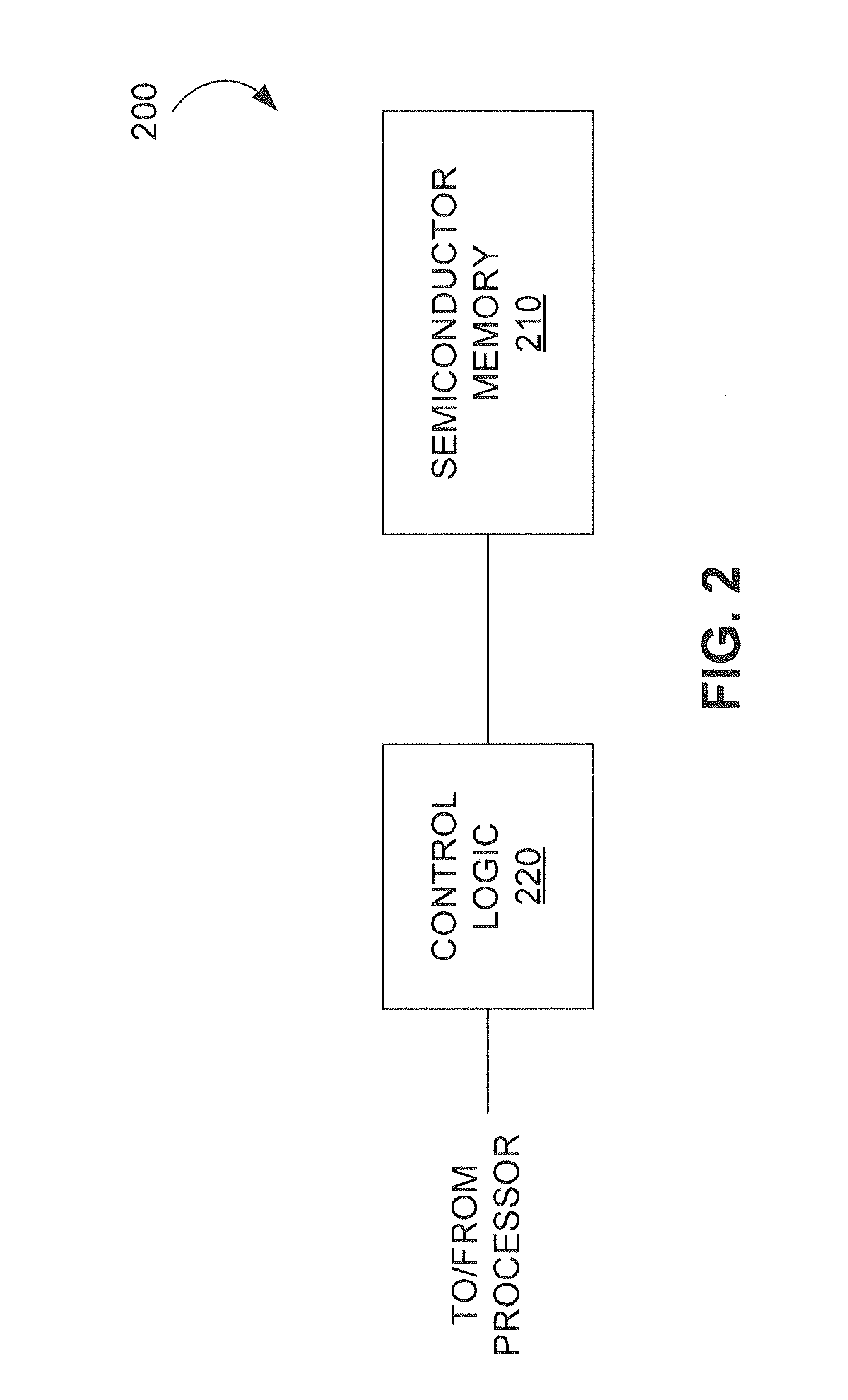

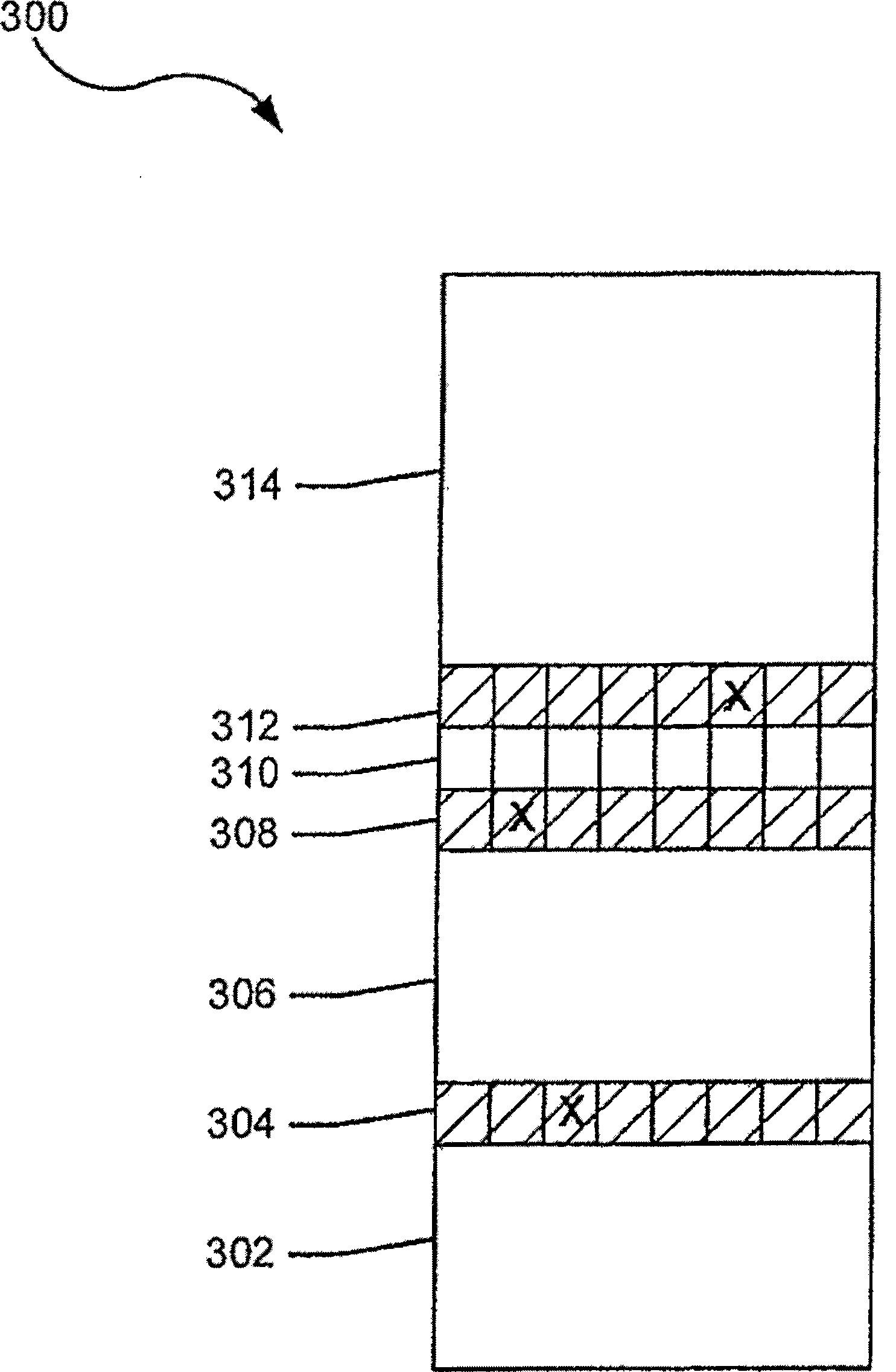

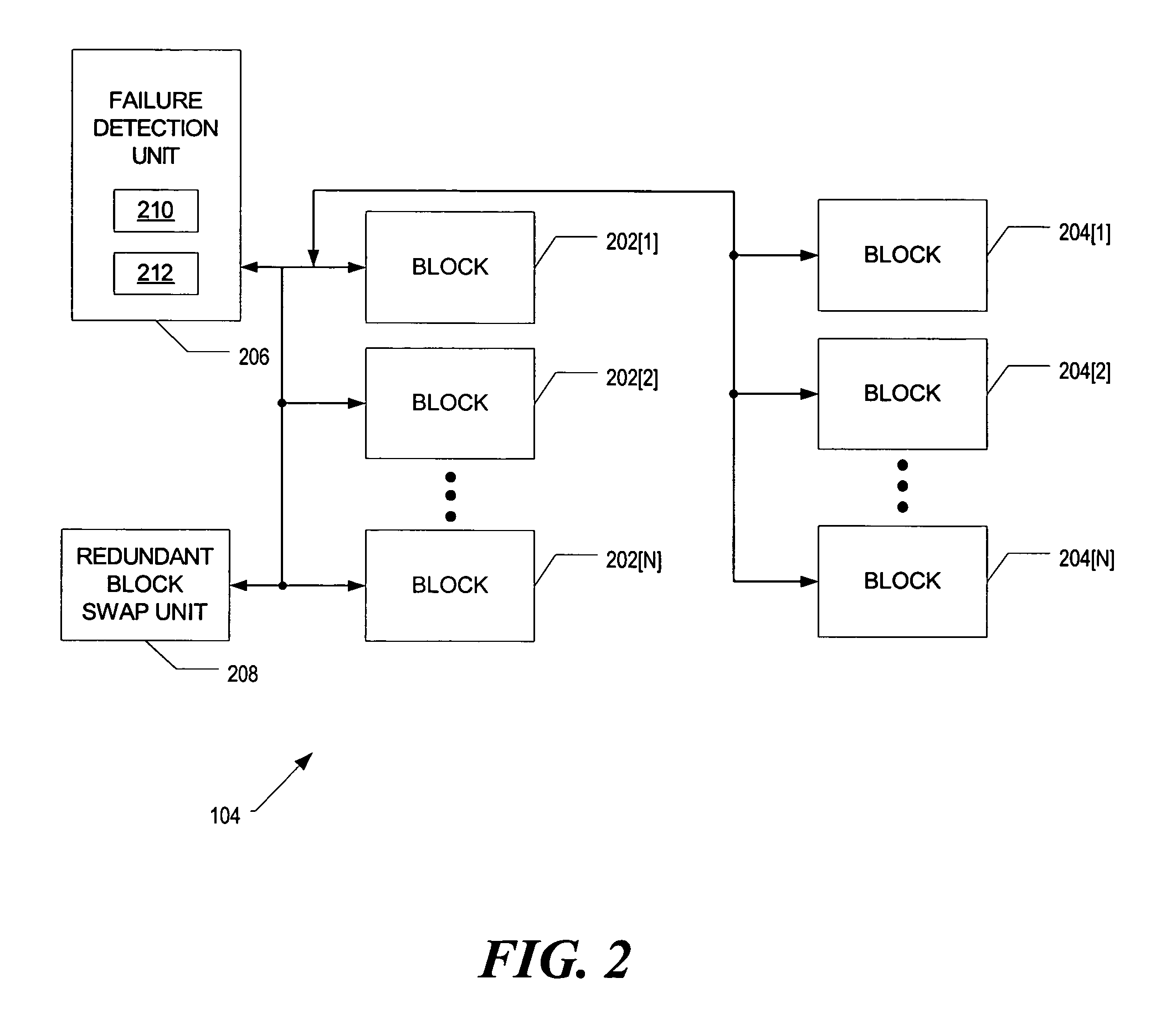

Defect management for a semiconductor memory system

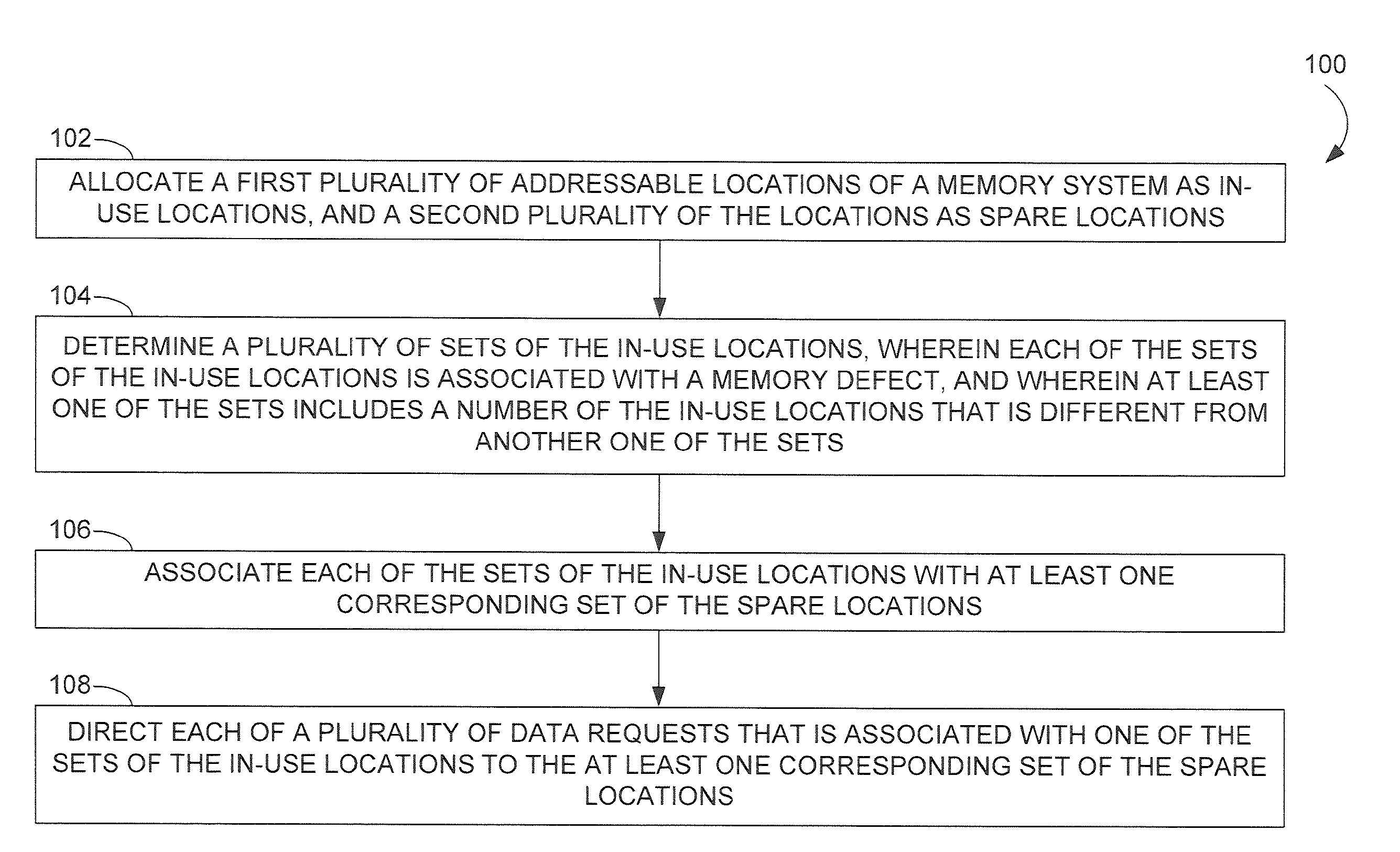

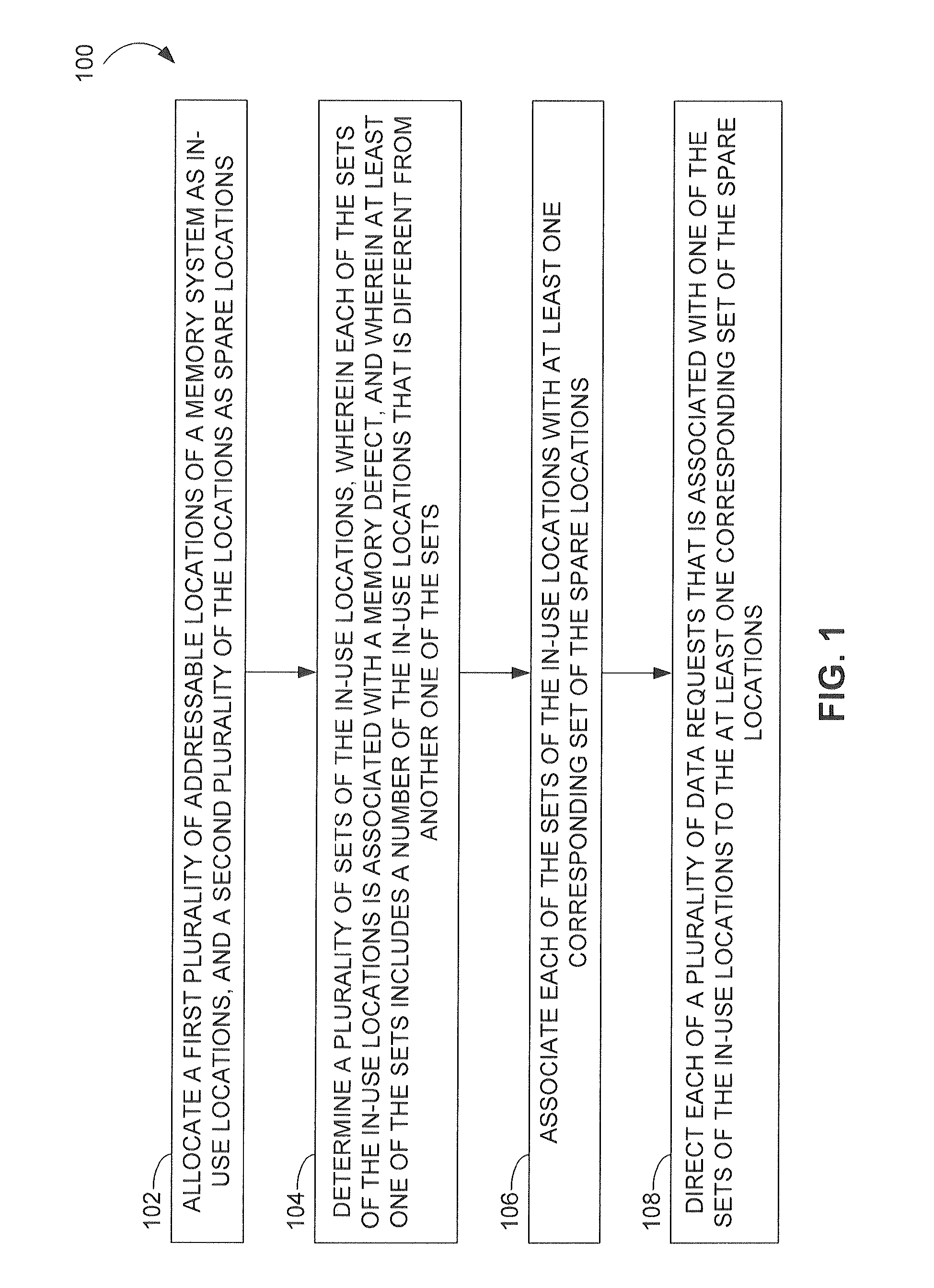

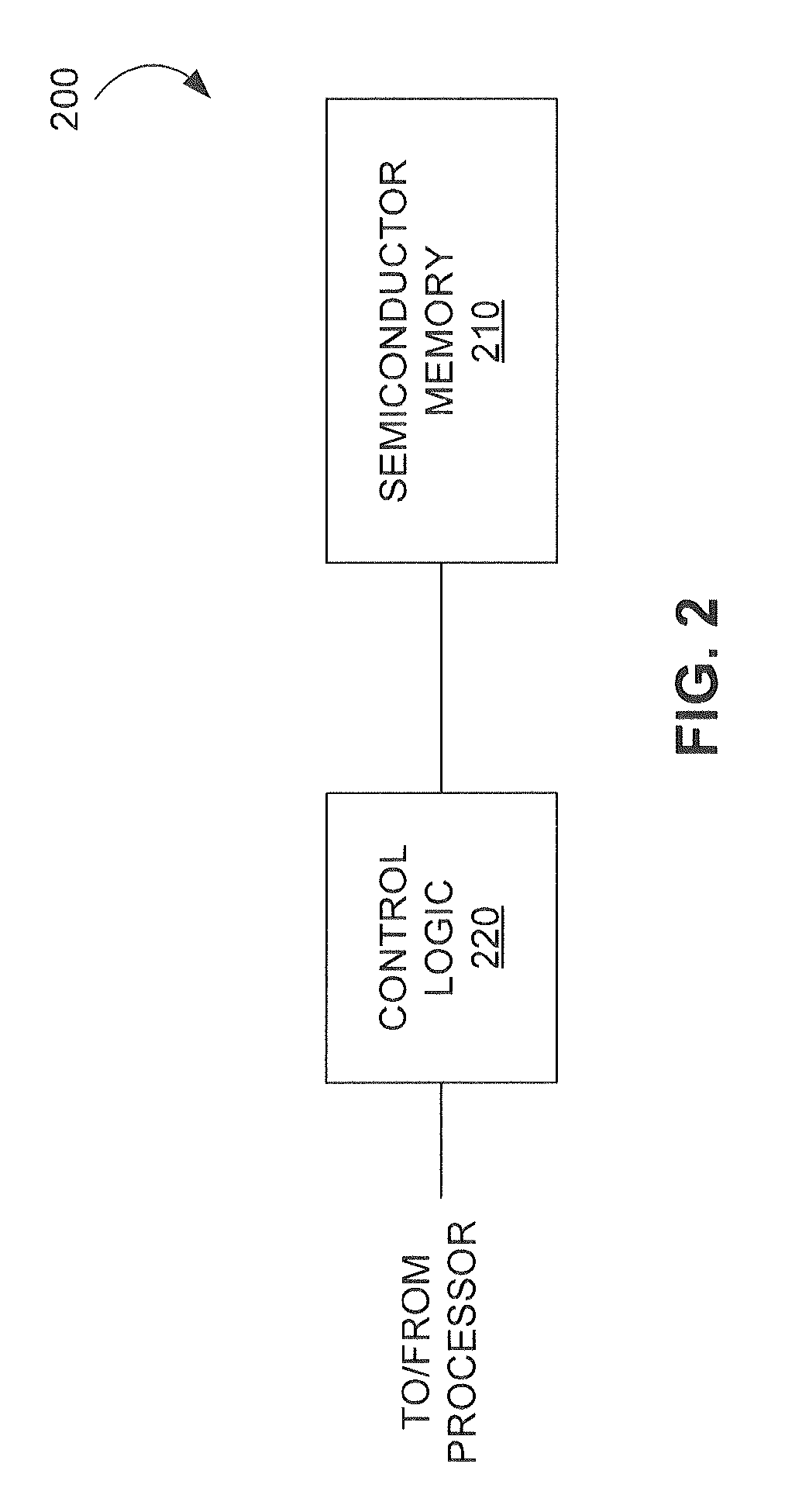

A method is provided for managing defects in a semiconductor memory system having a plurality of addressable locations. In the method, a first plurality of the addressable locations is allocated as in-use locations, and a second plurality of the addressable locations is allocated as spare locations. A plurality of sets of the in-use locations, wherein each of the sets is associated with a memory defect, is determined. At least one of the sets includes a different number of in-use locations than another of the sets. Each of the sets of the in-use locations is associated with at least one corresponding set of the spare locations. Each of a plurality of data requests that is associated with one of the sets of the in-use locations is directed to the at least one corresponding set of the spare locations.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

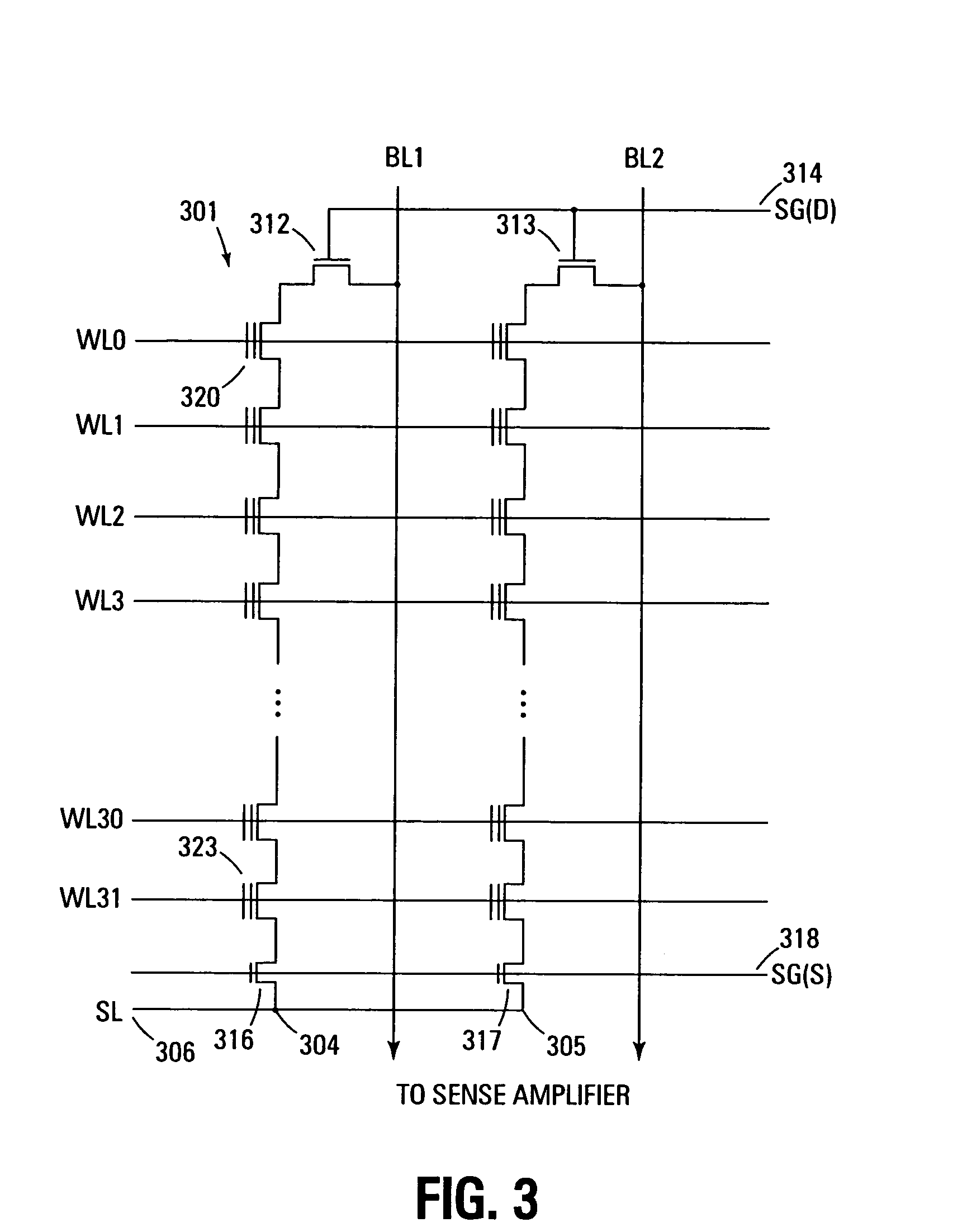

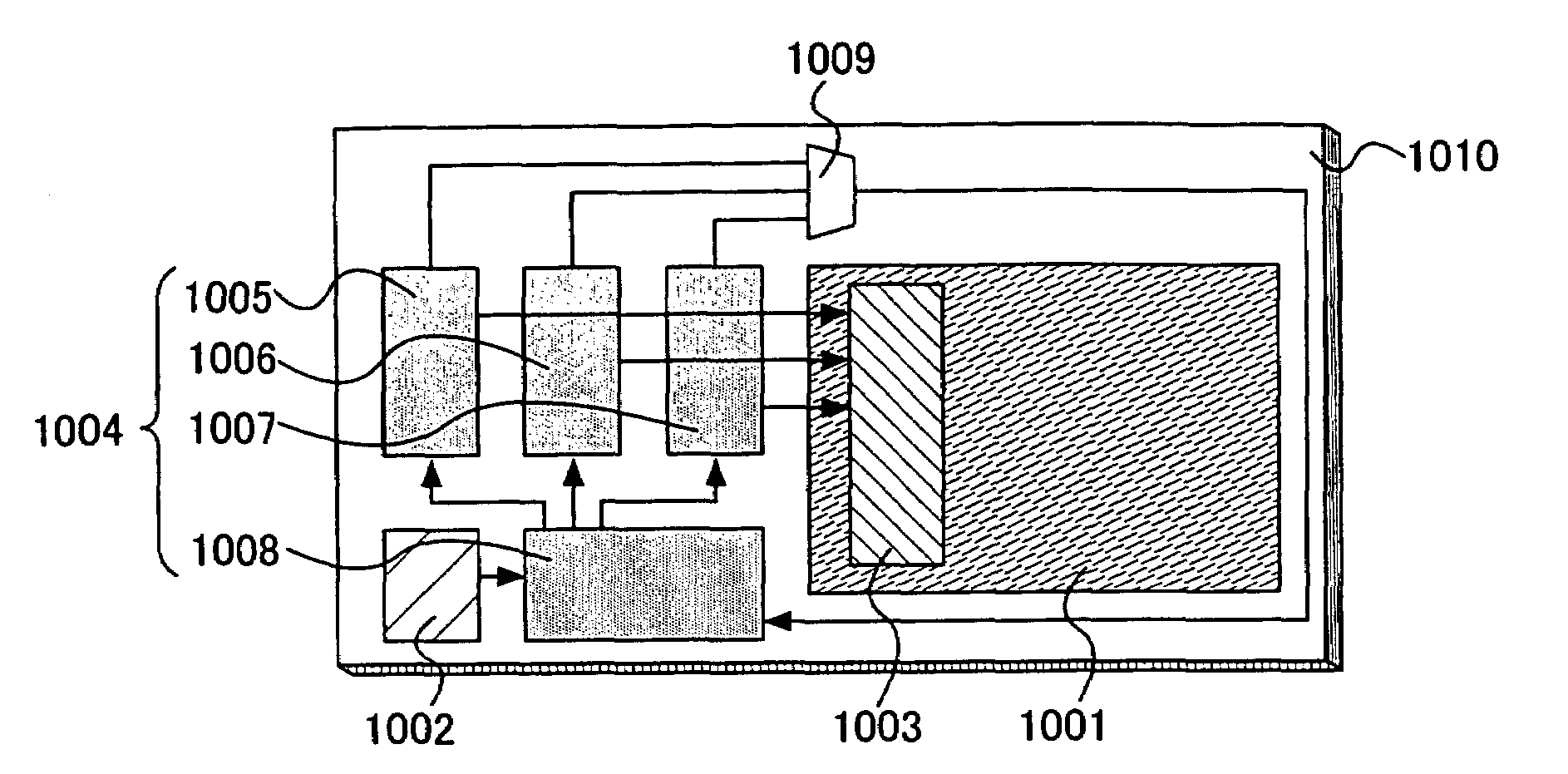

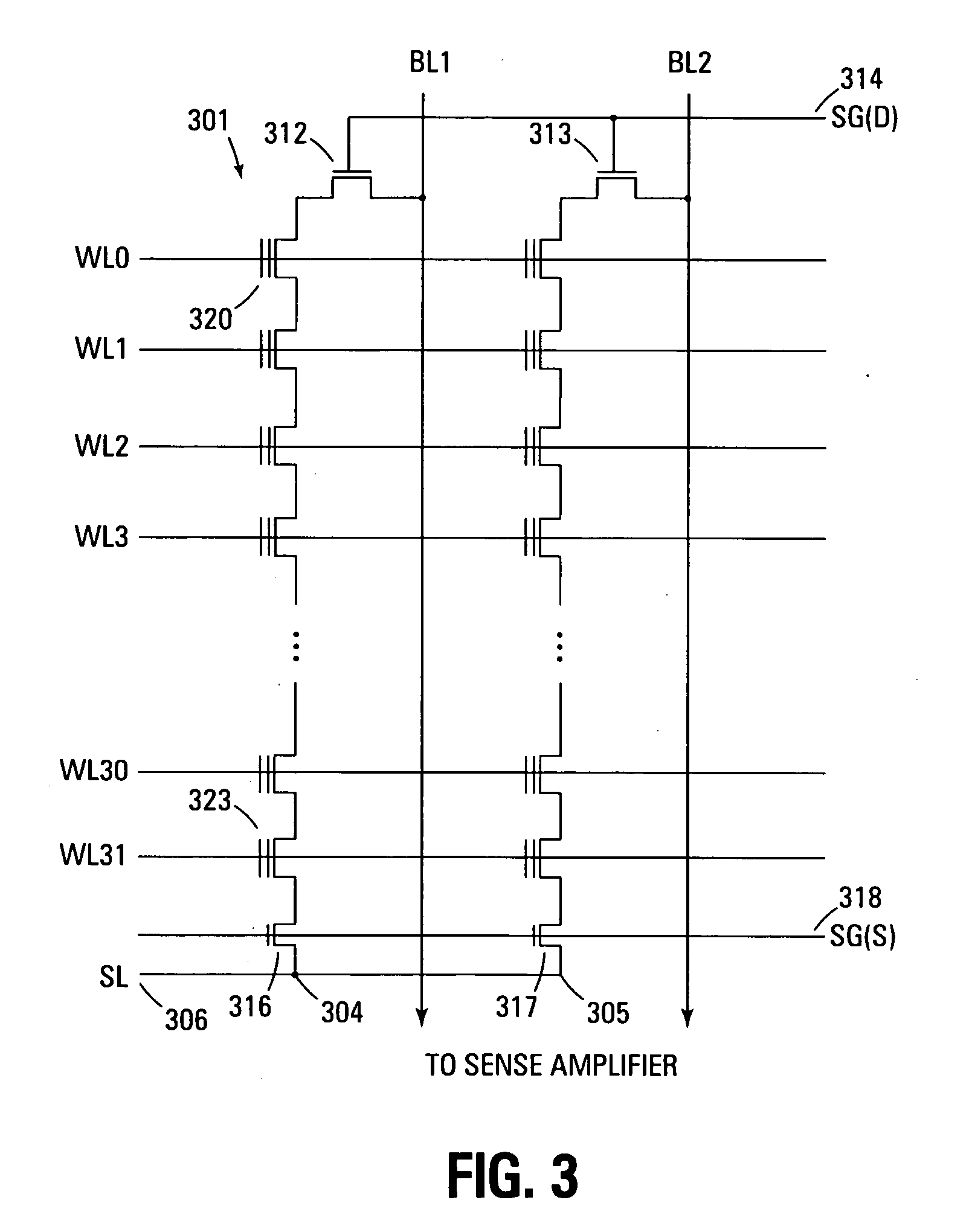

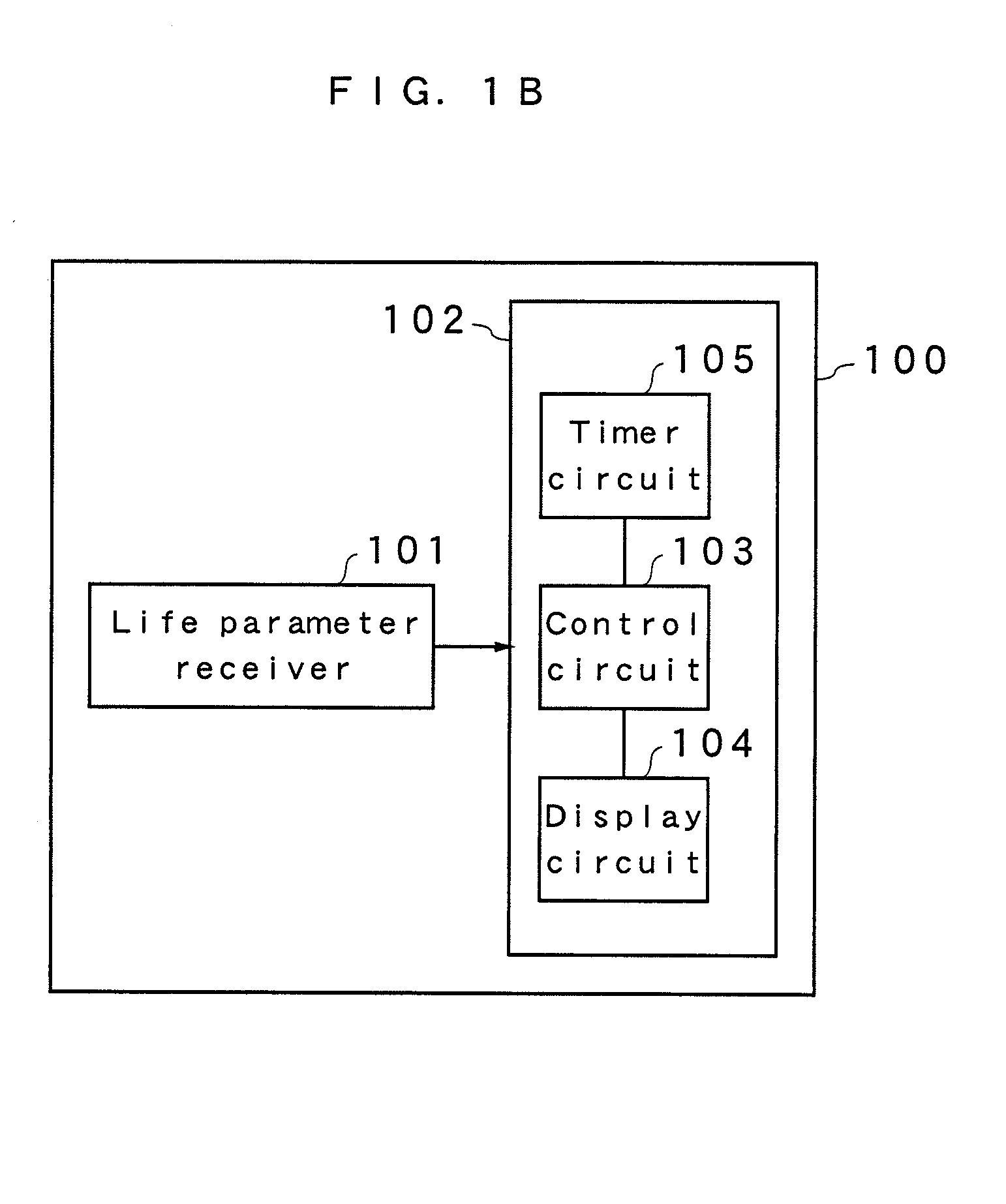

Semiconductor device for rectifying memory defects

ActiveUS7239564B2Defect correctionElectronic circuit testingDigital storageBit lineComputer hardware

The present invention provides a high-capacity and reliable semiconductor device which does not require additional circuits for use at power ON / OFF, additional steps nor high manufacturing cost, and which has a rectifier means for rectifying a defect easily. A semiconductor device comprises a first memory means including a memory cell and a redundant memory cell each including a memory element in the region where a bit line and a word line cross each other with an insulator interposed therebetween, a second memory means for storing an address of a defective memory in the first memory means, a rectifier means including a holding means and a replacement means, and an inspection means for writing data of the second memory means to the holding means. The replacement means replaces the defective memory cell with the redundant memory cell. In addition to the aforementioned four means, a display means for displaying images is provided as well.

Owner:SEMICON ENERGY LAB CO LTD

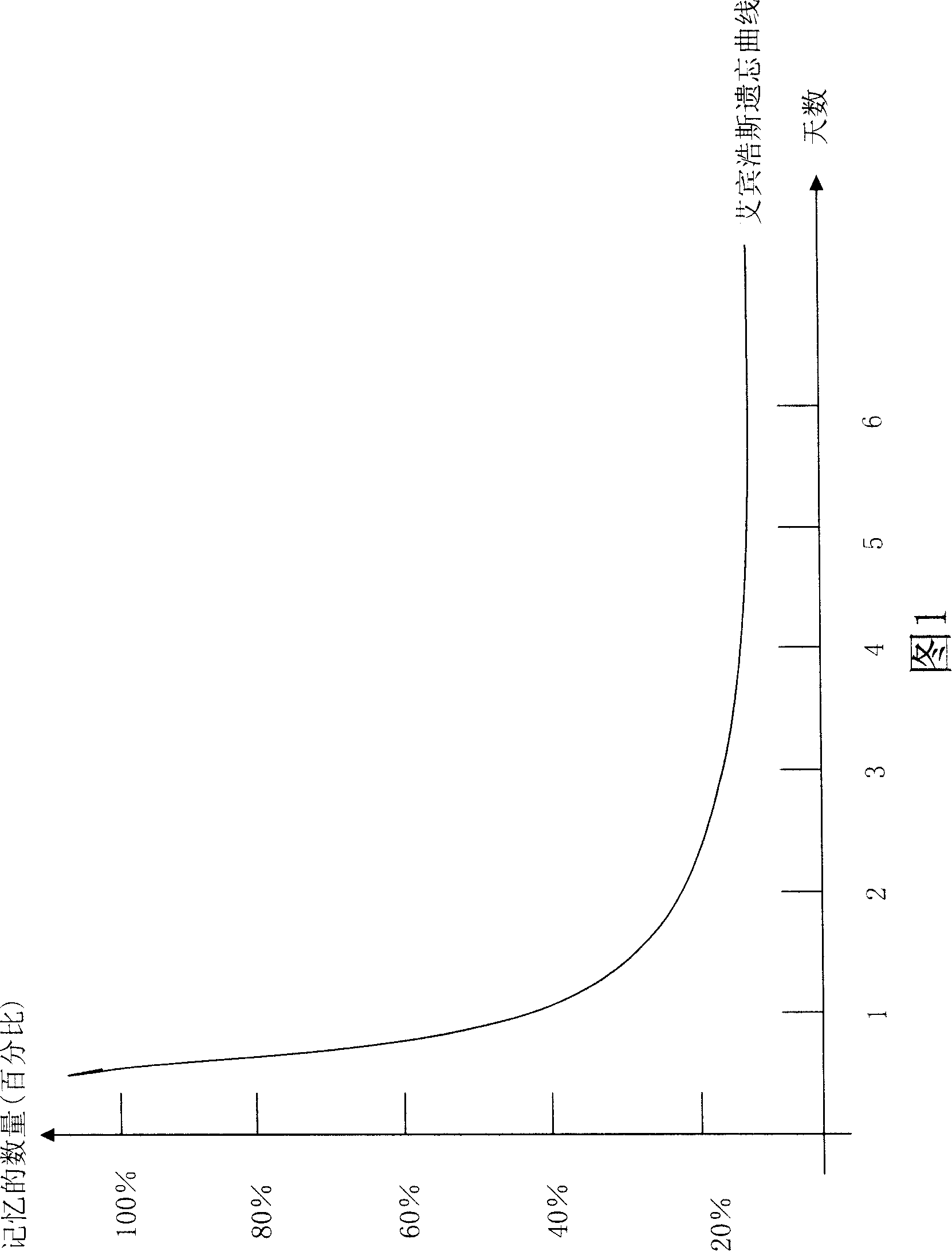

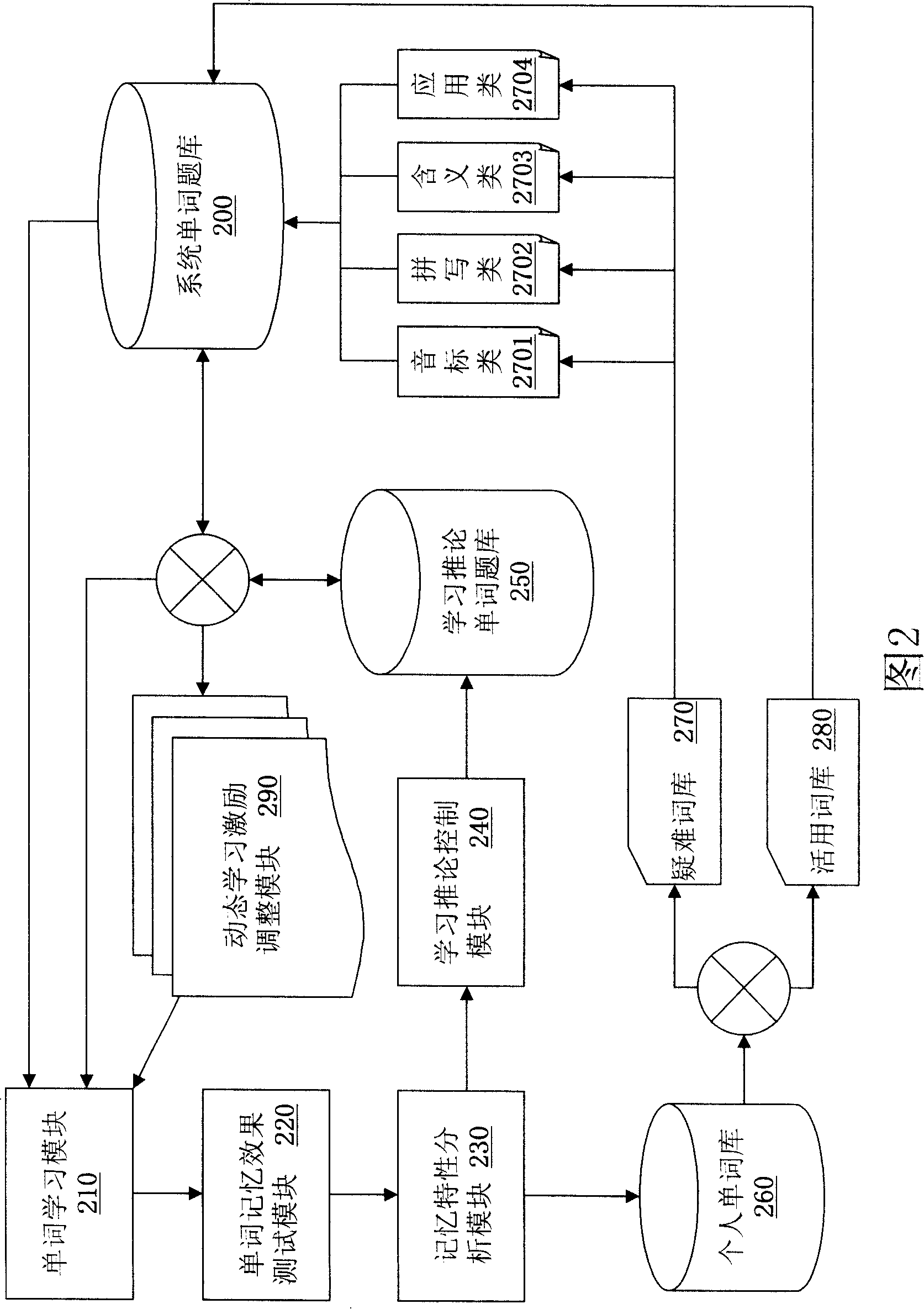

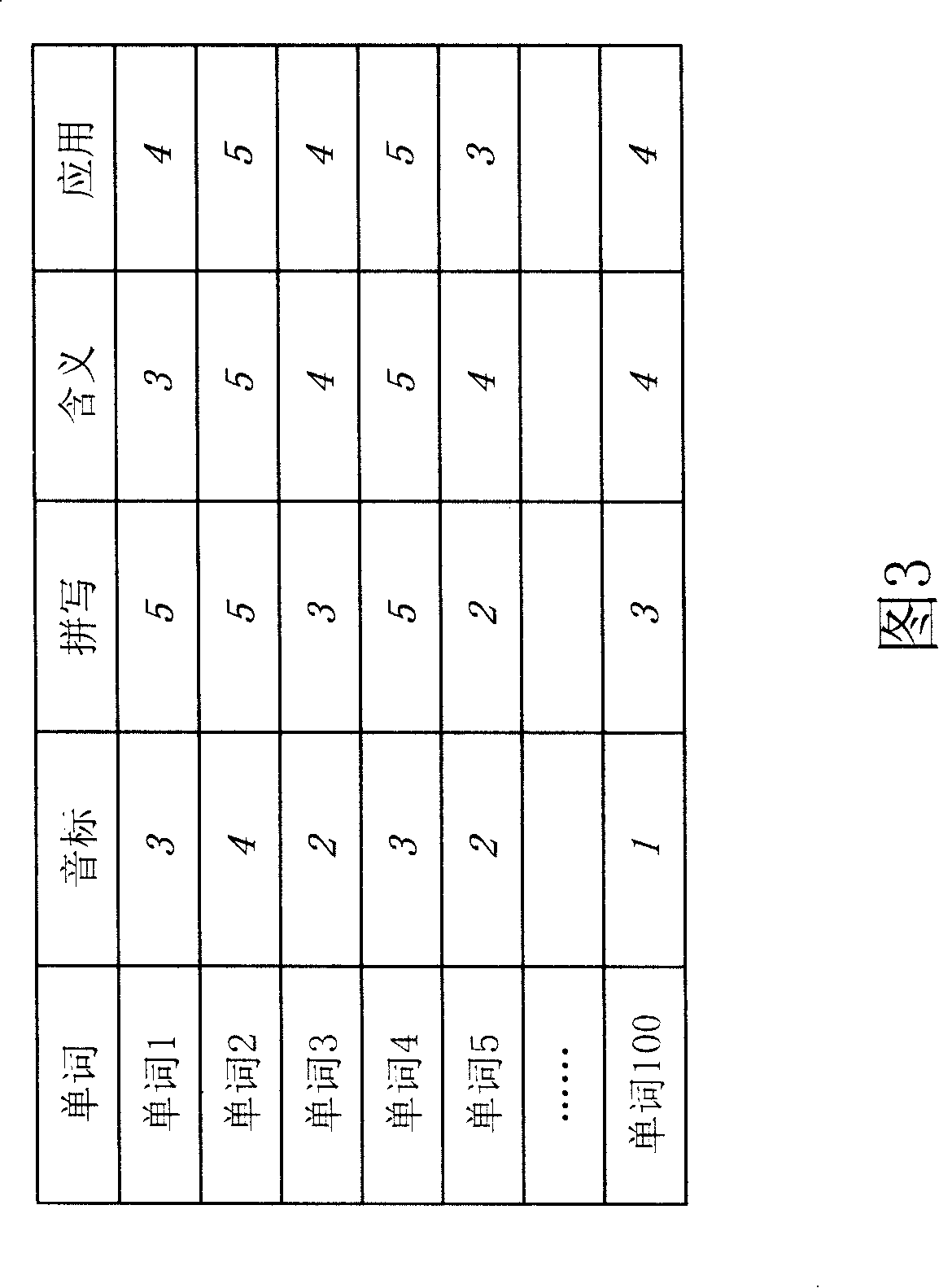

System and method for executive auxiliary learning of language word by computer

InactiveCN101201812AImprove memory efficiencyAvoid boringSpecial data processing applicationsTeaching apparatusMemory processPersonalization

The invention relates to a system that assists to study language word and is implemented by a computer and a method thereof, comprising a system word test item bank, a word studying module, a module used for testing the effect of memorizing words, an analysis module of characteristics of memory, a control module of studying inferences, a word test item bank of studying inferences, an individual word bank and a dynamic study field-controlled module; the forgetting curve and the memory defects are obtained by the statistics and analysis for the personal memory process of a learner and a individual word test item bank is customized for the individual according to the two characteristics, thus improving the efficiency of assisting to study language word.

Owner:INVENTEC CORP

Integrated circuit and method for testing memory on the integrated circuit

ActiveUS8145958B2Improve scalabilityIncrease the number ofElectronic circuit testingError detection/correctionComputer hardwareTelecommunications link

Owner:ARM LTD

Defect management for a semiconductor memory system

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Memory block quality identification in a memory device

If a memory block in a flash memory device is found to have a defect, a memory block quality indication is generated in response to the type of memory defect. This indication is stored in the memory device. In one embodiment, the quality indication is stored in a predetermined location of the defective memory block. Using the quality indication, it can be determined if a system's error correction code scheme is capable of correcting data errors resulting from the defect.

Owner:MICRON TECH INC

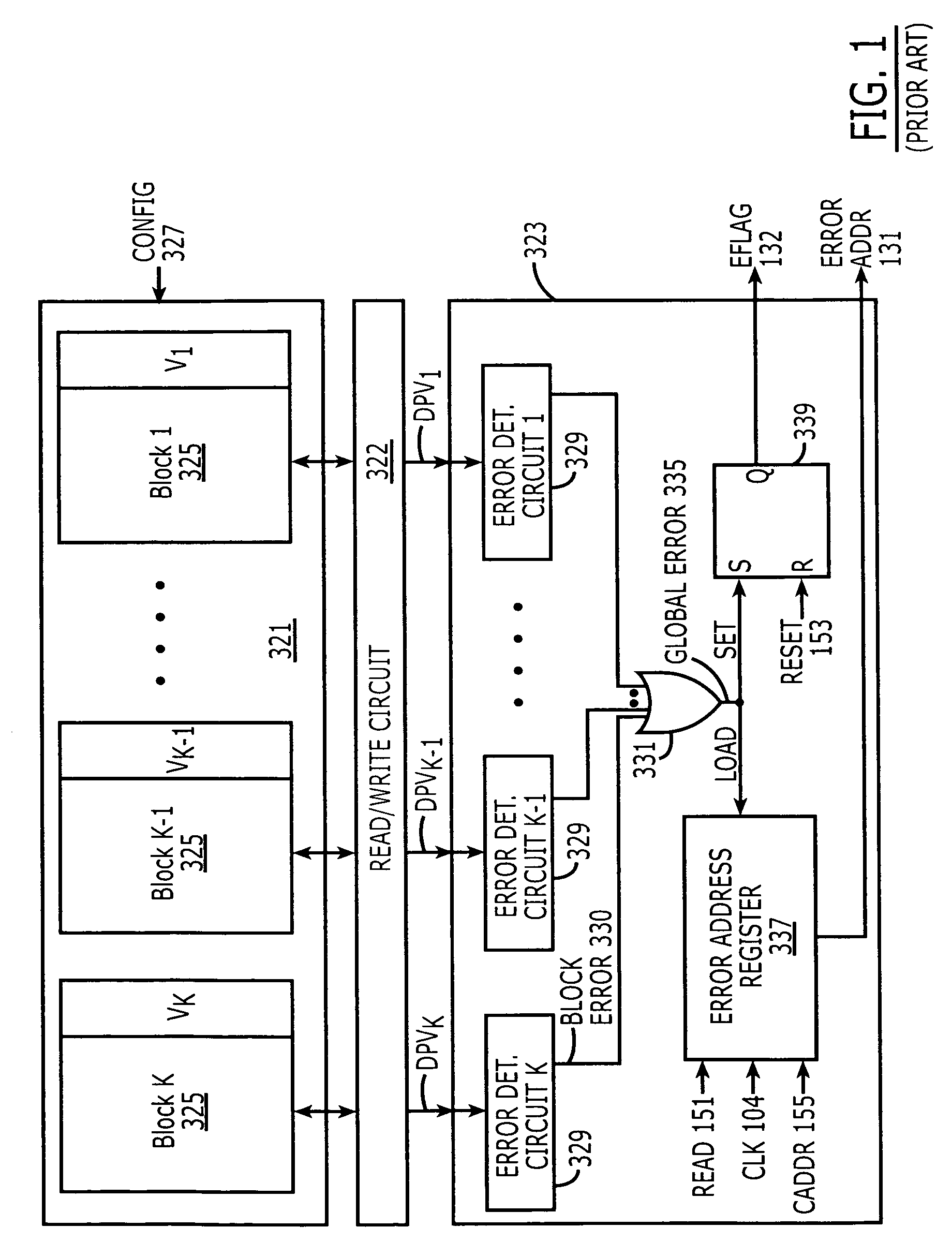

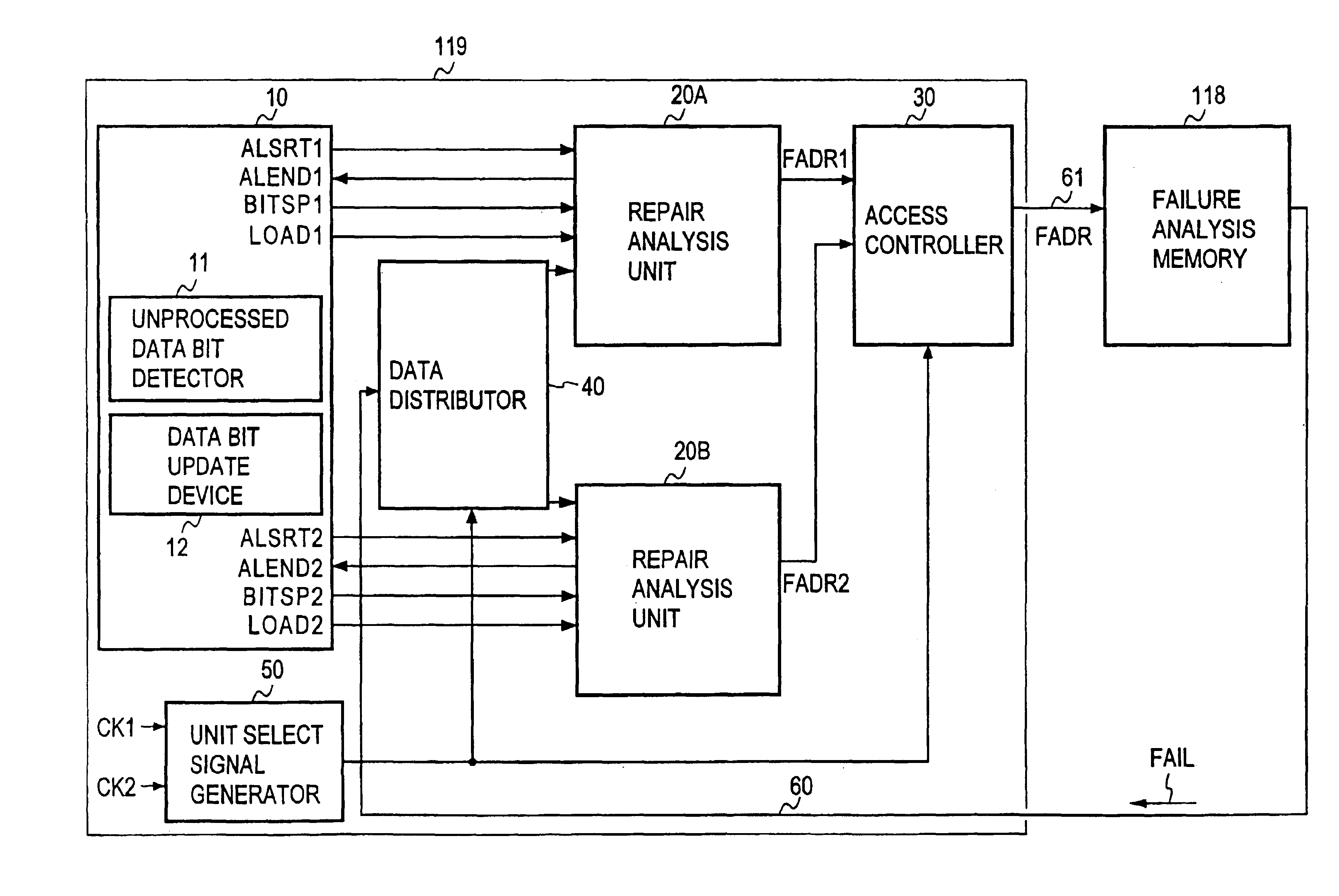

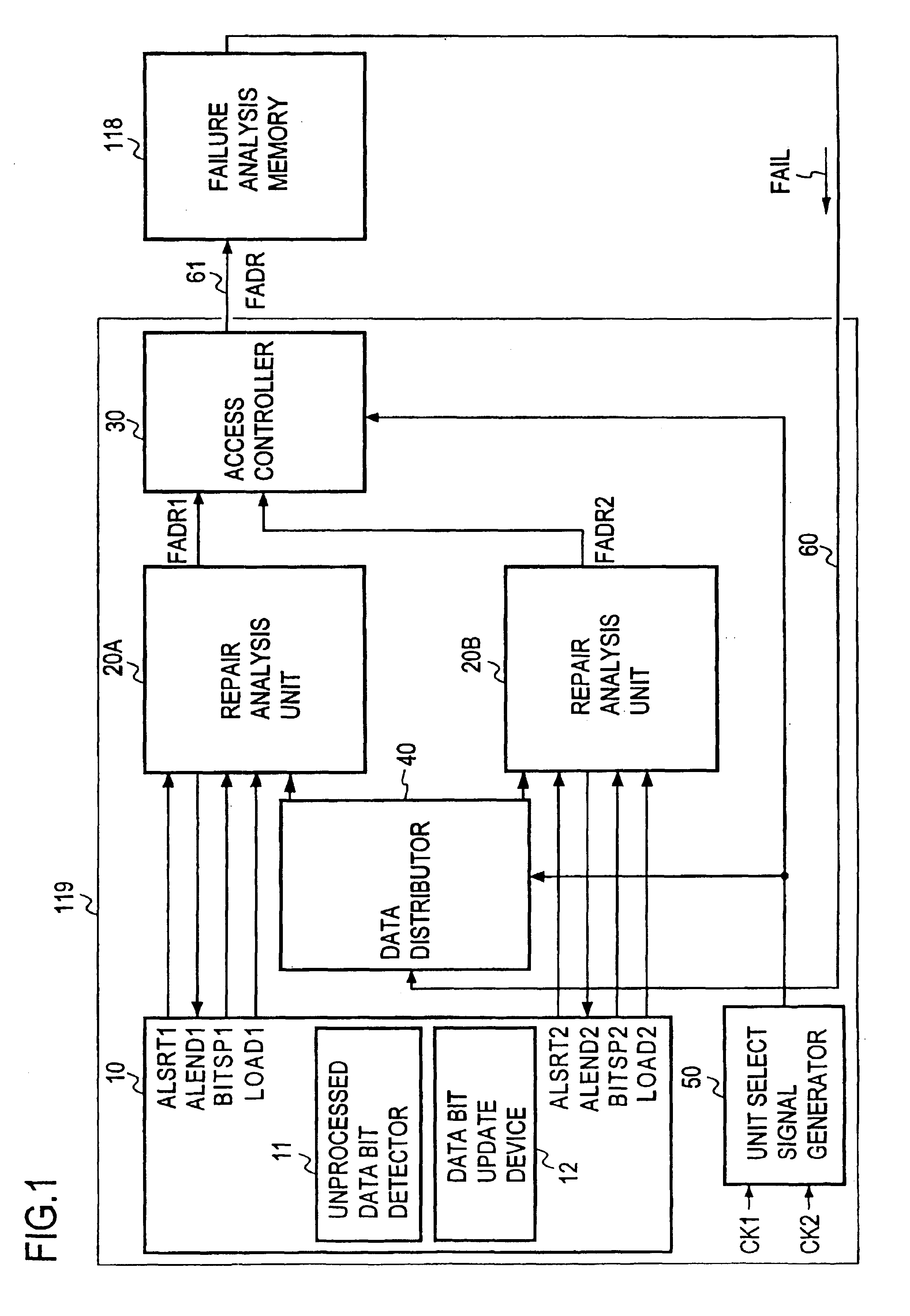

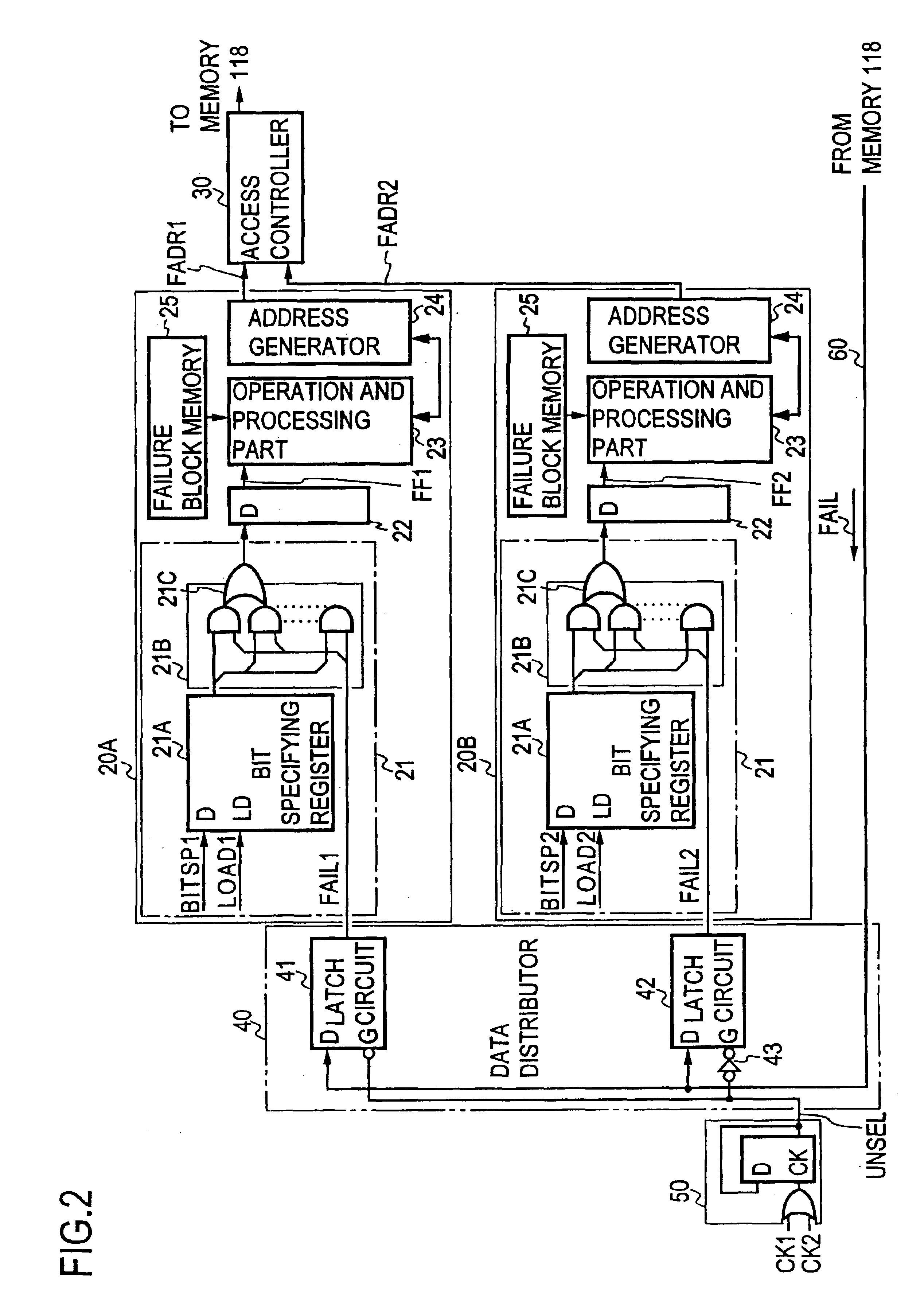

Memory defect redress analysis treating method, and memory testing apparatus performing the method

InactiveUS6907385B2Increase speedFailed analysisDigital computer detailsNuclear monitoringFailure analysisMemory testing

There are provided a failure repair analyzing and processing method and a memory testing apparatus provided with a failure repair analyzing and processing apparatus using this method, that are capable of reducing a time duration required to perform the failure repair analysis and processing for a multi-bit memory having redundancy structure. A plurality of repair analysis units as well as a common failure analysis memory are provided, and these repair analysis units are concurrently operated in parallel with each other, thereby to carry out respective repair analyses and processings for failure memory cells of plural data bits read out from the failure analysis memory in the plural repair analysis units concurrently and in parallel with each other. As a result, a time duration required to execute the failure repair analysis and processing is shortened.

Owner:ADVANTEST CORP

Apparatus and method for managing memory defects

InactiveUS20050022066A1Combination recordingError detection/correctionMemory addressParallel computing

A method and apparatus for managing defects in a memory, wherein the method includes the steps of testing a plurality of memory locations to determine an inoperable memory location and moving a memory address corresponding to the inoperable memory location to a first position in a list of available memory addresses. The method further includes the steps of incrementing an address pointer to a second position in the list of available addresses indicating a next available memory address in the list of available addresses, wherein said step of incrementing an address pointer to a second position operates to remove the memory address stored in the first position from the list of available memory addresses. The apparatus includes a memory having a predetermined number of memory locations for storing data and an address pool having a predetermined number of available memory addresses therein, each of said predetermined number of available addresses corresponding to one of the predetermined number of memory locations. An address pool controller is provided, wherein the address pool controller manages defects in the memory by removing an address from the predetermined number of available addresses when the address is identified as corresponding to an inoperable memory location.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

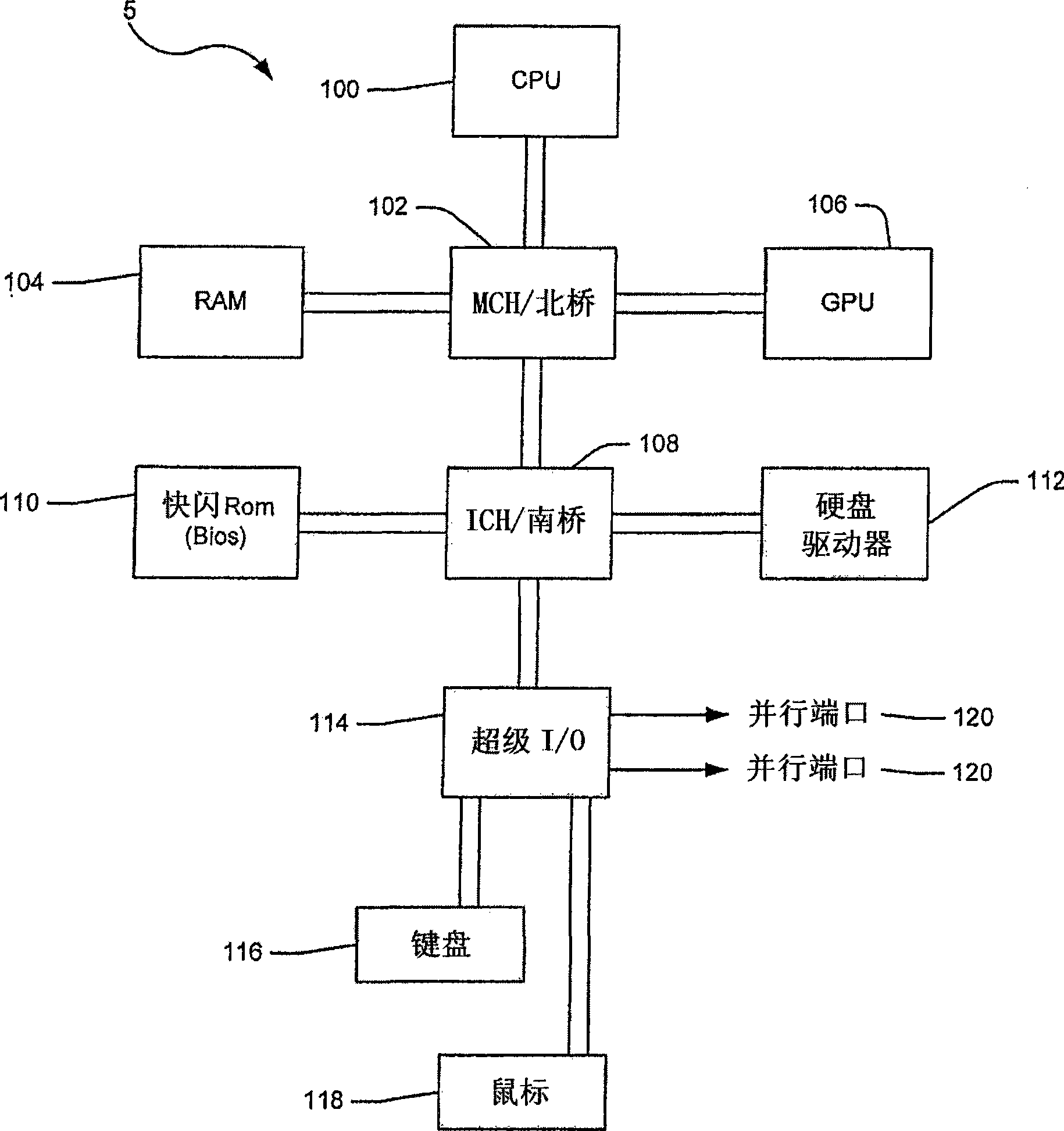

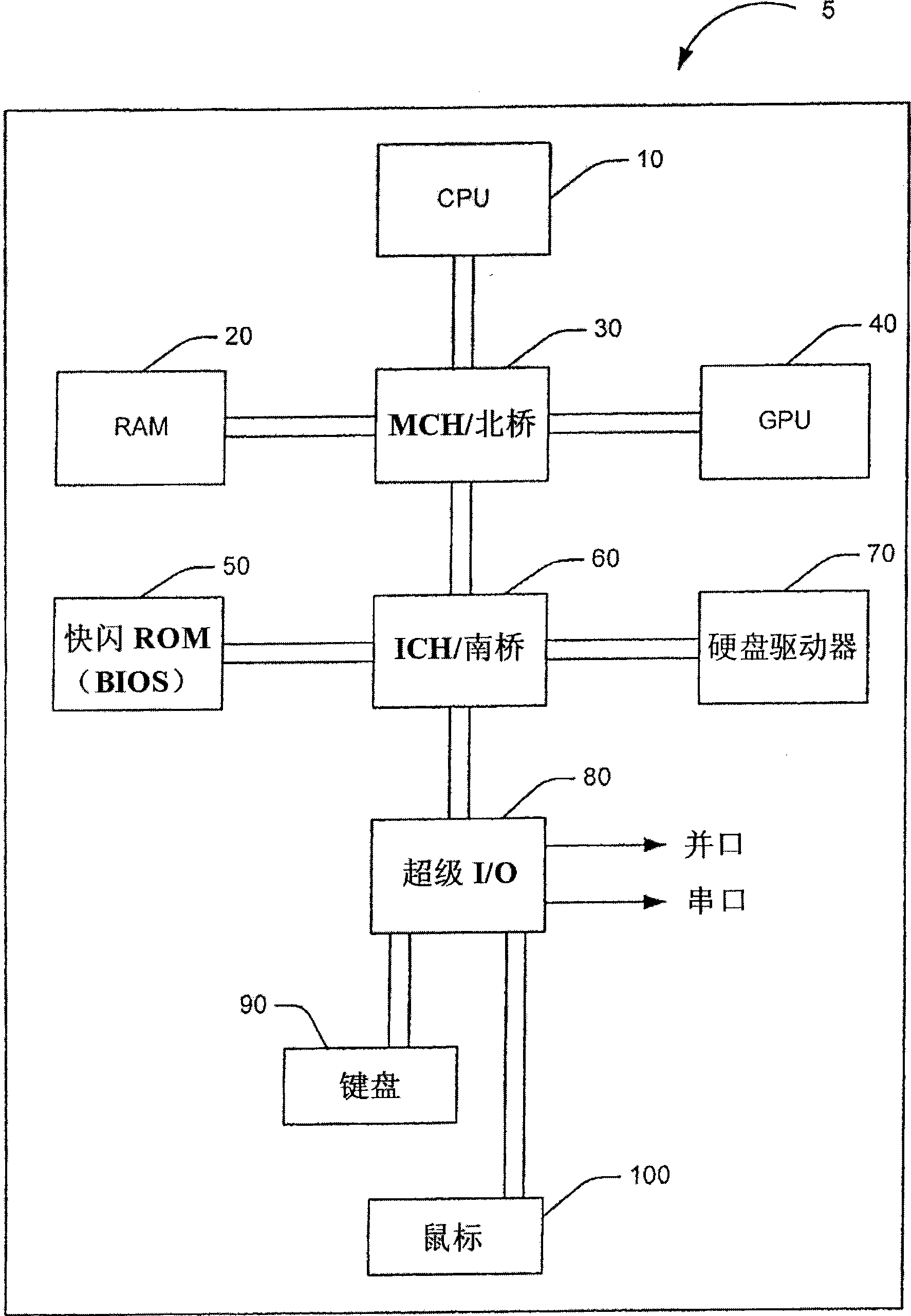

System and method for managing memory errors in an information handling system

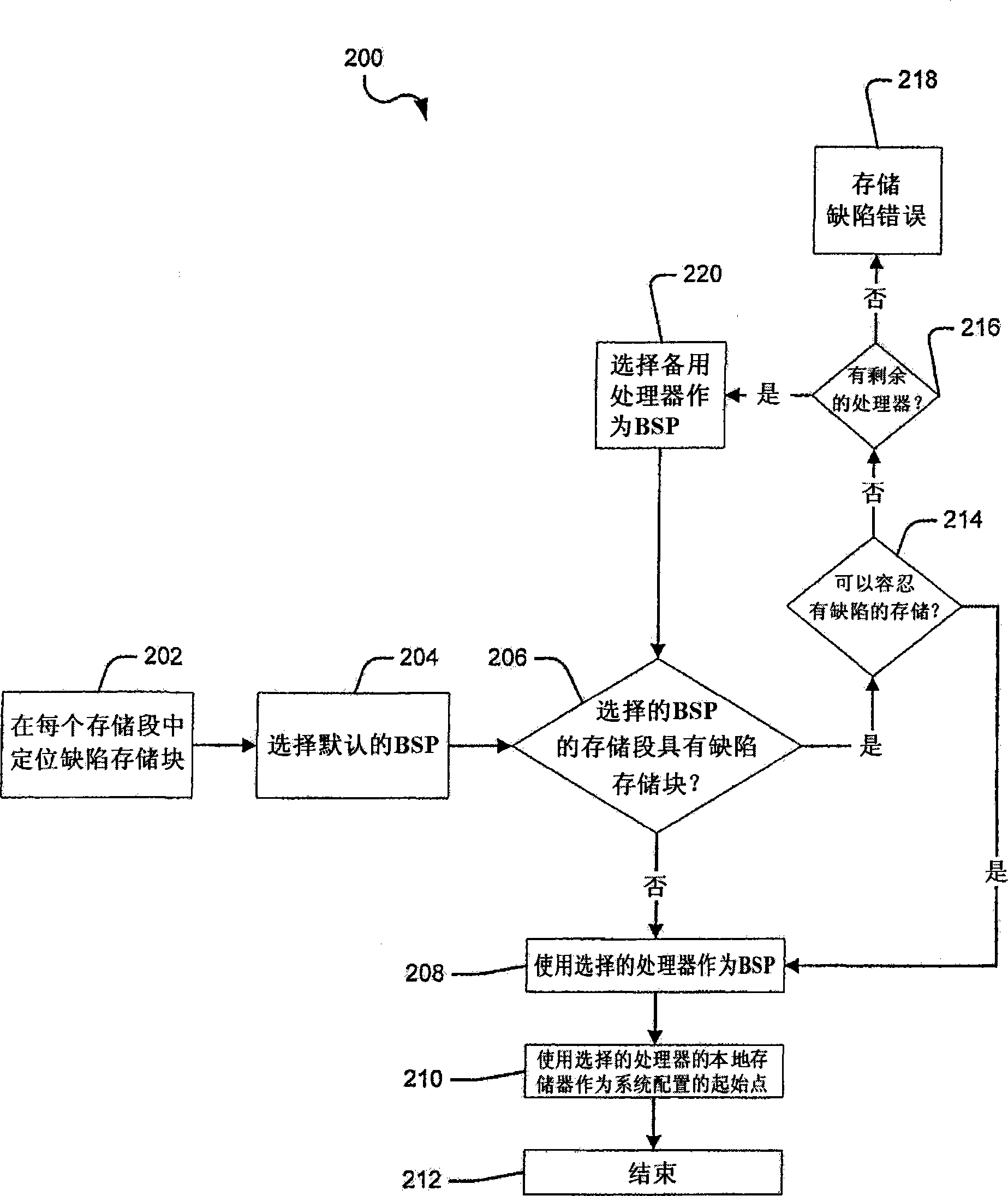

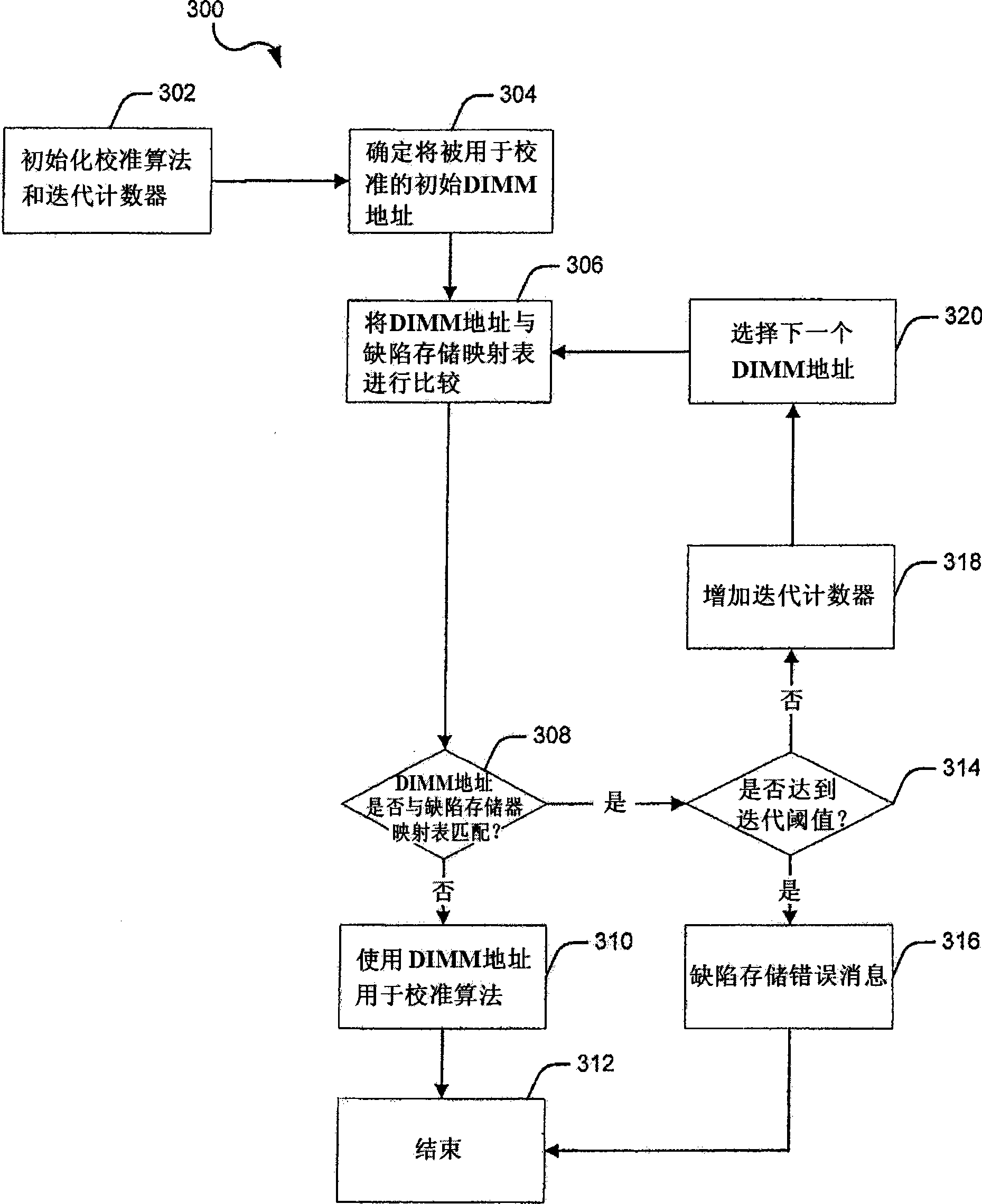

ActiveCN101369240ALow costGuaranteed operabilityDetecting faulty hardware by power-on testFault responseMulti processorHandling system

A method for handling memory defects during the POST phase and memory calibration in single processor and multiprocessor information handling systems is disclosed whereby information regarding the location of a known memory defect is utilized to optimize the performance of an information handling system. Memory defects within system memory are identified and replaced during operation with error free memory space.

Owner:DELL PROD LP

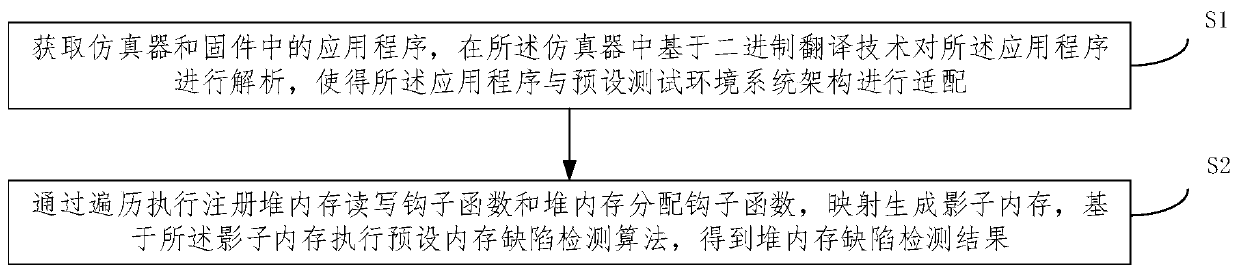

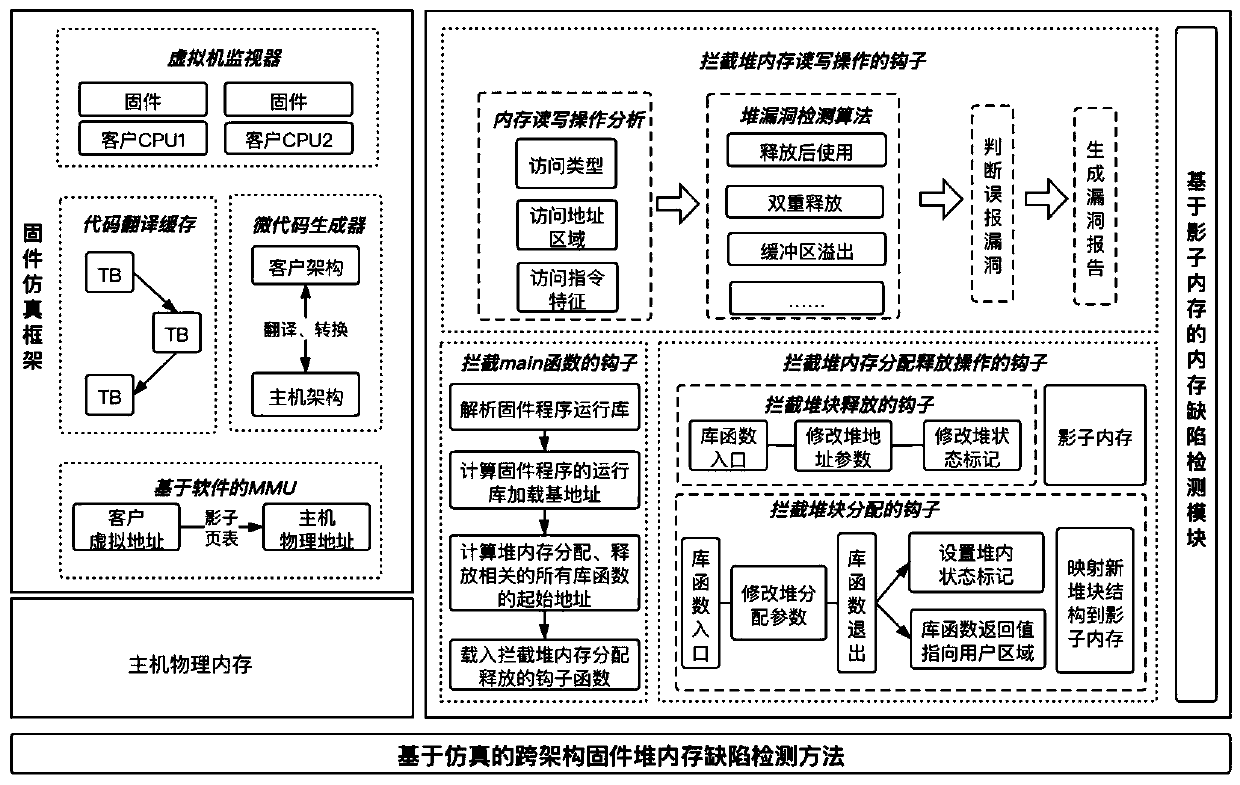

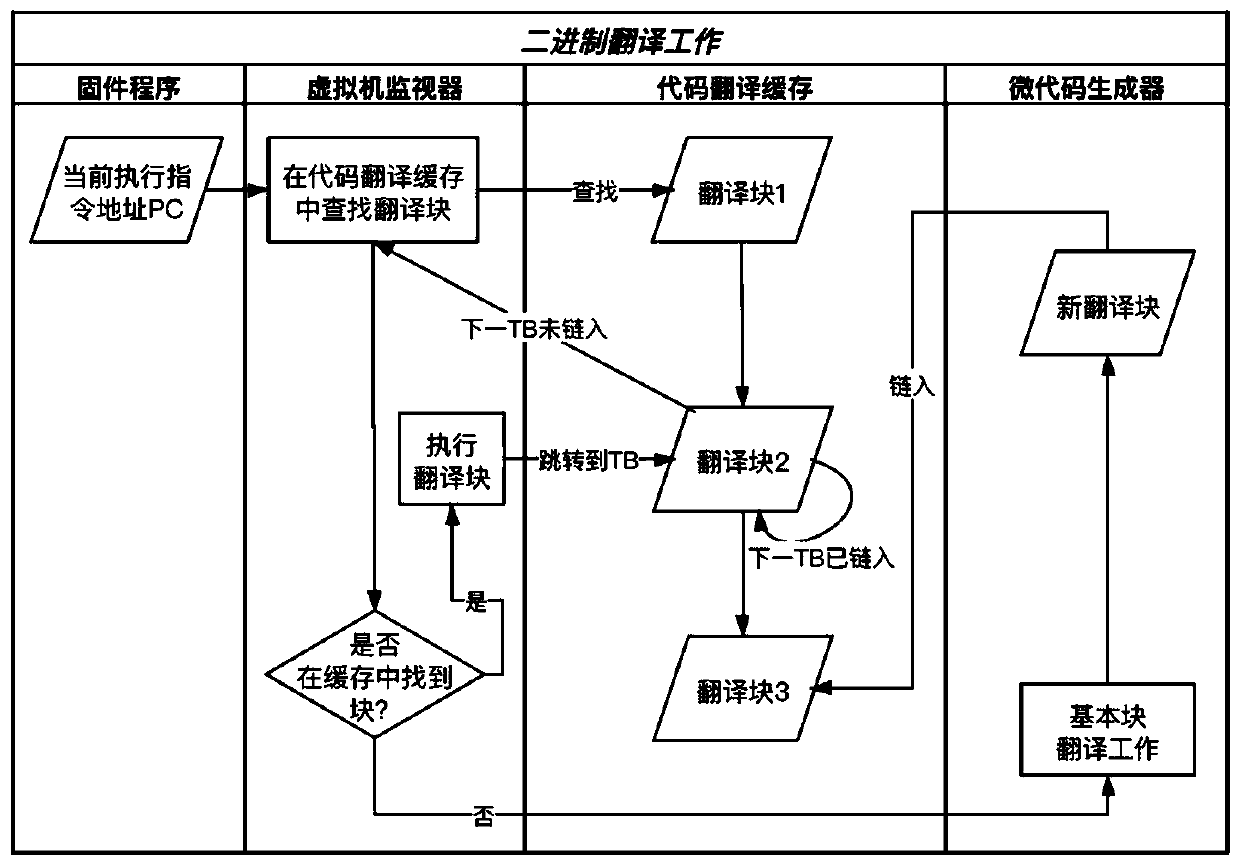

Defect detection method and system for cross-architecture firmware heap memory

ActiveCN111597109AImprove test efficiencyOvercoming unrealistic demandsFunctional testingSoftware testing/debuggingEffective solutionPERQ

The embodiment of the invention provides a defect detection method and system for a cross-architecture firmware heap memory. The method comprises the steps: acquiring an application program in a simulator and firmware, and analyzing the application program in the simulator based on a binary translation technology, so as to enable the application program to be matched with a preset test environmentsystem architecture; and performing mapping to generate a shadow memory by traversing and executing the registered heap memory read-write hook function and the heap memory allocation hook function, and executing a preset memory defect detection algorithm based on the shadow memory to obtain a heap memory defect detection result. According to the embodiment of the invention, the cross-platform characteristic of the execution module is simulated; a detection tool does not need to be deployed into equipment where firmware is located, the unpractical requirement that a traditional memory detection tool needs to be deployed in the device is greatly overcome, the firmware test efficiency is improved, the problem that the storage space of the IoT device is limited is solved, and meanwhile, the memory defect detection module also provides an effective solution for detecting various heap memory defects in a cross-architecture firmware scene.

Owner:TSINGHUA UNIV +1

Integrated circuit and method for testing memory on the integrated circuit

An integrated circuit and method for testing memory on that integrated circuit includes processing logic operable to perform data processing operations on data, and a number of memory units operable to store data for access by the processing logic. A memory test controller is also provided for executing test events in order to seek to detect any memory defects in the number of memory units. The controller includes a storage operable to store event defining information for each of a plurality of test events forming a sequence of test events to be executed, and an interface which, during a single programming operation, receives the event defining information for each of the plurality of test events and causes that event defining information to be stored in the storage. Event processing logic within the controller is then operable, following the single programming operation, to execute the sequence of test events.

Owner:BLUE SKY MEDICAL GROUP +1

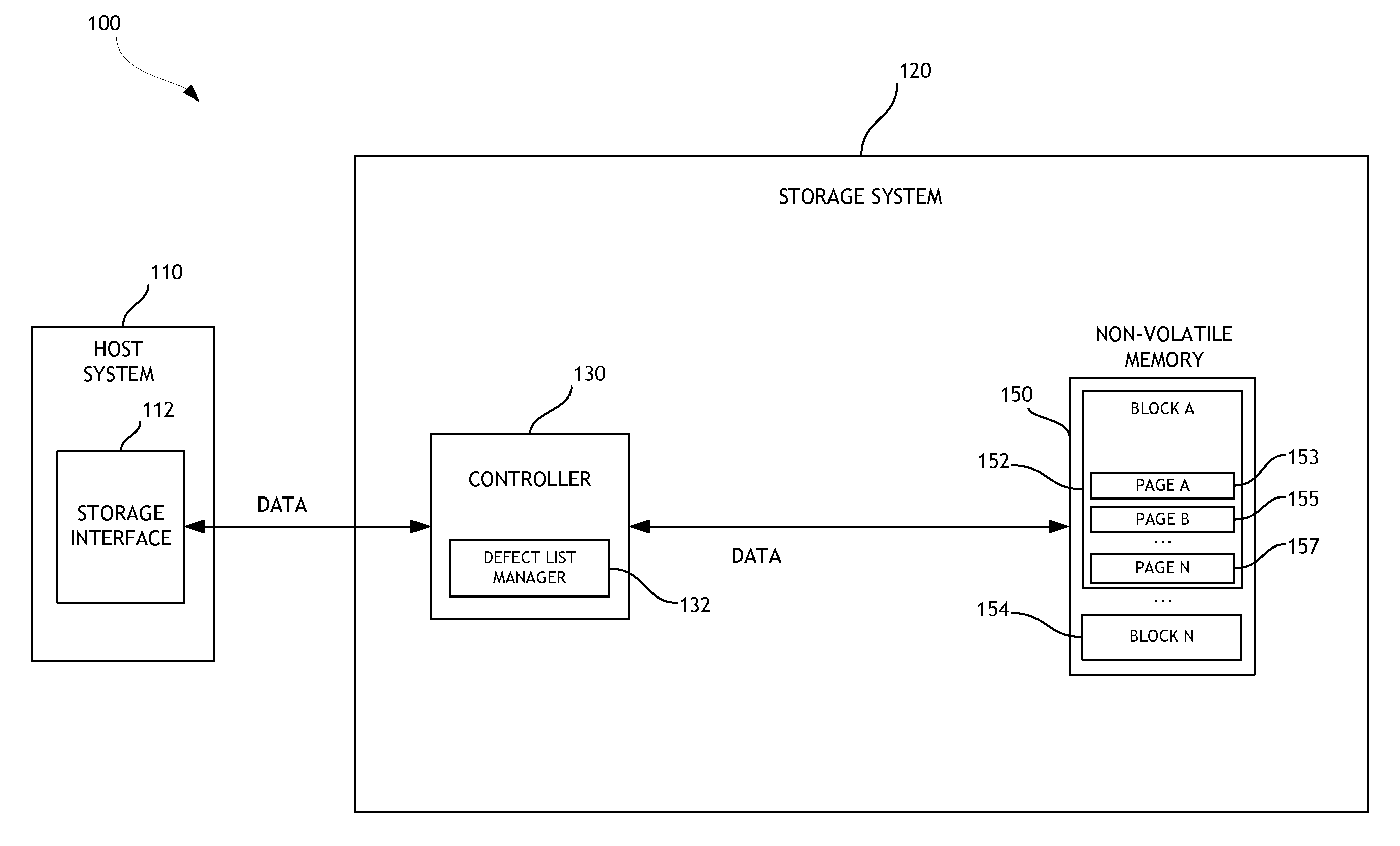

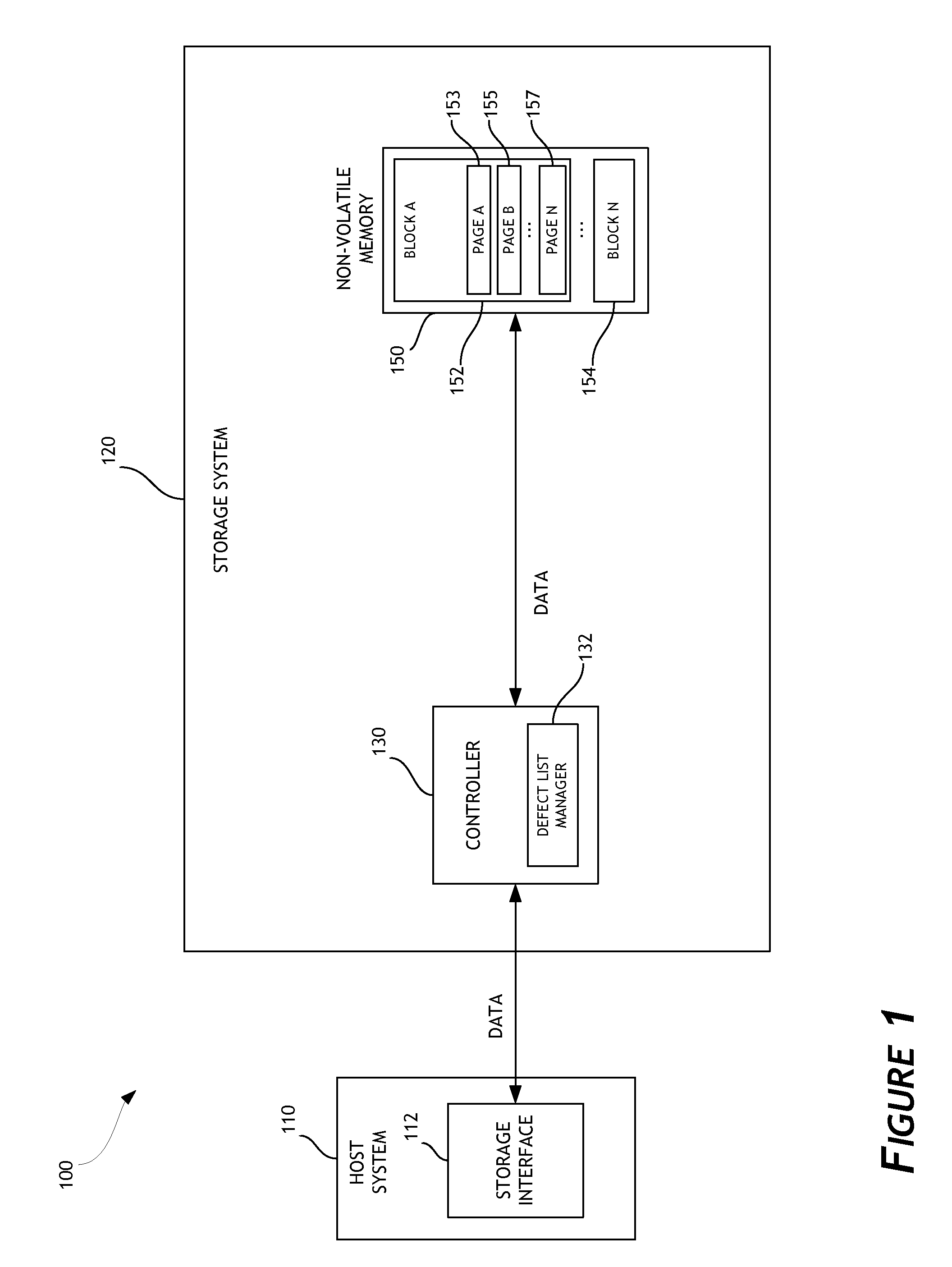

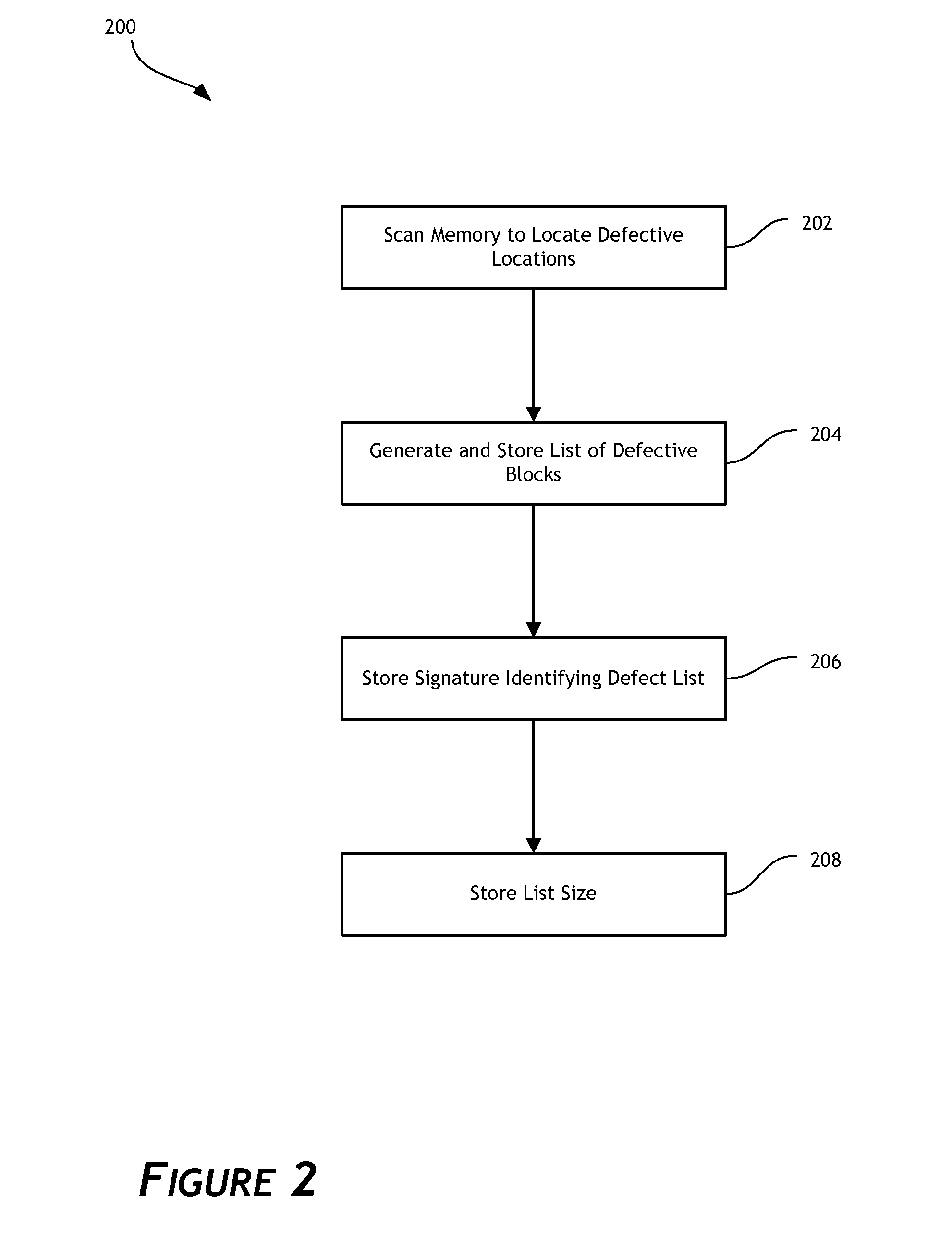

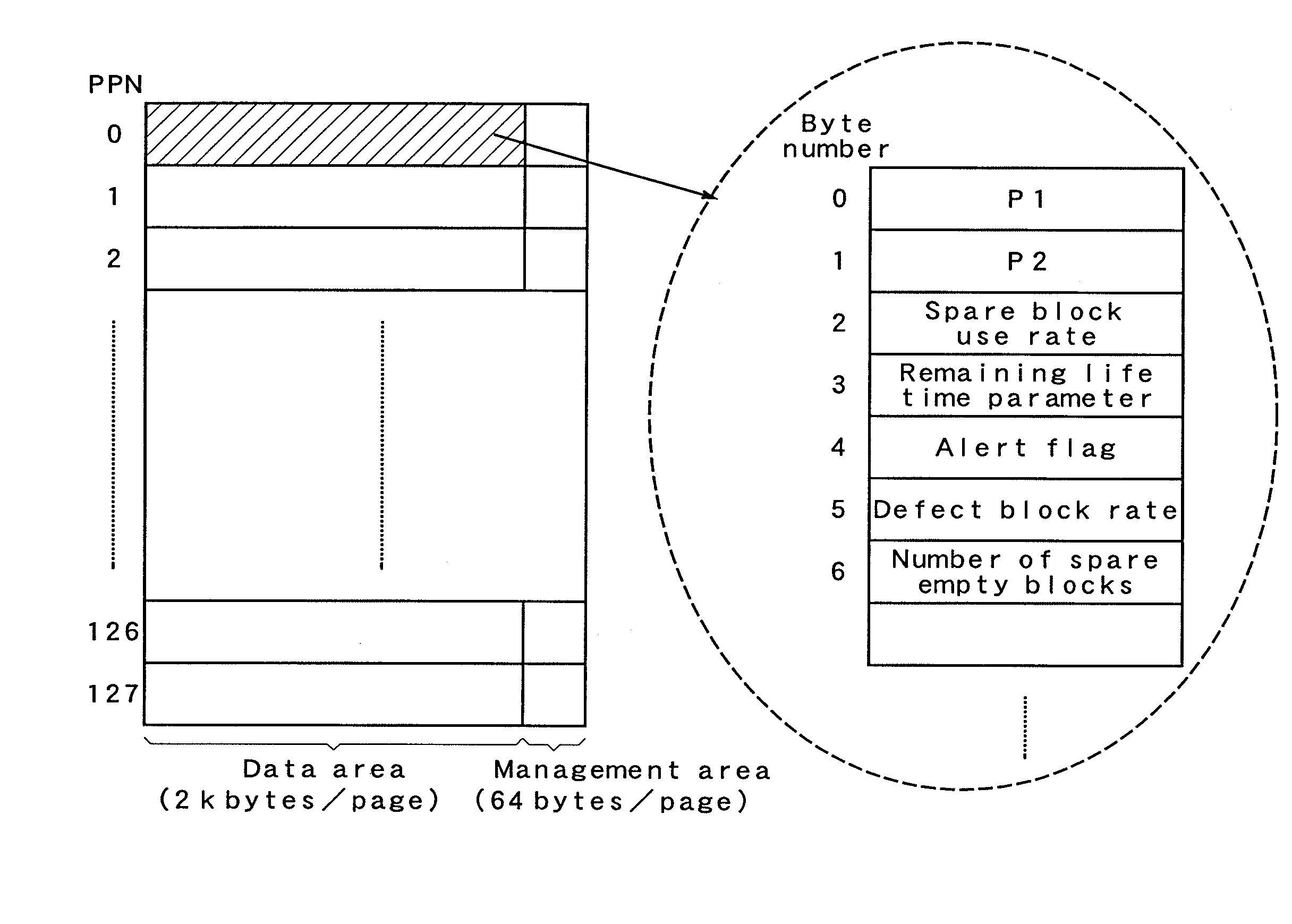

Memory defect management using signature identification

ActiveUS8959416B1Reliable and convenient and quickCode conversionCoding detailsMetadataMemory defects

A non-volatile storage subsystem is disclosed that implements a process for reliably managing memory defect information. In one embodiment, a list indicating the locations of defective memory locations is stored in a non-volatile storage device along with a signature that can be used to identify the location of the stored defect list. The stored list may relate to memory defects that are associated with, or developed in connection with, a manufacturing process of the storage device. The signature may be stored in a metadata portion of one or more pages in which the list is stored.

Owner:WESTERN DIGITAL TECH INC

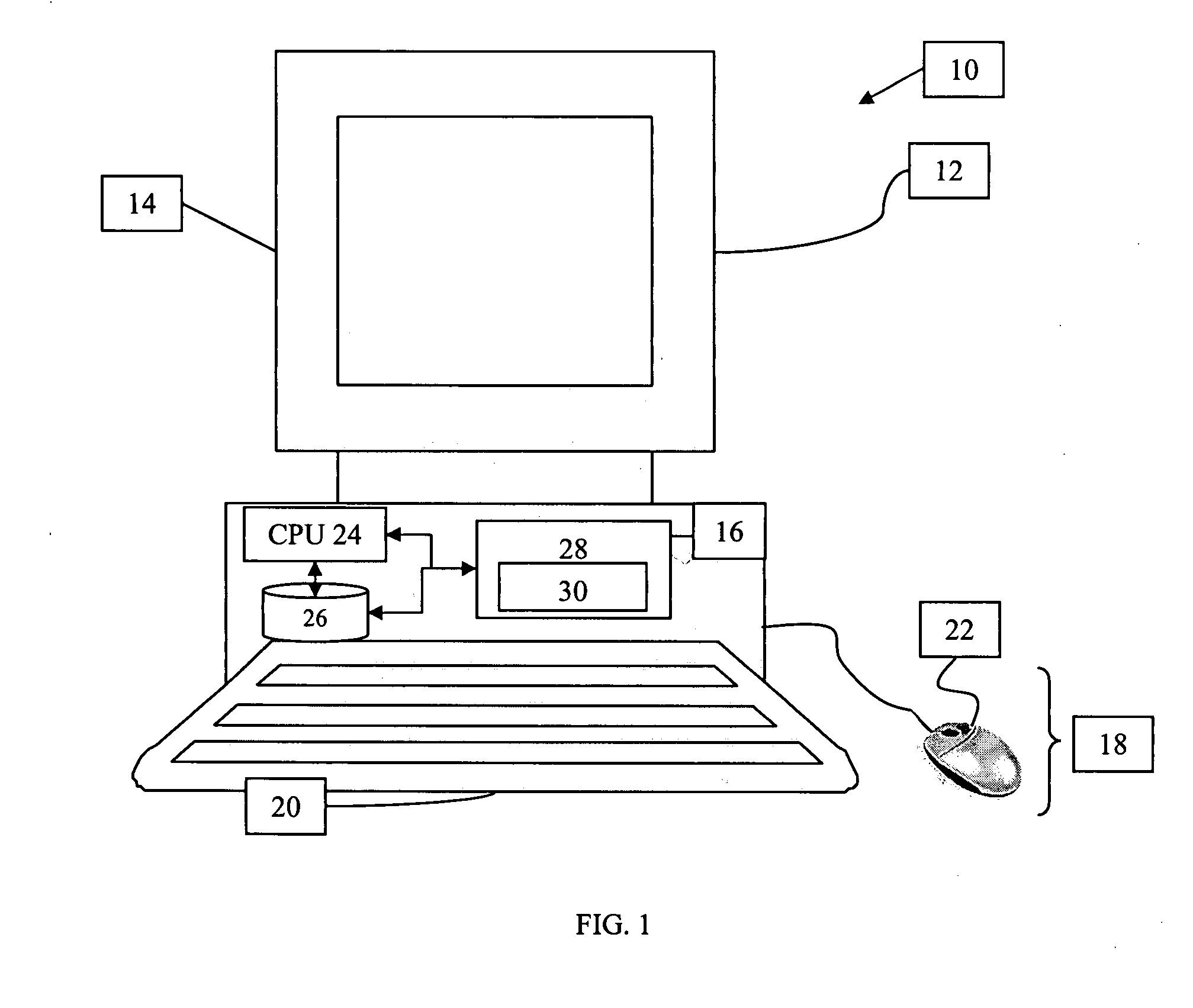

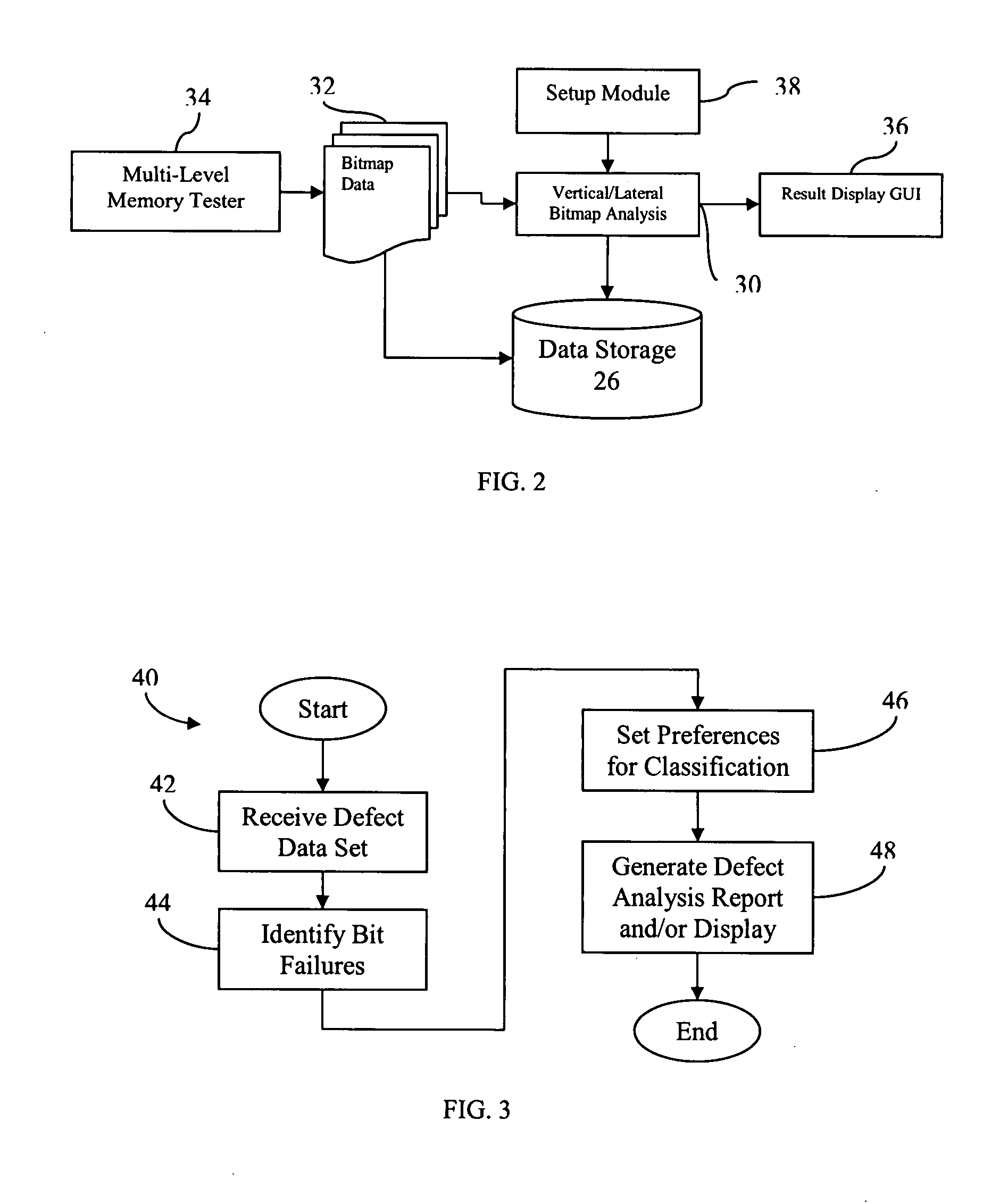

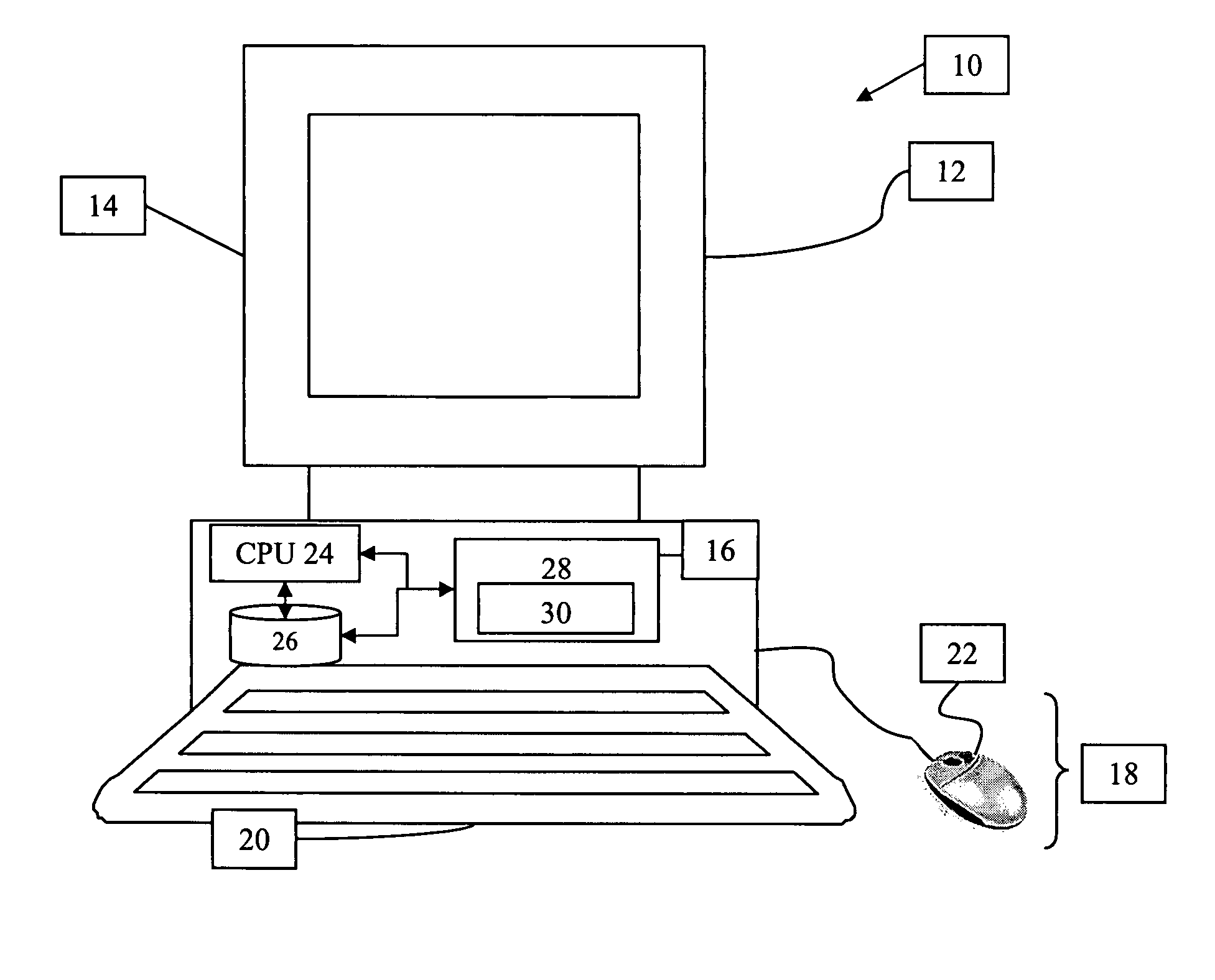

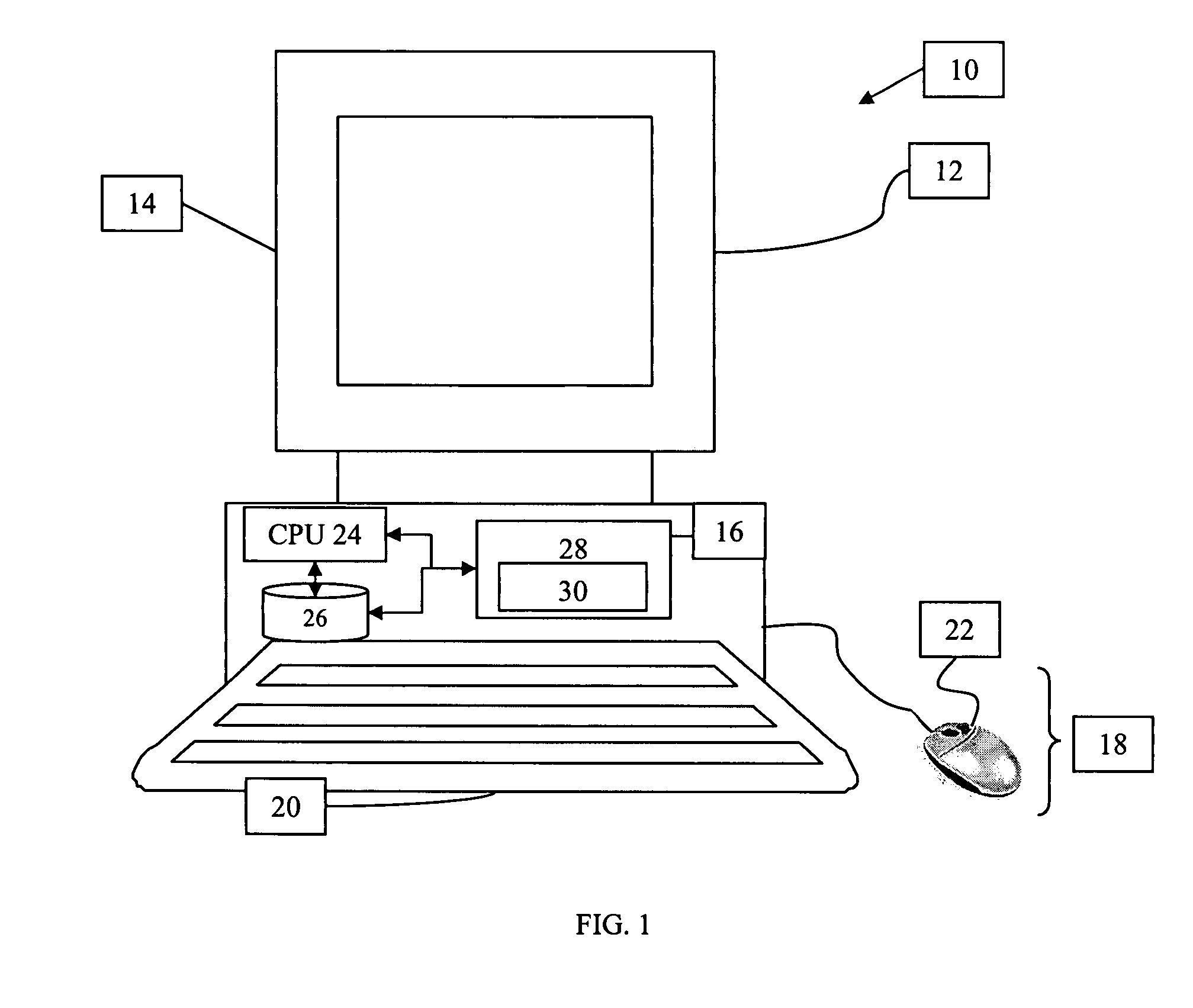

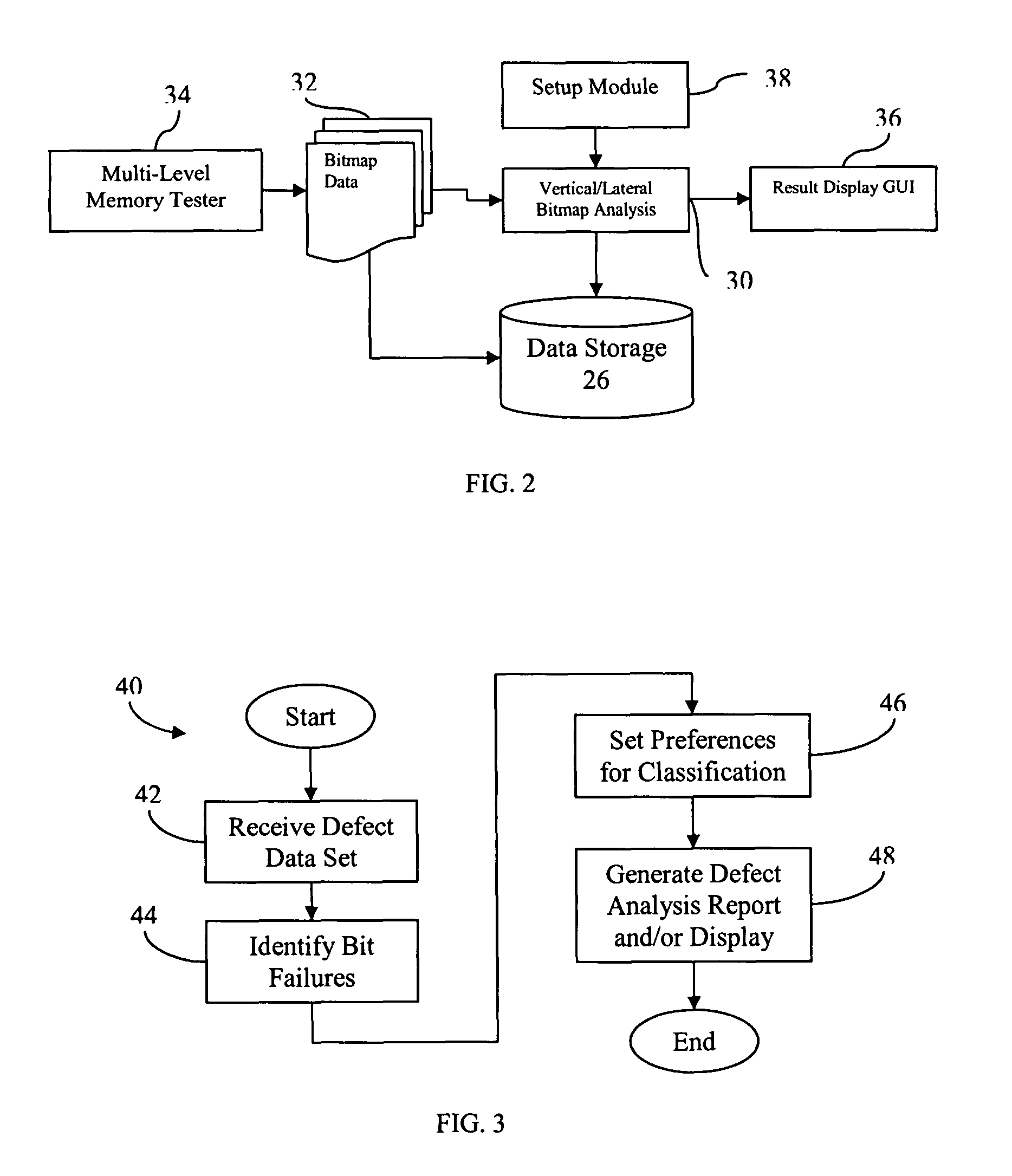

Analysis techniques for multi-level memory

A system and method for defect analysis of multi-level memory cell devices and embedded multi-level memory in system-on-chip integrated circuits are disclosed wherein a defect data set is input into the system. When a defect data set is received, an automated test engineering system running a memory test program analyzes the defect data set to generate one or more fail bit locations and one or more fail states of the memory. The multi-level memory defect analysis system and method then classify failed bits or patterns comprising a vertical fail pattern, whereby after being classified, each memory cell failure vertical fail pattern has three data attributes comprising fail type, a number of fail bits / states, and a sequence of the fail states. The vertical fail pattern may comprise a single fail state or multi-state fail. The multi-state fail may be a continuous-states fail, discontinuous-states fail, or all-state fail. The multi-level memory defect analysis system and method may additionally enable classification of failed bits or patterns comprising a lateral fail pattern. The lateral fail pattern may be a gradual fail pattern, periodic fail pattern, or random fail pattern.

Owner:ONTO INNOVATION INC

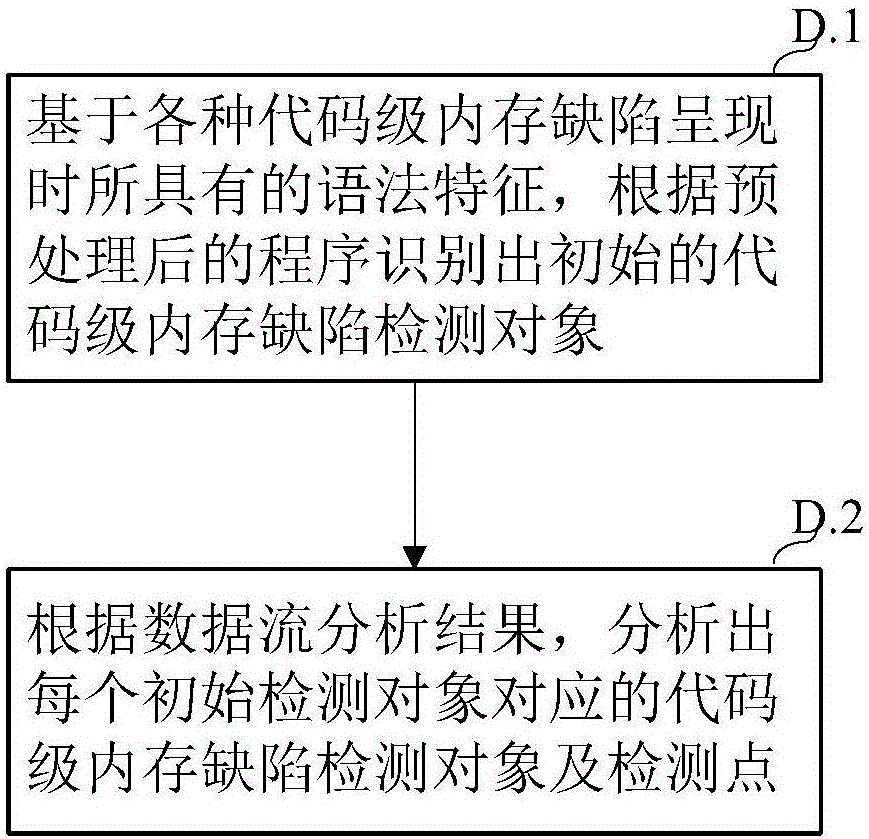

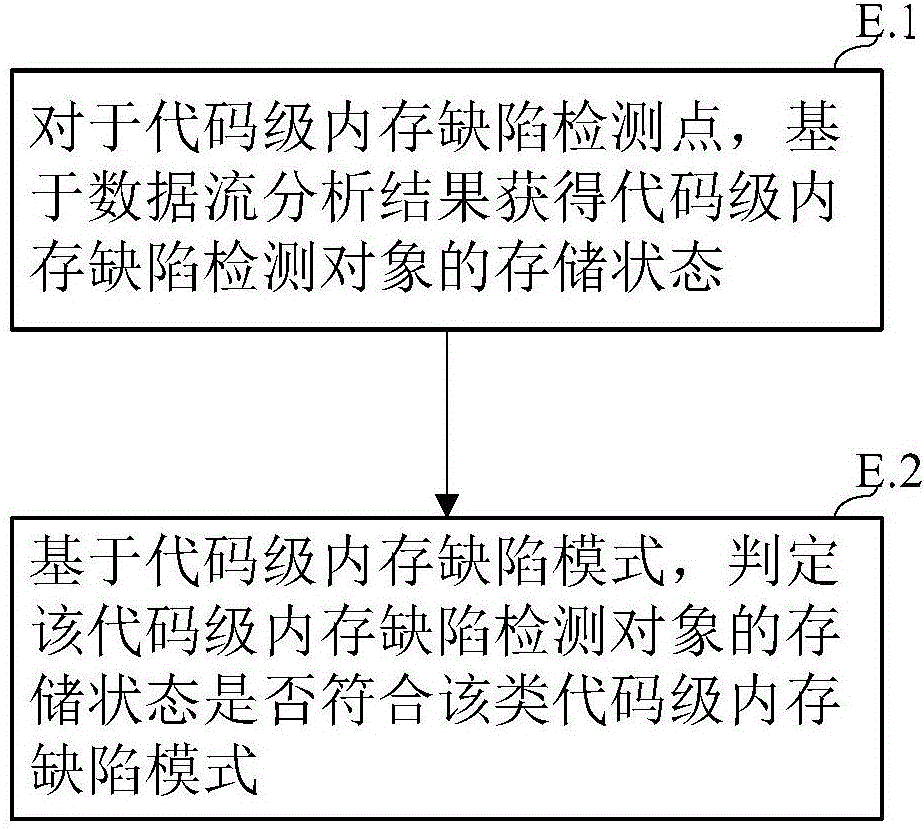

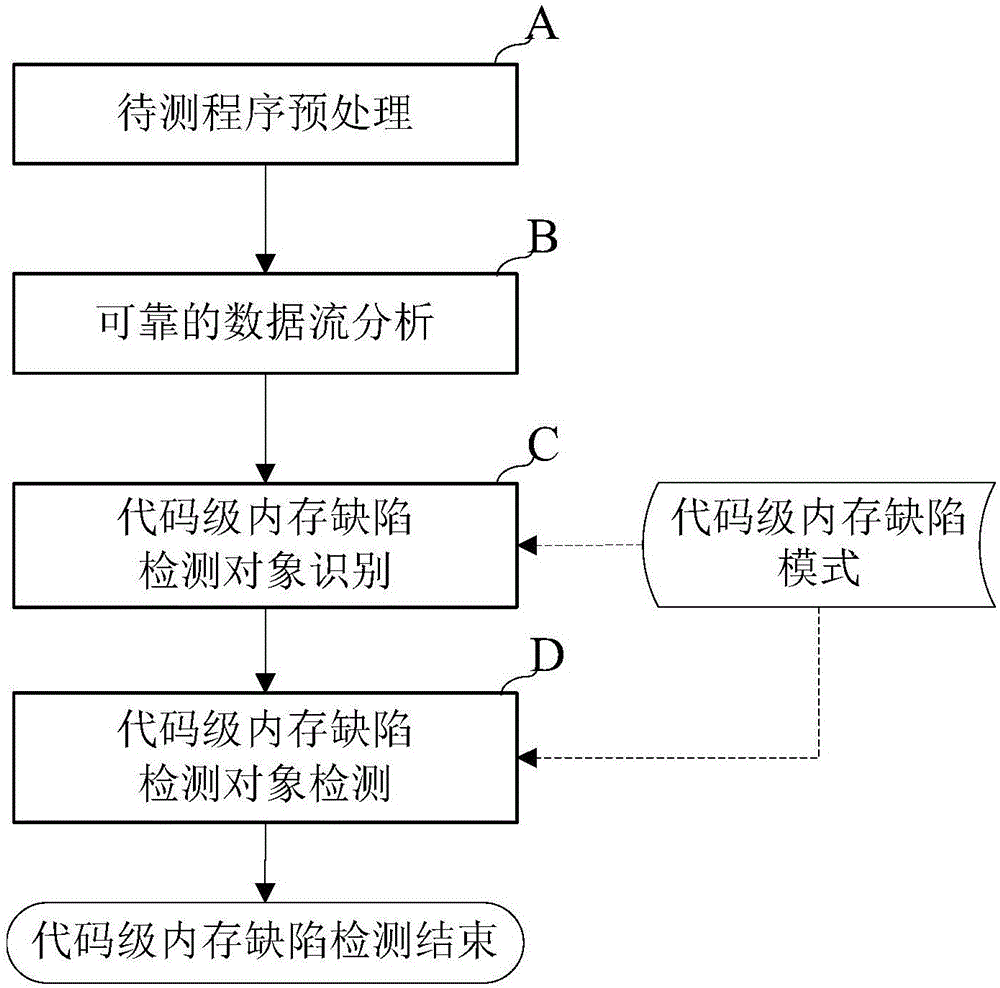

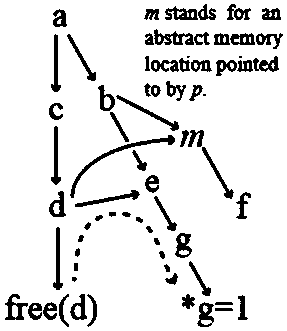

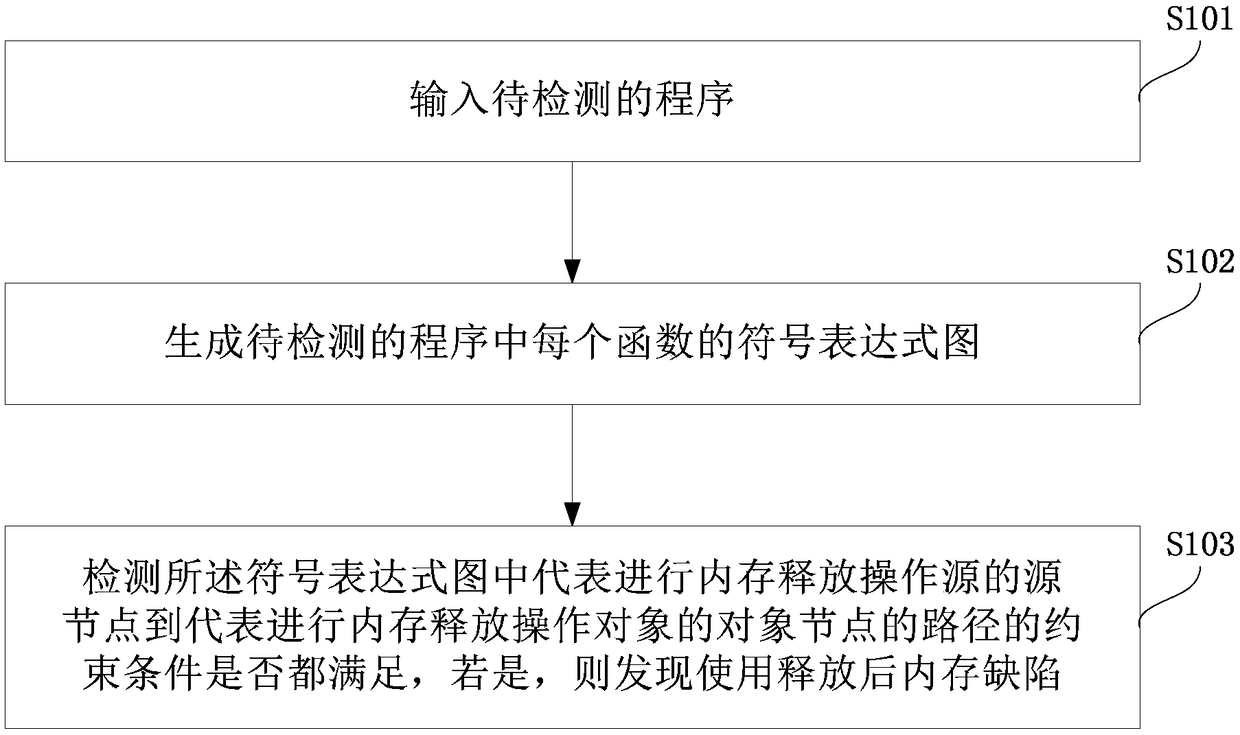

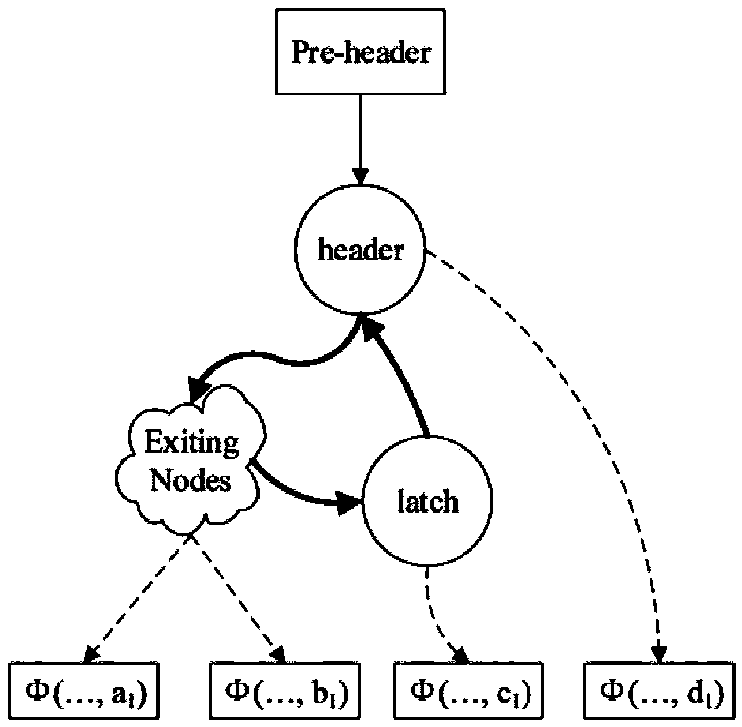

Defect report missing analysis and solving method of code-level memory in program

InactiveCN106681851AEliminate false negativesGuarantee sufficiencyNon-redundant fault processingRedundant data error correctionMemory objectParallel computing

The invention discloses a solution of defect report missing of a code-level memory in a program. The method can achieve detection of all code-level memory defects in programs and comprises the steps that (A) code-level memory defect modes are fully summarized; (B) a storage state of a memory object is comprehensively described, an abstract domain is adopted to express values of expressions, an abstract memory model is adopted to describe various relevance of the expressions; (C) reliable data flow analysis is performed, and an upper approximate value of each memory object value on each program point and various possible relations of the expressions are analyzed and obtained; (D) code-level memory detect detecting objects are completely identified; (E) according to rules of the summarized code-level memory defect modes and data flow analysis results, whether each code-level memory detect detecting object violates correct semantic rules for memory reading and writing or not is accurately detected. By the adoption of the defect report missing analysis and solving method of code-level memories in programs, sufficiency of the detection on the code-level memory defects in the programs can be achieved.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

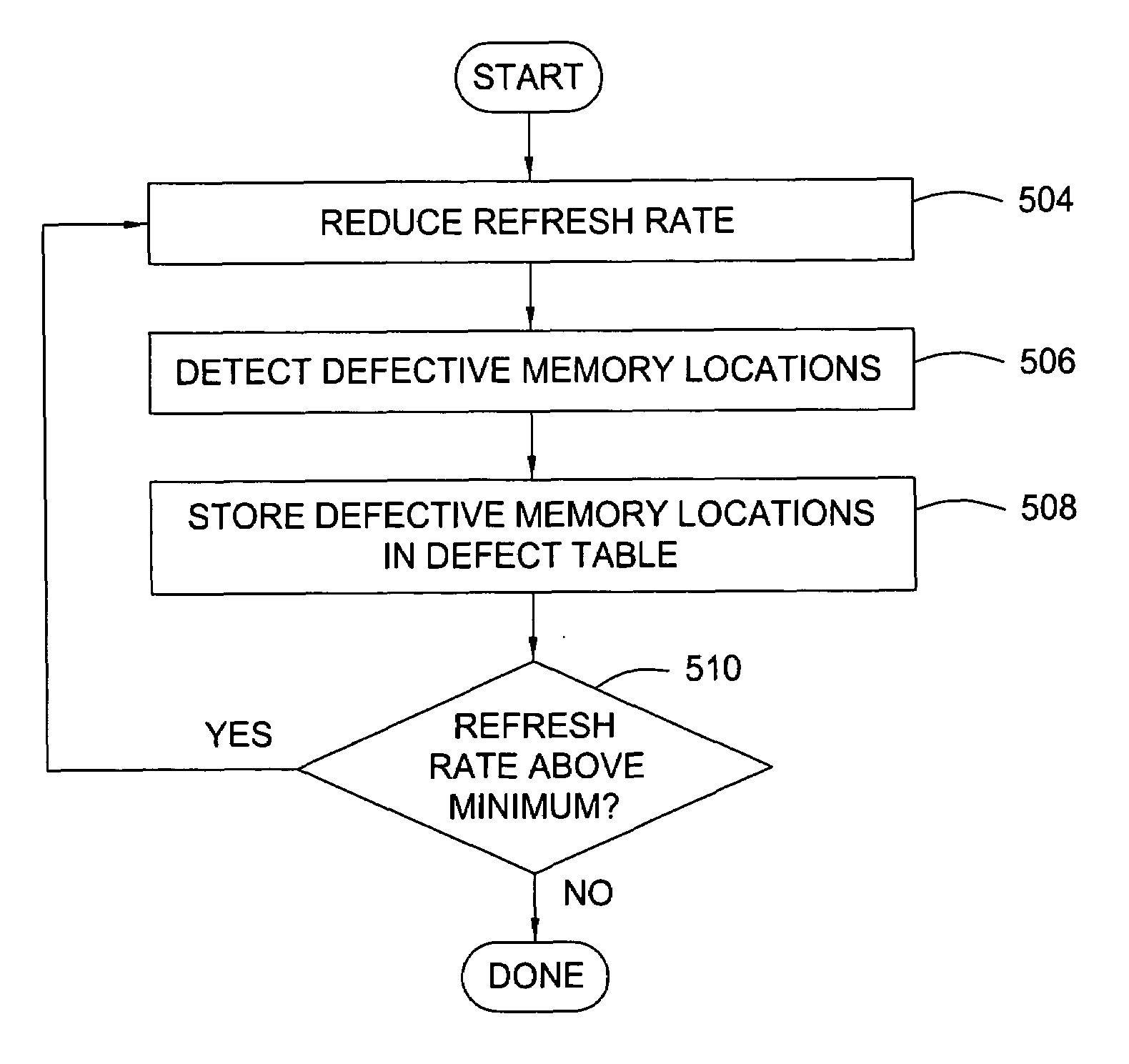

Method for creating a memory defect map and optimizing performance using the memory defect map

ActiveCN101369247ALow costRaise the importanceDetecting faulty computer hardwareStatic storageParallel computingMemory defects

A method for storing a memory defect map is disclosed whereby a memory component is tested for defects at the time of manufacture and any memory defects detected are stored in a memory defect map and used to optimize the system performance. The memory defect map is updated and the system's remapping resources optimized as new memory defects are detected during operation.

Owner:DELL PROD LP

System and method for implementing a memory defect map

ActiveCN101369245AAvoid collisionExtended service lifeDetecting faulty computer hardwareMemory adressing/allocation/relocationMemory defectsInformation handling system

In accordance with the present disclosure, a system and method are herein disclosed for managing memory defects in an information handling system. In an information handling system, a first quantity of memory, such as RAM, may contain defective memory elements. A second quantity of memory is physically coupled to the first quantity of memory and is used to store a memory defect map containing information regarding the location of defective memory elements in the first quantity of memory. The memory defect map may then be referenced by the BIOS or the operating system to preclude use of regions of memory containing defective memory elements.

Owner:DELL PROD LP

Memory shortage diagnostic method using failure mode as guide and its system

InactiveCN1598780AEasy to detect immediatelyEasy to detect problems immediatelyRedundant hardware error correctionMemory defectsDiagnostic methods

The invention relates to an approach of memory defect diagnoses which uses failure mode as direction. It conducts analyzing and comparing failure mode and disable mode. Through comparing with defect database built previously, practical problems in memory making and design can be found according to possible defect in different failure modes defined in the database.

Owner:NASOFORM INC +1

A detection method, system and device using the released memory and a storage medium

ActiveCN109426723AEfficient detectionReduce false positivesError detection/correctionSoftware engineeringMemory defectsData dependency

The invention provides a detection method, system and device using the released memory and a storage medium. The method comprises the following steps of inputting a program to be detected; generatinga symbolic expression diagram for each function in the program, wherein a symbolic expression graph consists of nodes and edges that connect nodes, the node includes a value node and an operator node,and the edge includes a data dependency edge and a control dependency edge, wherein the data dependency edge is a directional edge connecting the node to a value node with which it has a direct datadependency relationship, and the control dependency edge is a directional edge connecting the variable to the condition when there is a condition defining the variable; detecting whether the constraint conditions of the path from the source node of the symbolic expression graph to the object node of the object in which the memory release operation is performed are met, If so, finding a memory defect after the use of the released memory. The invention can efficiently detect the defect after the use of the released memory by utilizing the judgment of the path and the path constraint conditions in the symbol expression diagram.

Owner:SHENZHEN QIANHAI SOURCEBRELLA INC LTD

Memory defect detection and self-repair technique

According to some embodiments, a memory device having multiple memory units includes one or more redundant memory units. Upon detection of an electrical characteristic indicating a failing memory unit, one of the redundant memory units is used to replace the failing memory unit. Detection of failing memory units may be via current, voltage and / or resistance monitoring. If the electrical characteristic monitored exceeds a predetermined threshold, a memory unit is considered failing. The failing memory unit is removed from further use. The redundant memory unit is programmed to be accessible at the memory address of the removed memory unit. Replacement occurs automatically (that is, without user intervention).

Owner:INTEL NDTM US LLC

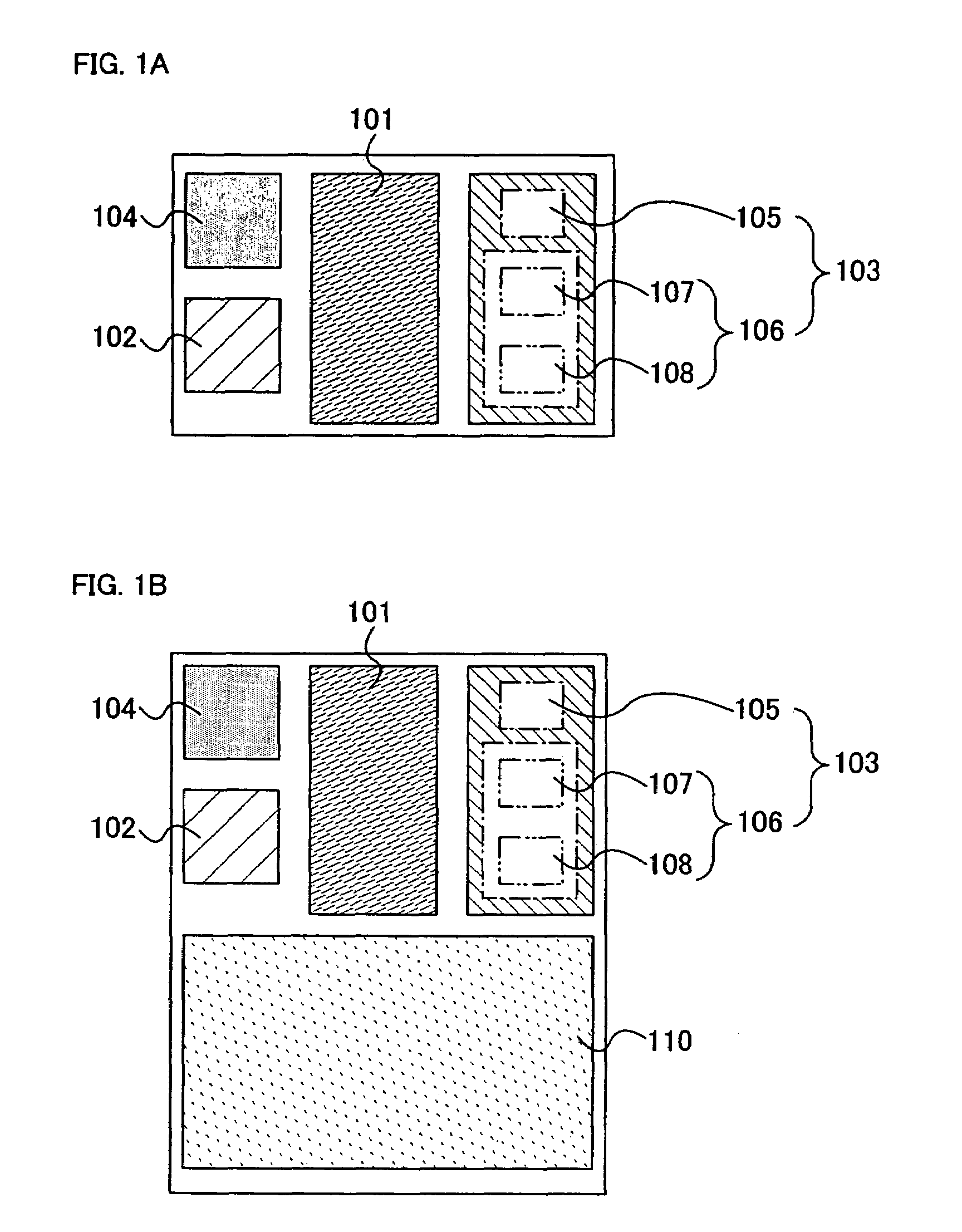

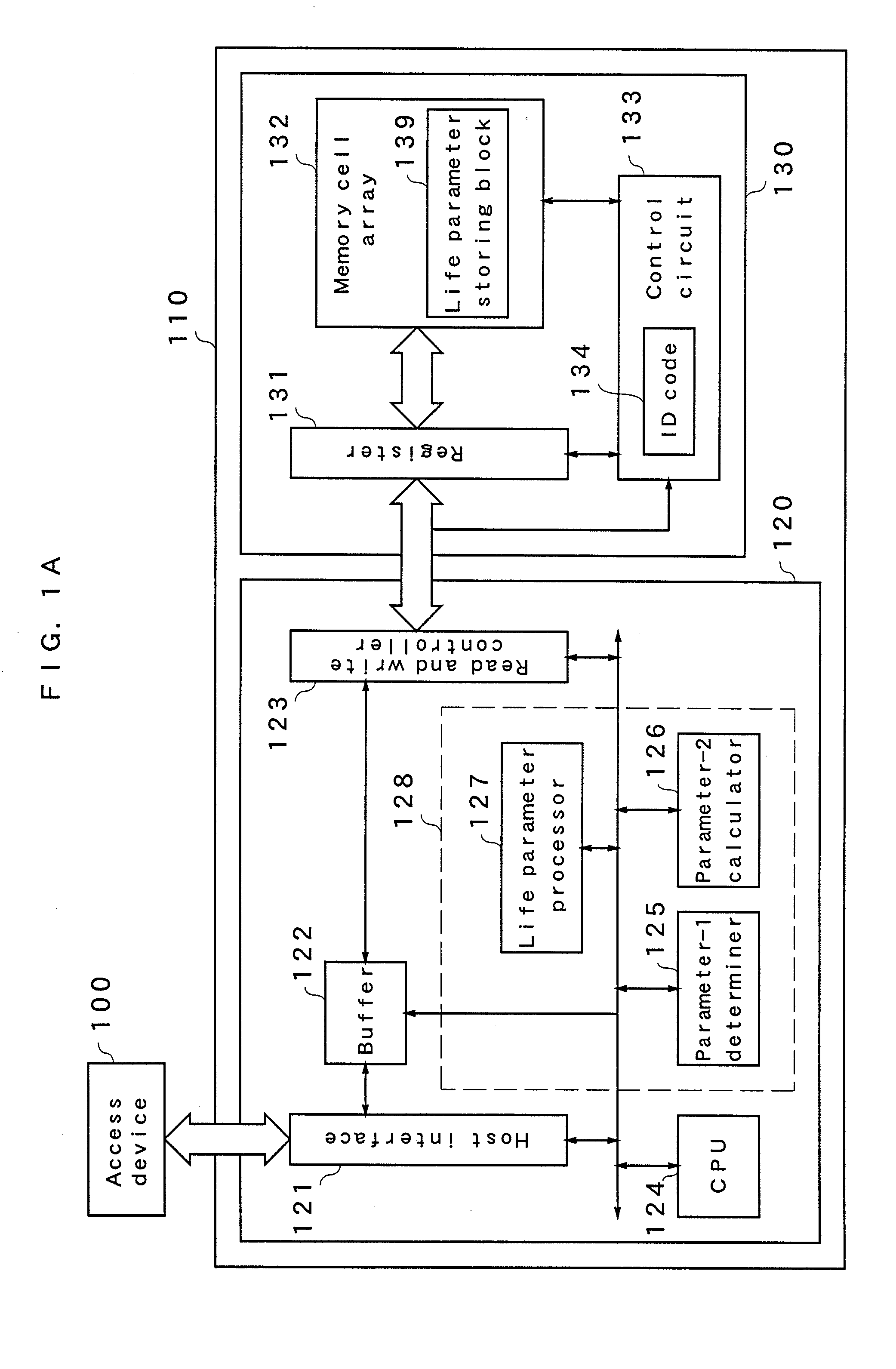

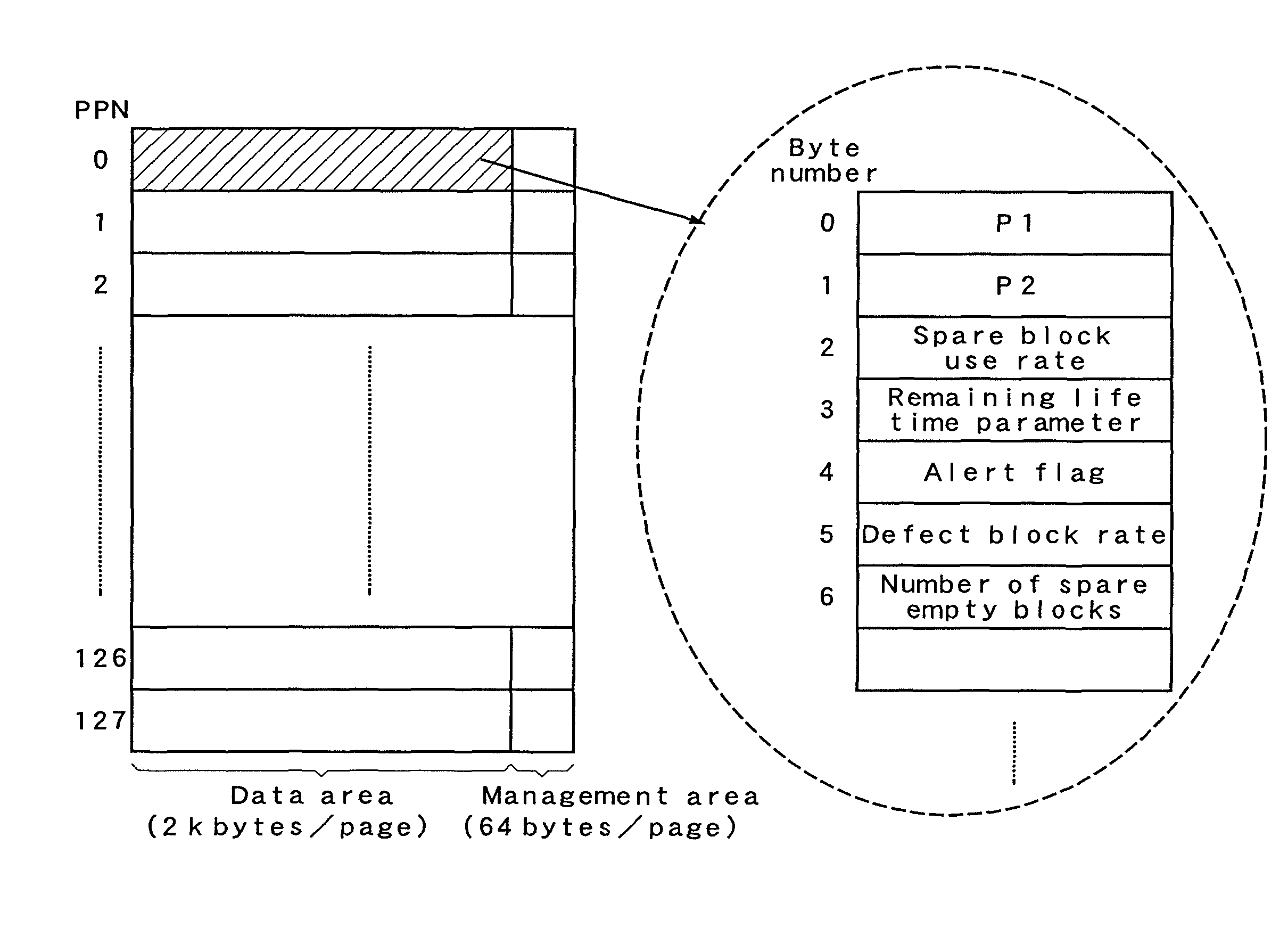

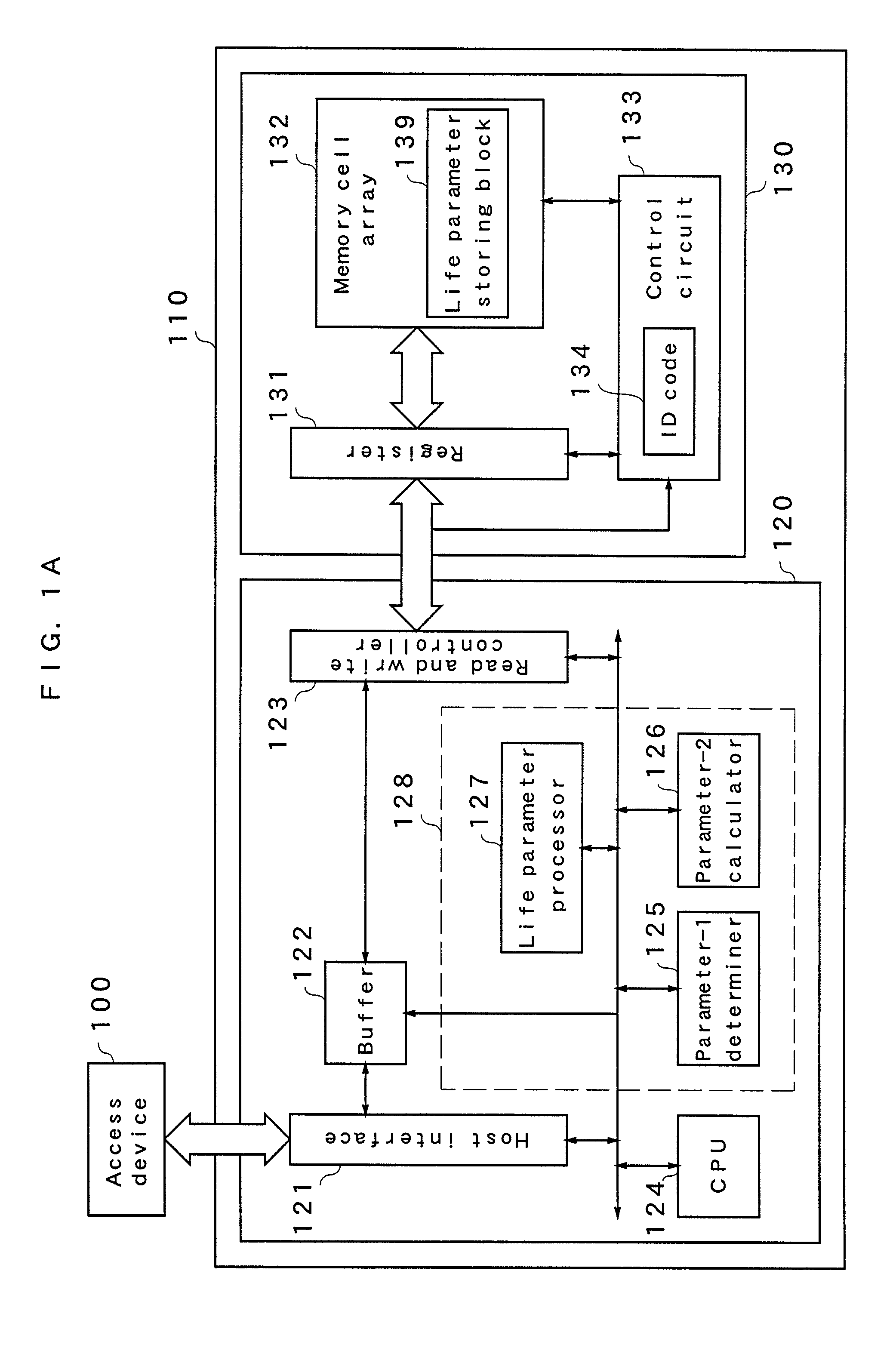

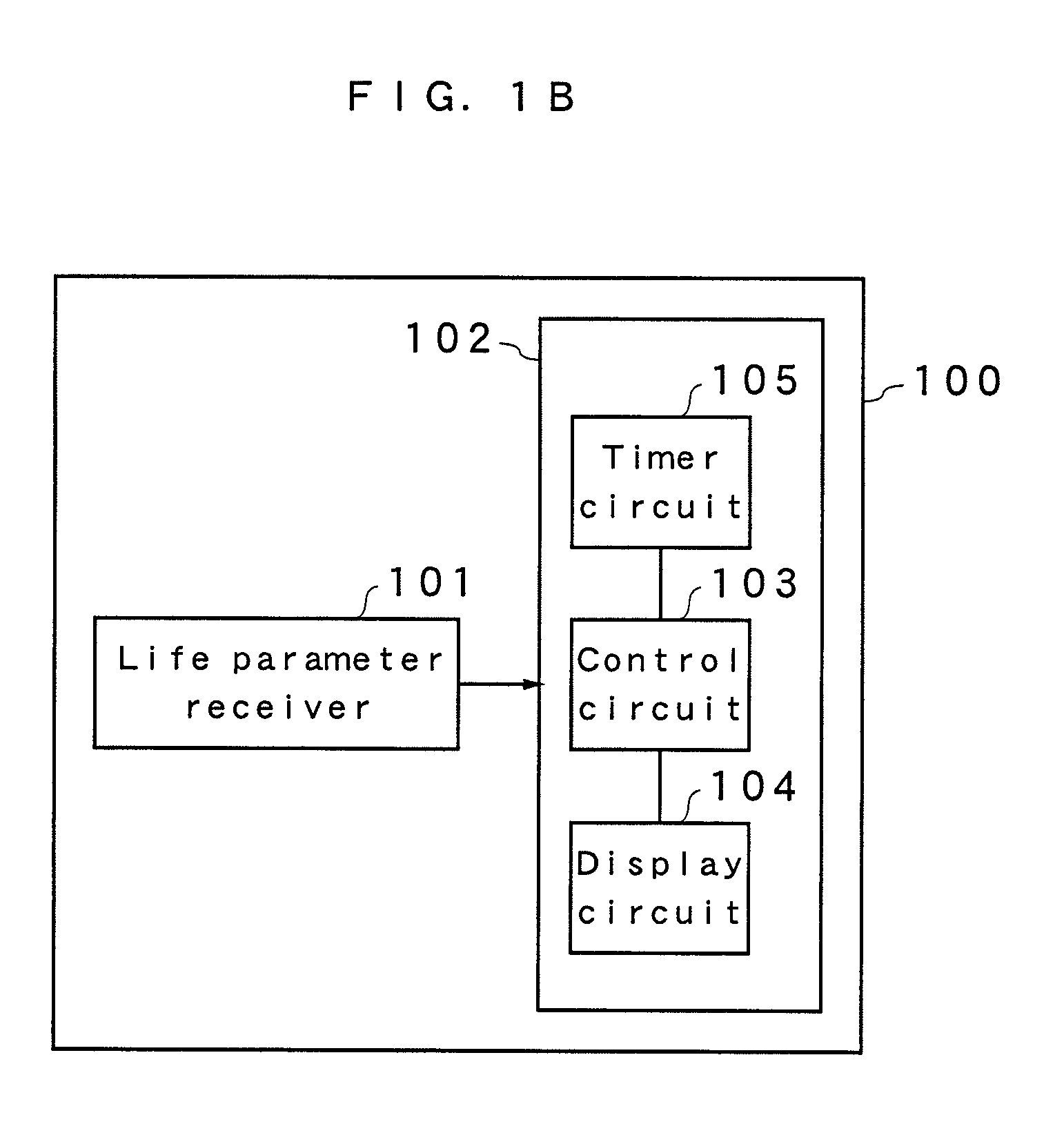

Nonvolatile memory device, nonvolatile memory system, and defect management method for nonvolatile memory device

ActiveUS20100223510A1Accurately and easily recognizeElectronic circuit testingVolume/mass flow measurementEmbedded systemNon-volatile memory

Owner:PANASONIC CORP

Analysis techniques for multi-level memory

A system and method for defect analysis of multi-level memory cell devices and embedded multi-level memory in system-on-chip integrated circuits are disclosed wherein a defect data set is input into the system. When a defect data set is received, an automated test engineering system running a memory test program analyzes the defect data set to generate one or more fail bit locations and one or more fail states of the memory. The multi-level memory defect analysis system and method then classify failed bits or patterns comprising a vertical fail pattern, whereby after being classified, each memory cell failure vertical fail pattern has three data attributes comprising fail type, a number of fail bits / states, and a sequence of the fail states. The vertical fail pattern may comprise a single fail state or multi-state fail. The multi-state fail may be a continuous-states fail, discontinuous-states fail, or all-state fail. The multi-level memory defect analysis system and method may additionally enable classification of failed bits or patterns comprising a lateral fail pattern. The lateral fail pattern may be a gradual fail pattern, periodic fail pattern, or random fail pattern.

Owner:ONTO INNOVATION INC

Shift redundancy encoding for use with digital memories

A computer system is disclosed that includes a memory, a memory defect map, and a shift encoder. The memory includes a plurality of bits and a plurality of input / output ports for accessing the plurality of bits. The memory defect map specifies positions of defective ones of the plurality of bits. The shift encoder encodes positions of defective ones of the plurality of bits in a shift encoding. The shift encoding includes a shift redundancy record representing positions of transitions between functional bits and defective bits in the memory, and a hints record representing numbers of bits in sets of consecutive defective bits in the memory.

Owner:HEWLETT PACKARD DEV CO LP

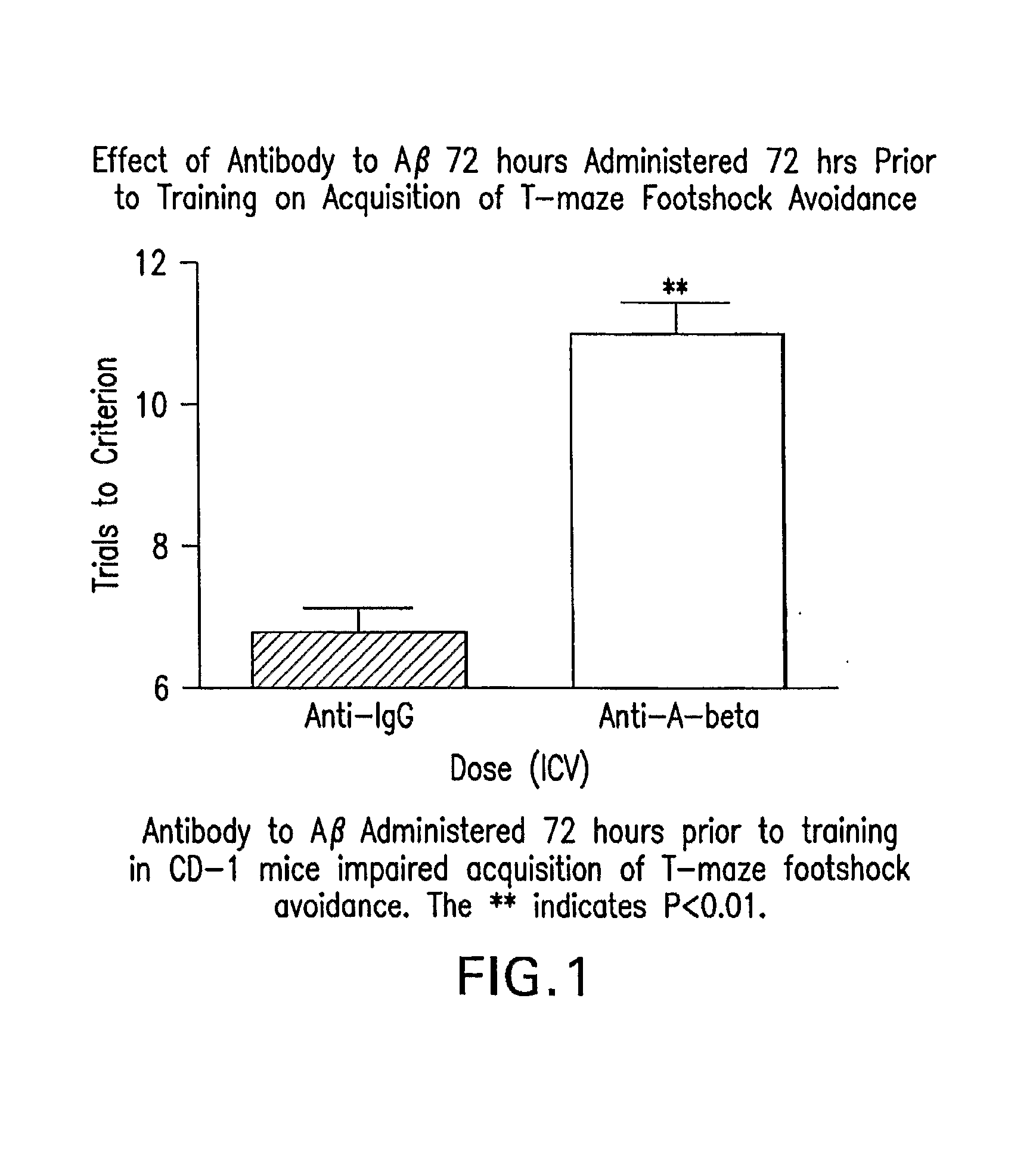

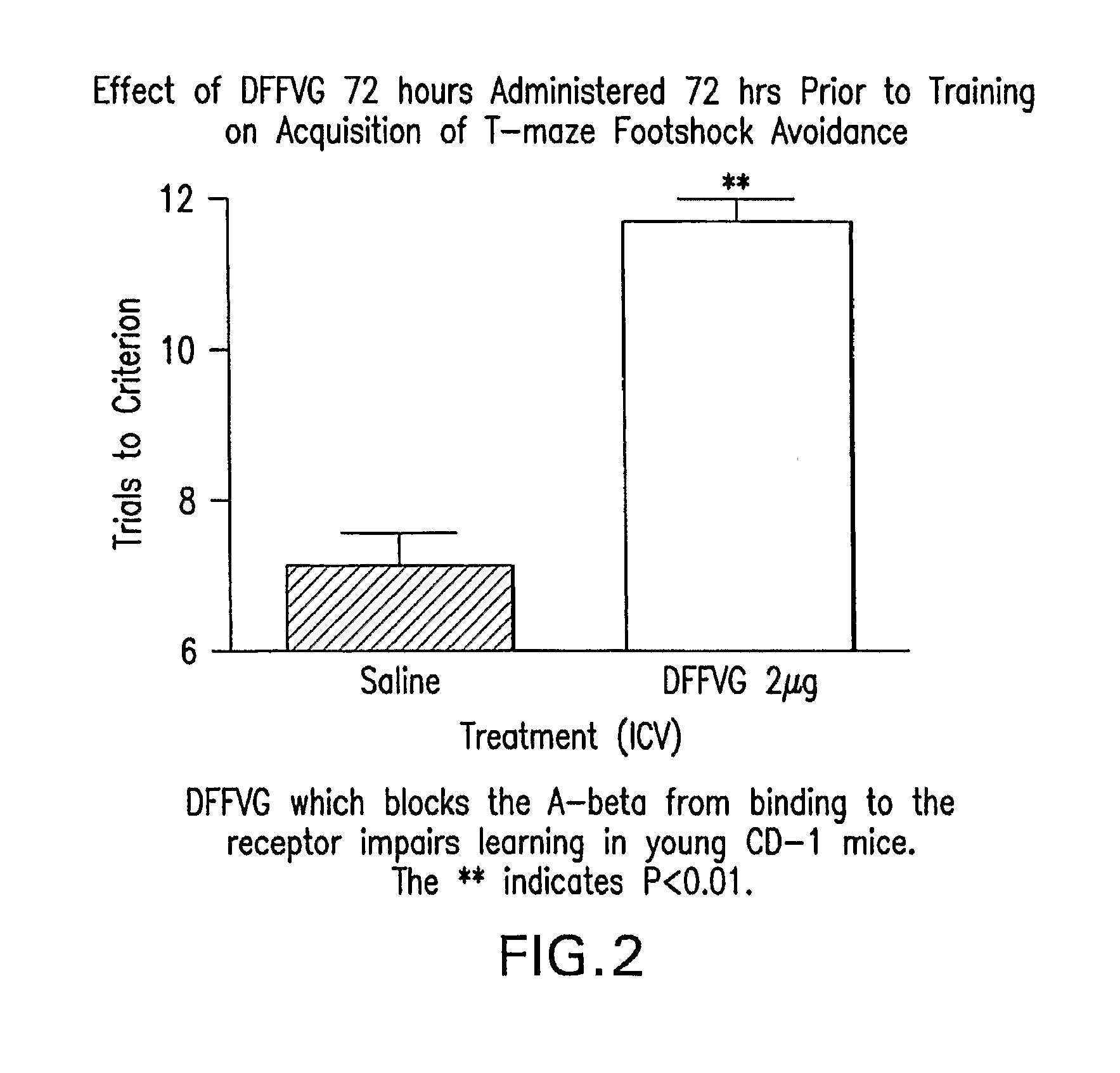

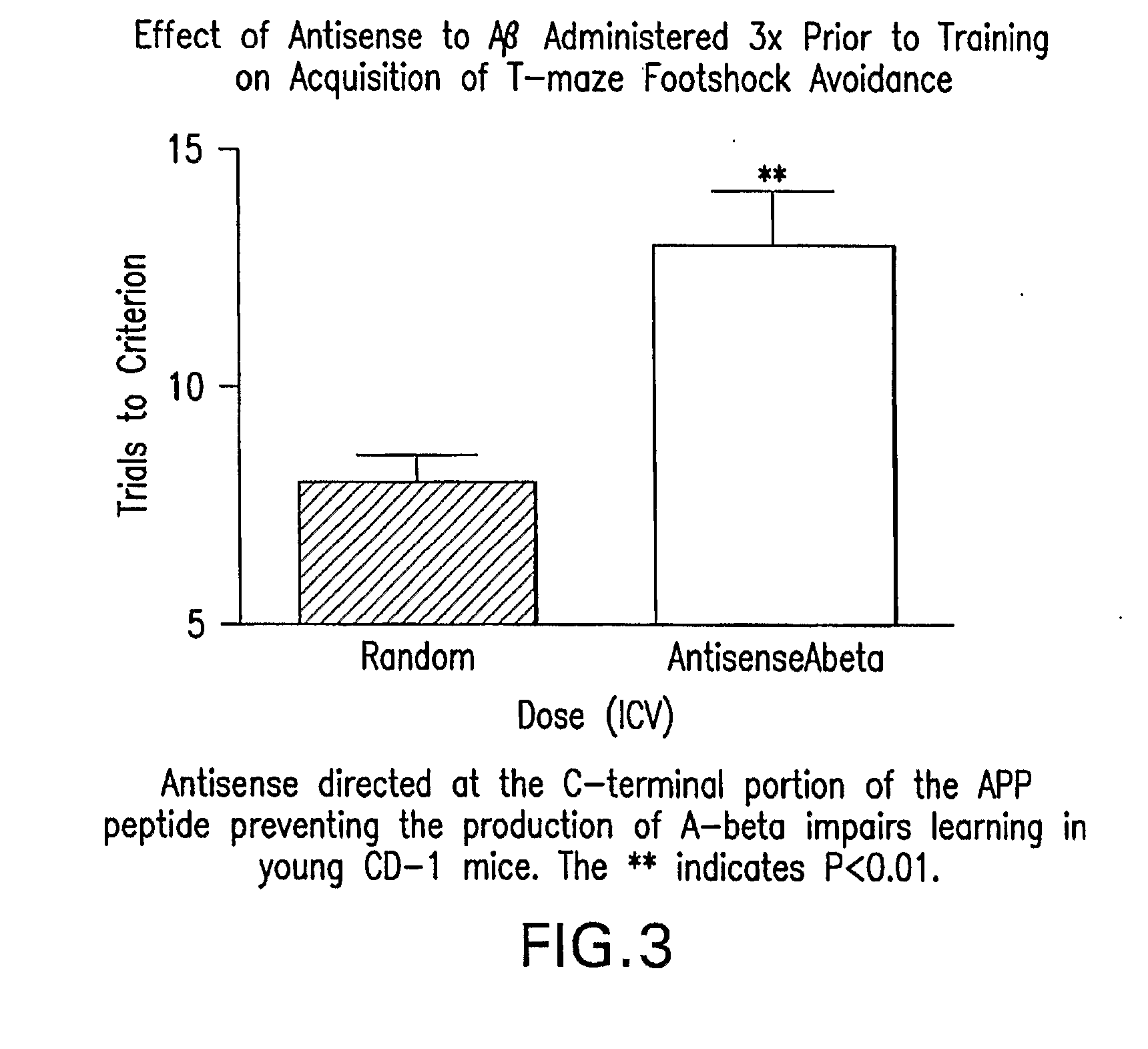

Compositions and methods for enhancing cognitive function

InactiveUS20090304676A1Lower Level RequirementsImprove learning and memoryOrganic active ingredientsNervous disorderClinical psychologyAmyloid

The present application provides methods and compositions for improving cognitive function and enhancing mental performance in subjects, including those suffering from memory deficiencies, by regulating the activity of beta amyloid (Aβ) in the brain of such subjects.

Owner:SAINT LOUIS UNIVERSITY

Nonvolatile memory device, nonvolatile memory system, and defect management method for nonvolatile memory device

ActiveUS7921340B2Accurately and easily recognizeElectronic circuit testingRead-only memoriesLife timeAudio frequency

Owner:PANASONIC CORP

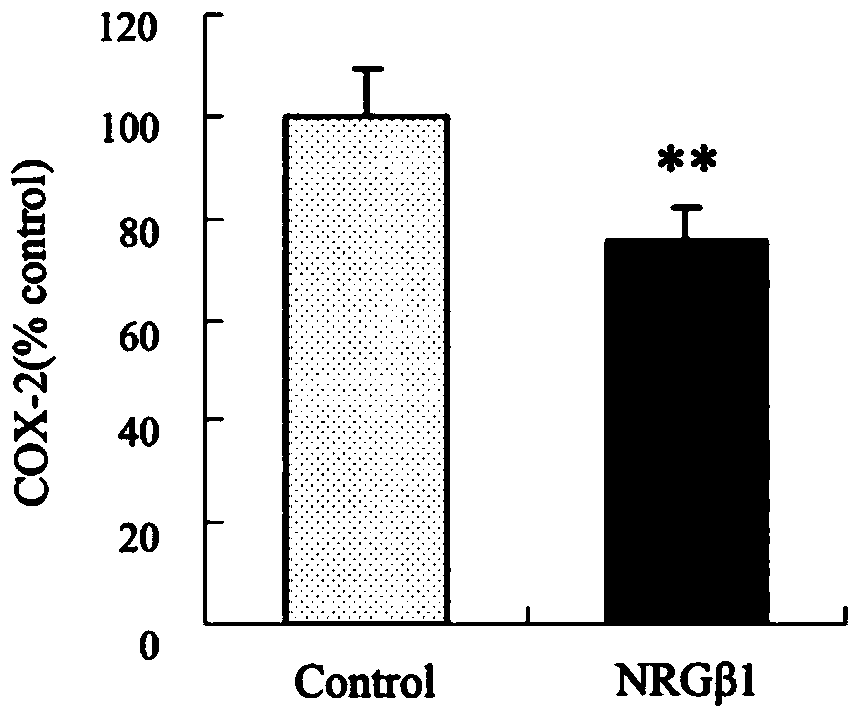

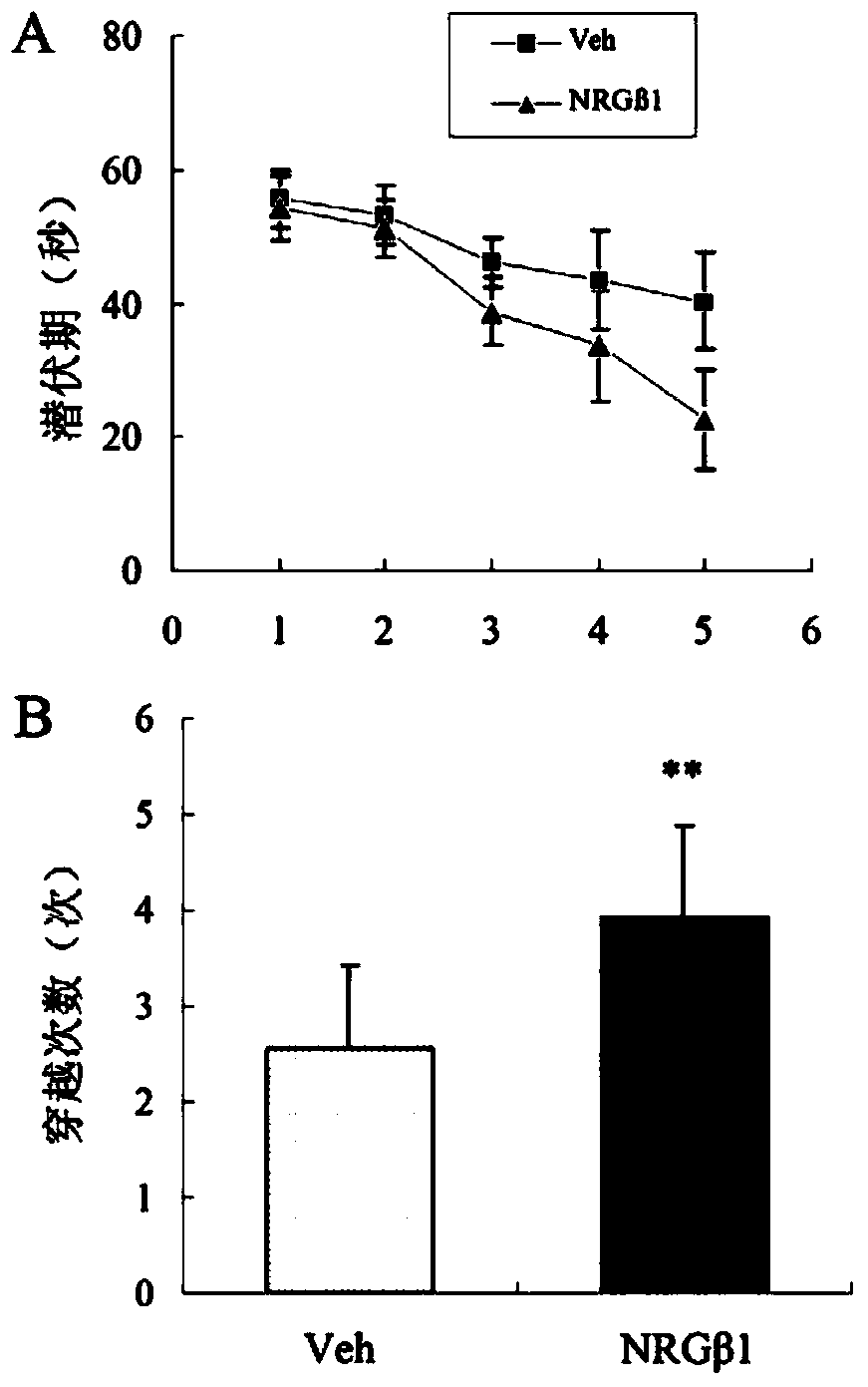

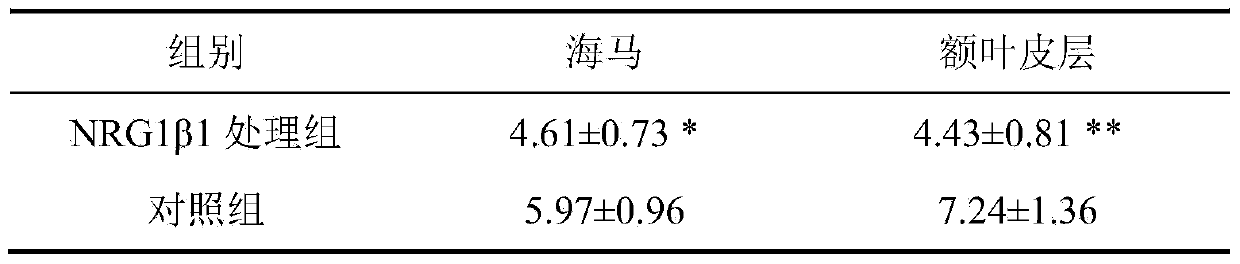

Use of neuregulin 1

InactiveCN103611153ASignificant neuroprotective effectInhibition amountNervous disorderPeptide/protein ingredientsInflammatory factorsBiological activation

The invention discloses use of neuregulin 1, belongs to the technical field of a biomedicine, and particularly relates to application of the neuregulin 1 inpreparation of a drug for treating lead encephalopathy. The characteristics of the lead encephalopathy are high expression of inflammatory cells and inflammatory factors and wide neuronal cell death. Neuron loss and nerve inflammatory reaction play a crucial role in the lead encephalopathy process. The neuregulin 1 has a significant nerve inflammatory reaction and a role of protecting cell apoptosis in the lead encephalopathy, can inhibit inflammatory activation, reduces the quantities of microglial cells and astrocytes, reduces the expression level of inflammatory cytokines COX-2, and improves the learning and memory defects caused by lead poisoning. In addition, the quantity of ErbB4 positive cells can be increased by the neuregulin 1; the inhibition apoptosis activity of anti-apoptosis protein Bc1-2 is improved; expression of pro-apoptotic protein Bax is reduced, so that apoptosis is inhibited, and neuregulin 1 has significant neuroprotective effects on the lead encephalopathy.

Owner:XINXIANG MEDICAL UNIV