Evaluation chip

一种芯片、优先级的技术,应用在仪器、电数字数据处理、检测有故障的计算机硬件等方向,能够解决不能使用EVA芯片等问题,达到增加便利性、防止空间不足、降低成本的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0020] structure

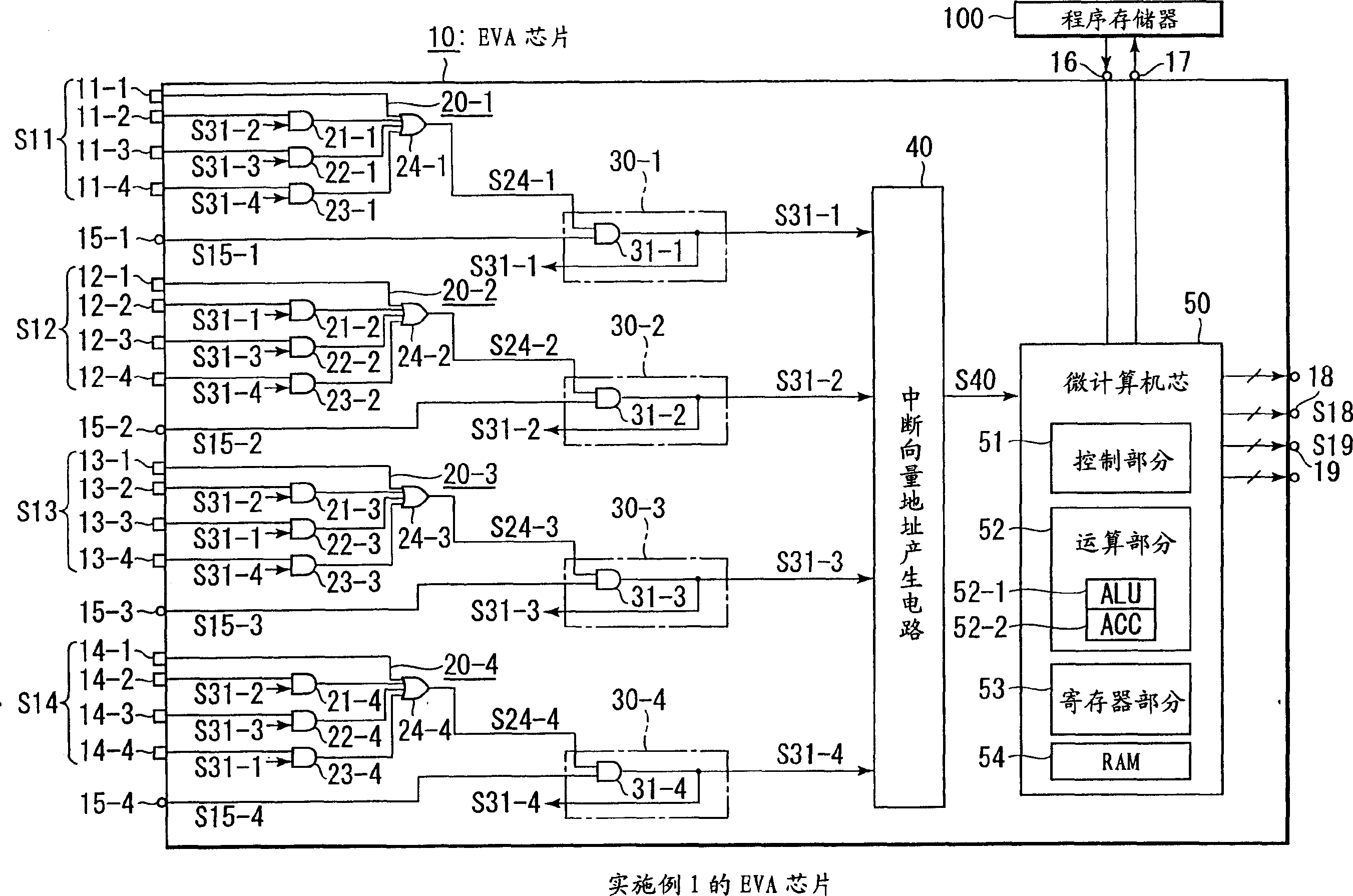

[0021] figure 1 is a schematic diagram of the EVA chip 10 according to the first embodiment (Embodiment 1) of the present invention.

[0022] The EVA chip 10 evaluates programs stored in the external program memory 100 . The EVA chip 10 includes: four groups of control signal input terminals 11-1 to 11-4, 12-1 to 12-4, 13-1 to 13-4, and 14-1 to 14-4; four interrupt request signal input terminals terminals 15 - 1 to 15 - 4 ; a command input terminal 16 ; an address output terminal 17 ; a plurality of data output terminals 18 ; and a plurality of control signal output terminals 19 . A plurality of (for example, four) four-bit control signals S11, S12, S13, and S14 for modifying and controlling the order of interrupt priority of the program are input to the four sets of control signal input terminals 11-1 to 11-4, 12, respectively. -1 to 12-4, 13-1 to 13-4, and 14-1 to 14-4. Four interrupt request signals are input to the four interrupt request signal inp...

Embodiment 2

[0045] structure

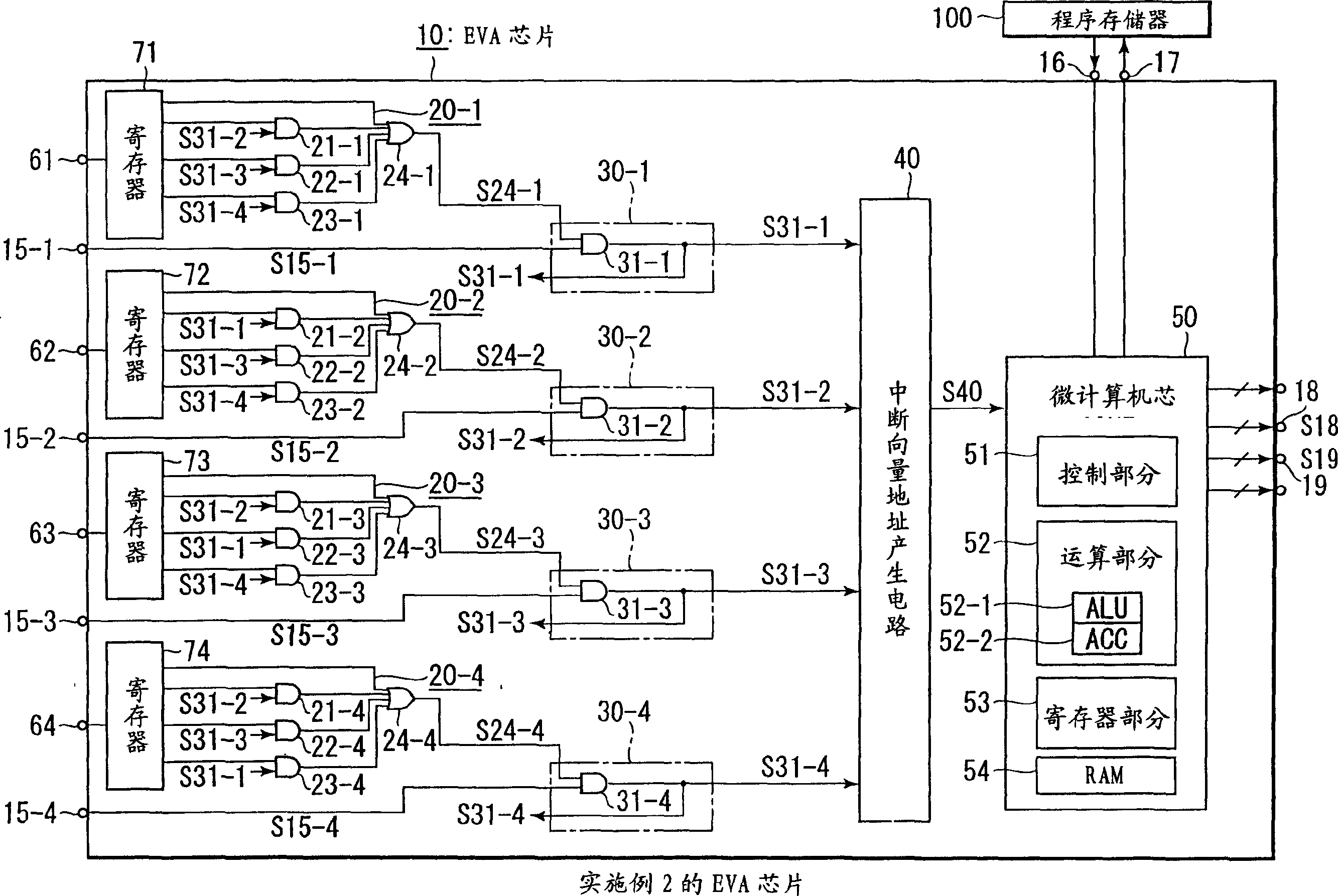

[0046] figure 2 is a schematic diagram showing an EVA chip 10A according to a second embodiment (Embodiment 2) of the present invention. and figure 1 Similar symbols are used for the same or similar structural elements in Embodiment 1.

[0047] In the EVA chip 10 of Embodiment 1, control signal input terminals 11-1 to 11-4, 12-1 to 12-4, 13-1 to 13-4, and 14-1 to 14-4 are provided to The interrupt priority order of the interrupt modules 30-1 to 30-4 is switched. The difference is that in the EVA chip 10A of Embodiment 2, four data input terminals 61 to 64, and four priority order control registers 71 to 74 respectively connected to these terminals are provided instead of the control signal input terminals 11- 1 to 11-4, 12-1 to 12-4, 13-1 to 13-4, and 14-1 to 14-4.

[0048] Data on the priority order of interrupts is input to the data input terminals 61 to 64 from the CPU controlling the EVA chip 10A. The priority order control registers 71 to 74 ar...

Embodiment 3

[0061] structure

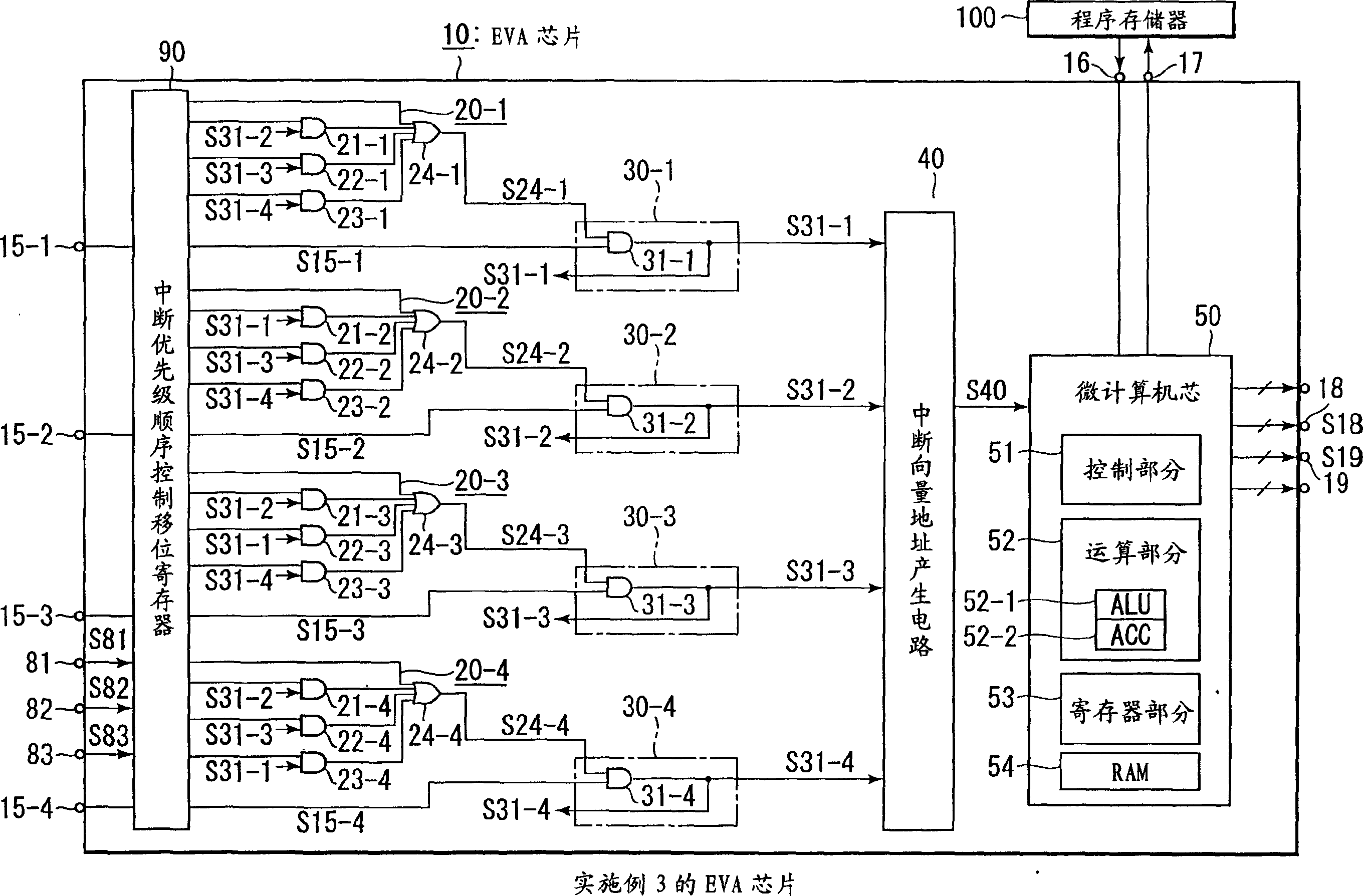

[0062] image 3 is a schematic diagram of an EVA chip 10B according to a third embodiment (Embodiment 3) of the present invention. and figure 1 Example 1 in and figure 2 Similar reference numerals are used for the same structural elements in Embodiment 2.

[0063] In the EVA chip 10A of Embodiment 2, data input terminals 61 to 64 and priority order control registers 71 to 74 are provided to switch the interrupt priority order of the interrupt modules 30-1 to 30-4. The difference is that in the EVA chip 10B of Embodiment 3, three input terminals 81 to 83 and a 12-bit interrupt priority sequence control shift register 90 connected to these terminals are provided instead of the data input terminals 61 to 64 and Priority order control registers 71 to 74.

[0064] At the input terminal 81, the serial 12-bit priority order data S81 is input from the outside, at the input terminal 82, the synchronous clock S82 is input from the outside; and at the input ter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com