Comparator with output offset correction and mos logical circuit

An oxide semiconductor and offset correction technology, applied in the field of comparators, can solve the problems of inconsistent output common mode level of MCML circuits, abnormal operation of MCML circuits, and limiting the maximum operating frequency and analytical capabilities of MCML circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

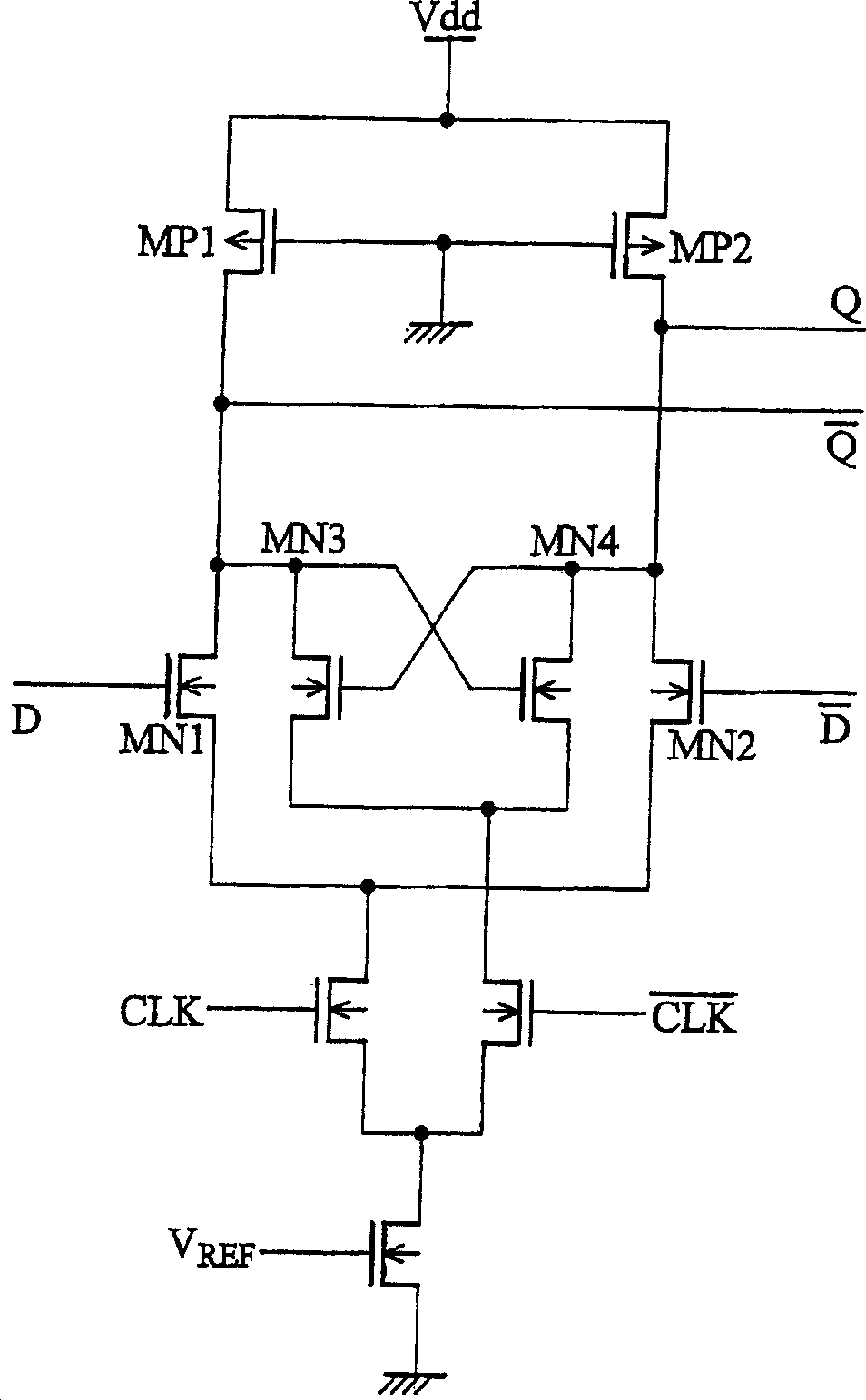

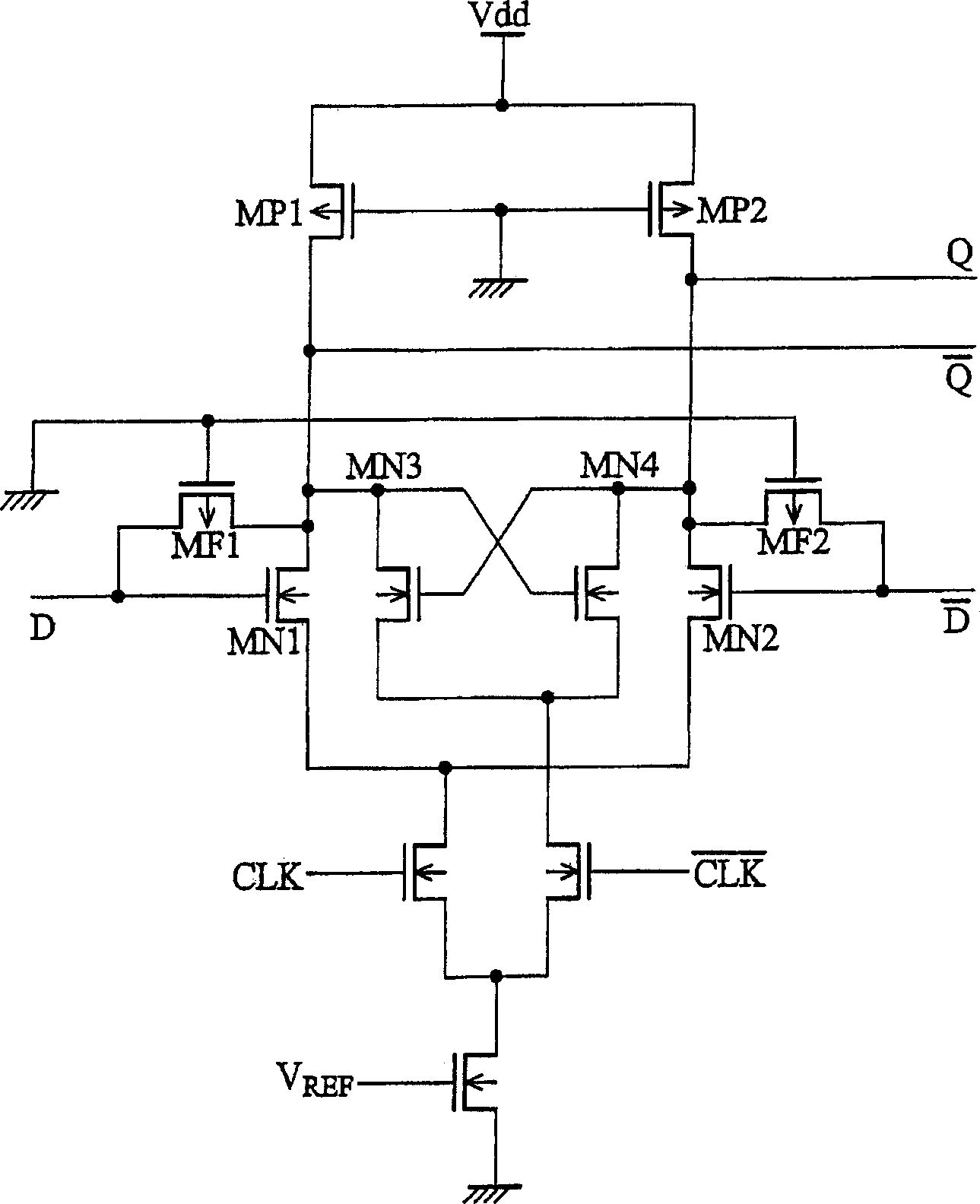

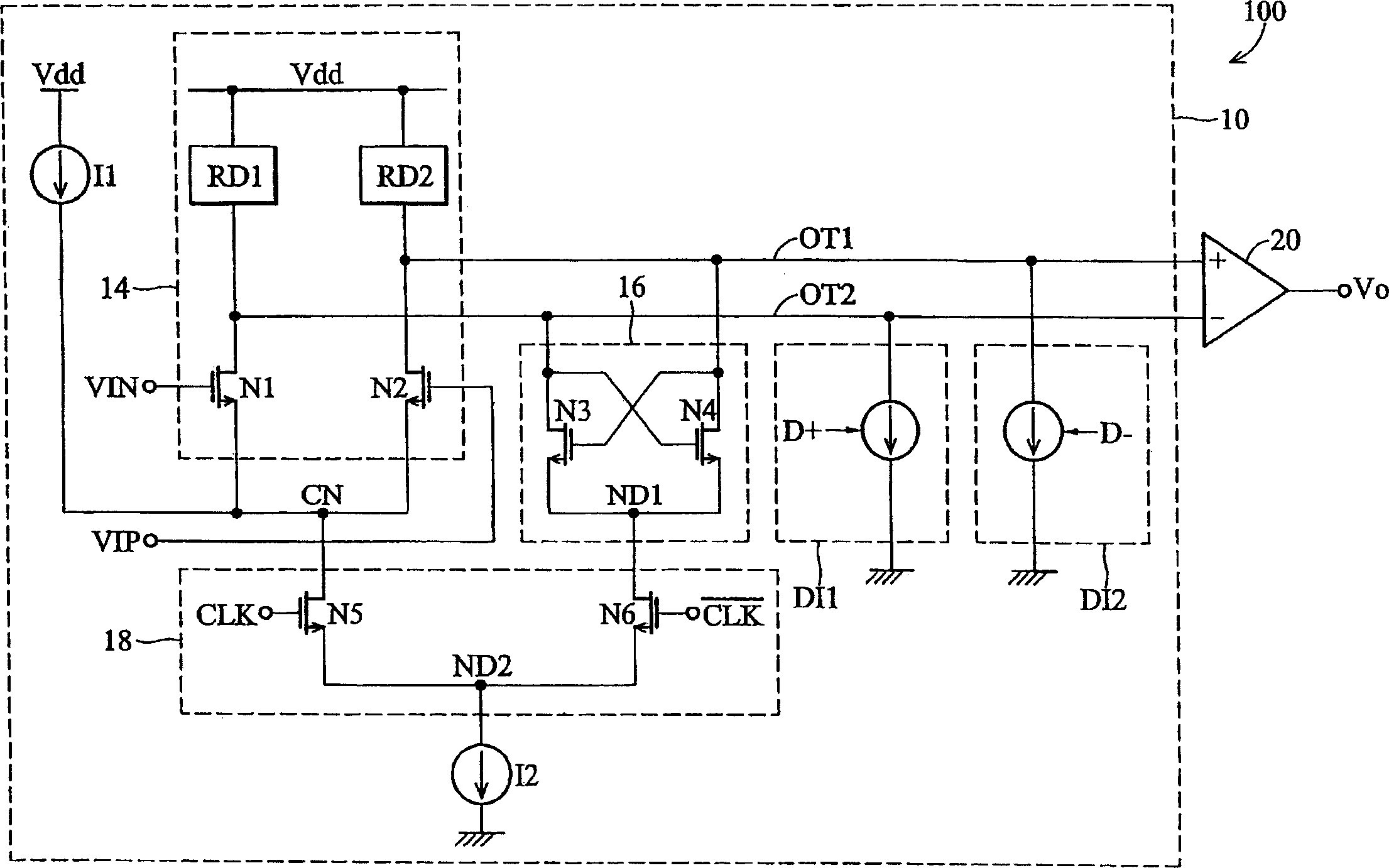

[0048] figure 2 is shown as an embodiment of the comparator of the present invention, while image 3 Shown is a schematic circuit diagram of a MOS current mode logic (MCML) circuit of the present invention. Such as figure 2 and image 3 As shown, the comparator 100 includes a metal oxide semiconductor current mode logic circuit (hereinafter referred to as MCML circuit) 10 and an output stage 20 .

[0049] The MCML circuit 10 receives input signals VIN and VIP, and generates differential logic signals on output terminals OT1 and OT2. MCML circuit 10 includes a coupling circuit 12 (shown only in image 3 middle), a differential input stage 14, a latch unit 16, a differential pair 18, a current source I2 (only shown in figure 2 middle), a correction unit (DI1 and DI2), and a booster I1 (only shown in image 3 middle). The boosting device I1 is used for pulling up the voltage level of the common node CN to the power supply voltage Vdd in a comparison mode.

[0050] The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More