Method for controlling pre-aligning of silicon wafer

A control method and silicon wafer technology, applied in computer control, general control system, control/regulation system, etc., can solve problems such as great influence, low precision, and increase equipment cost, achieve measurement error suppression, improve overall Performance, easy to use effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The silicon wafer pre-alignment control method of the present invention is described in detail as follows in conjunction with embodiments and accompanying drawings:

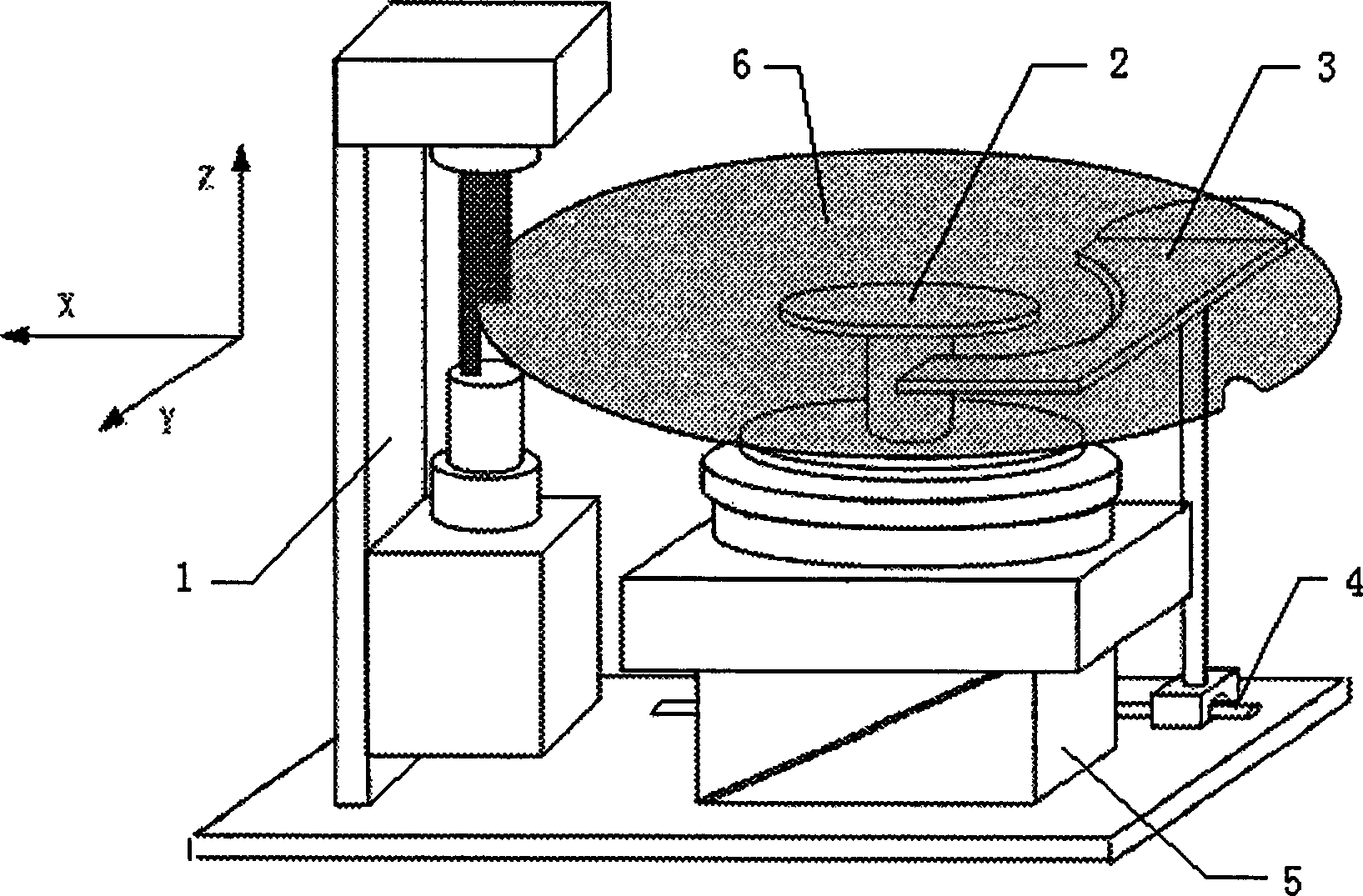

[0034] The structure of the embodiment of the silicon wafer pre-alignment equipment used in the method of the present invention is as follows figure 1 As shown, wherein, 6 is a silicon wafer with a notch (in this embodiment, an 8-inch (diameter 200mm) silicon wafer is used), 2 is a rotating unit, which can rotate around the Z axis, and the circular platform at the top has a The groove is used for vacuum adsorption of silicon wafers; 5 is a wedge-shaped platform, which can make the rotating unit 2 move along the Z direction by moving in the X direction; 3 is the centering unit, and the top of the semicircular platform also has a groove 4 is a horizontal guide rail, and the centering unit 3 can move in the X direction along the horizontal guide rail; 1 is a CCD detector (in this embodiment, the line array li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More