Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit

A technology of standard cell and layout method, applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of indeterminate gate electrode distance, inability to handle OPC, etc., and achieve the effect of reducing chip area and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

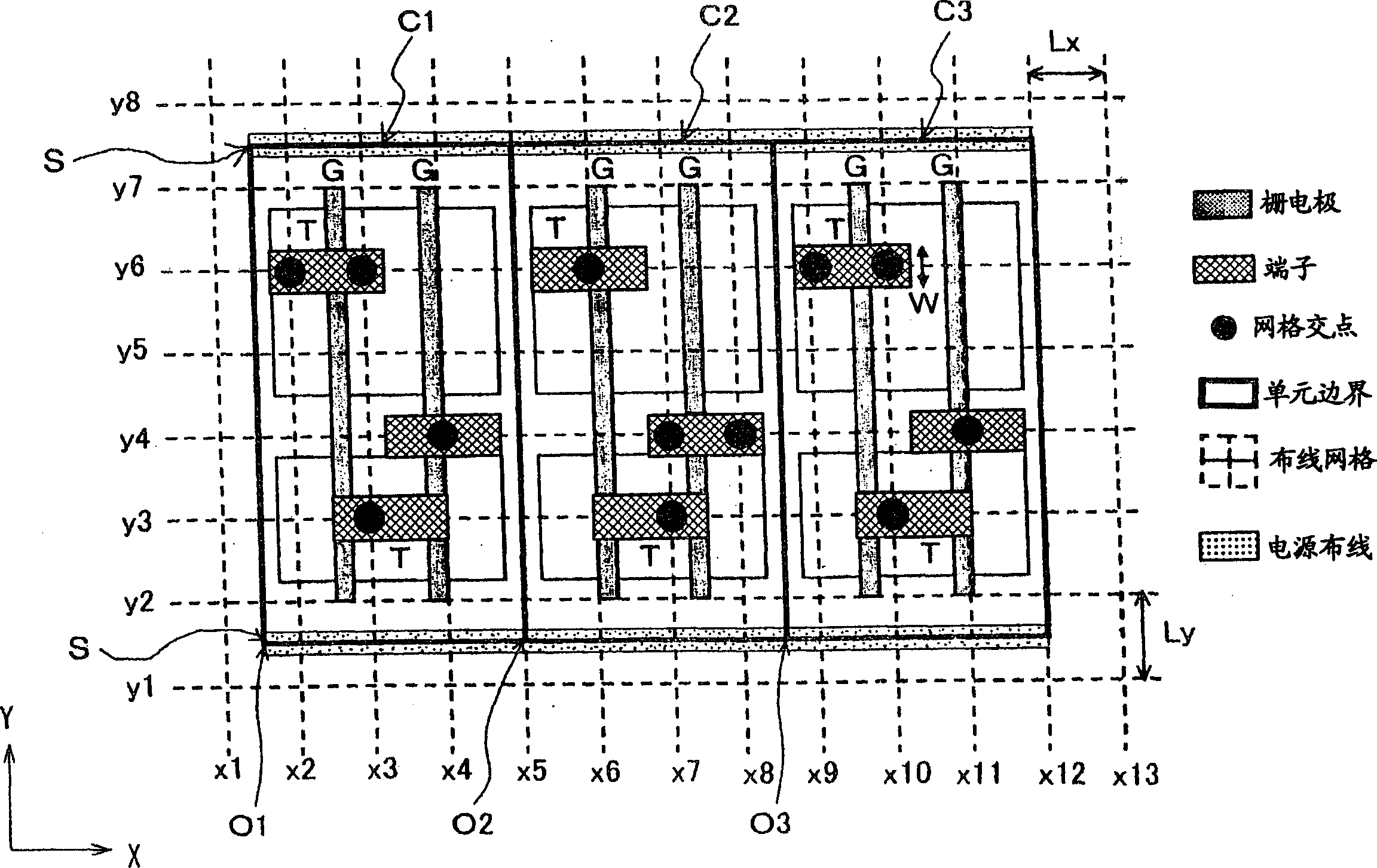

[0077] figure 1 is a layout of a standard cell according to Embodiment 1 of the present invention. The direction along the power supply wiring S of the standard cell refers to the X direction, and the direction perpendicular to the power supply wiring S refers to the Y direction. The power wiring S is only an example, and does not necessarily have to be configured as shown.

[0078] see figure 1 Reference numerals in , x1-x13 represent the wiring grid used in automatic placement & routing and provided along the X direction, y1-y8 represent the wiring grid provided along the Y direction, C1, C2 and C3 represent Standard cells, O1, O2 and O3 represent the starting point of C1, C2 and C3 respectively, T represents the terminal capable of transmitting the input signal or output signal of the standard cell Ci (i=1, 2, . . . ), and G represents the gate electrode.

[0079] Automatic place & route tools are automated design tools for locating cells and blocks and routing paths t...

Embodiment 2

[0091] Figure 5 It is a design flowchart of the automatic place & route method using standard cells according to Embodiment 2 of the present invention.

[0092] An automatic placement & routing apparatus for performing an automatic placement & routing method, comprising a connection information input device for obtaining connection information of a logic circuit from outside, a design constraint input device for obtaining design constraints of a logic circuit from outside, A layout information input device for externally obtaining standard cell layout information, a temporary layout device for temporarily arranging individual cells based on the obtained connection information, and a relocation for relocating temporarily arranged cells to reduce the area equipment. The automatic place & route apparatus of such a structure places and routes a logic circuit including a plurality of standard cells.

[0093] First, circuit connection information of logic circuits for connecting ...

Embodiment 3

[0101] Figure 7 It is a design flowchart of the automatic place & route method using standard cells according to Embodiment 3 of the present invention.

[0102] An automatic place & route apparatus for performing an automatic place & route method includes a connection information input device for externally obtaining connection information of a logic circuit, a design constraint input device for externally obtaining a design constraint of the logic circuit, Layout information input equipment for obtaining standard cell layout information from outside, layout equipment for arranging cells based on the obtained connection information, temporary wiring processing equipment for providing temporary wiring for terminals connecting individual cells, for forming terminals terminal forming processing equipment, and actual wiring processing equipment.

[0103] First, circuit connection information of logic circuits for connecting a plurality of standard cells to each other, design con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More