NOR flash memory and manufacture method thereof

A manufacturing method and memory technology, which are applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problem that the area of NOR-type flash memory cannot be further reduced, and achieve the effect of reducing the array area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

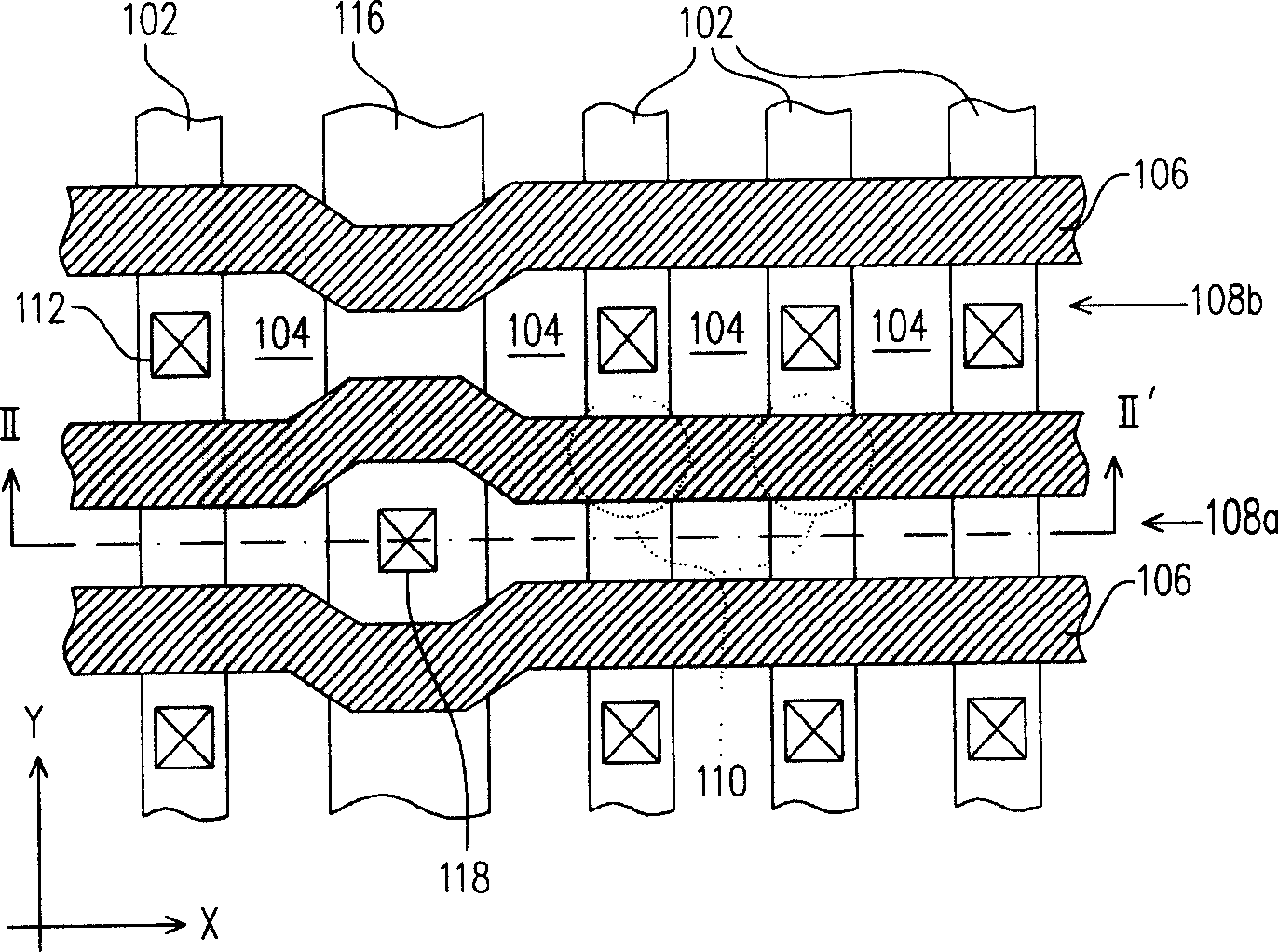

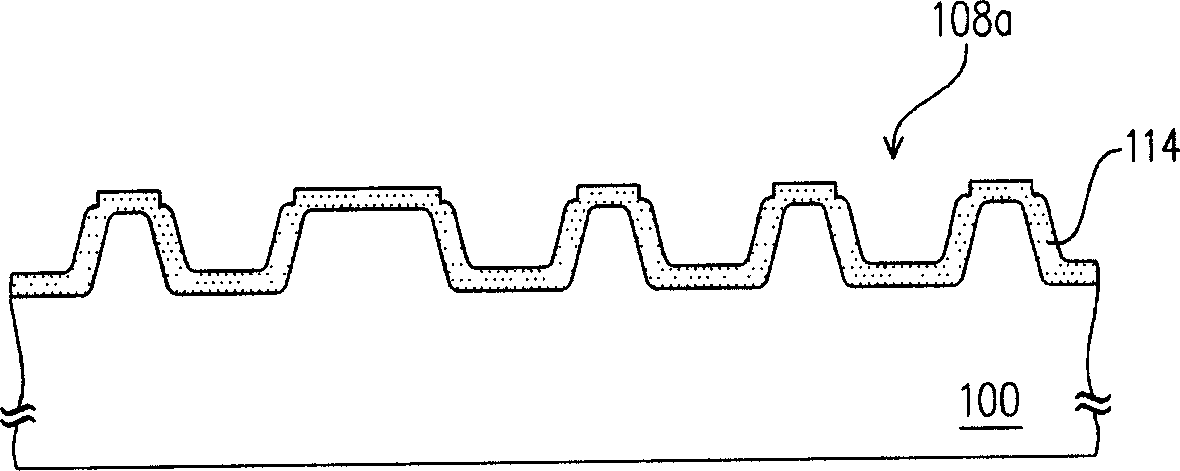

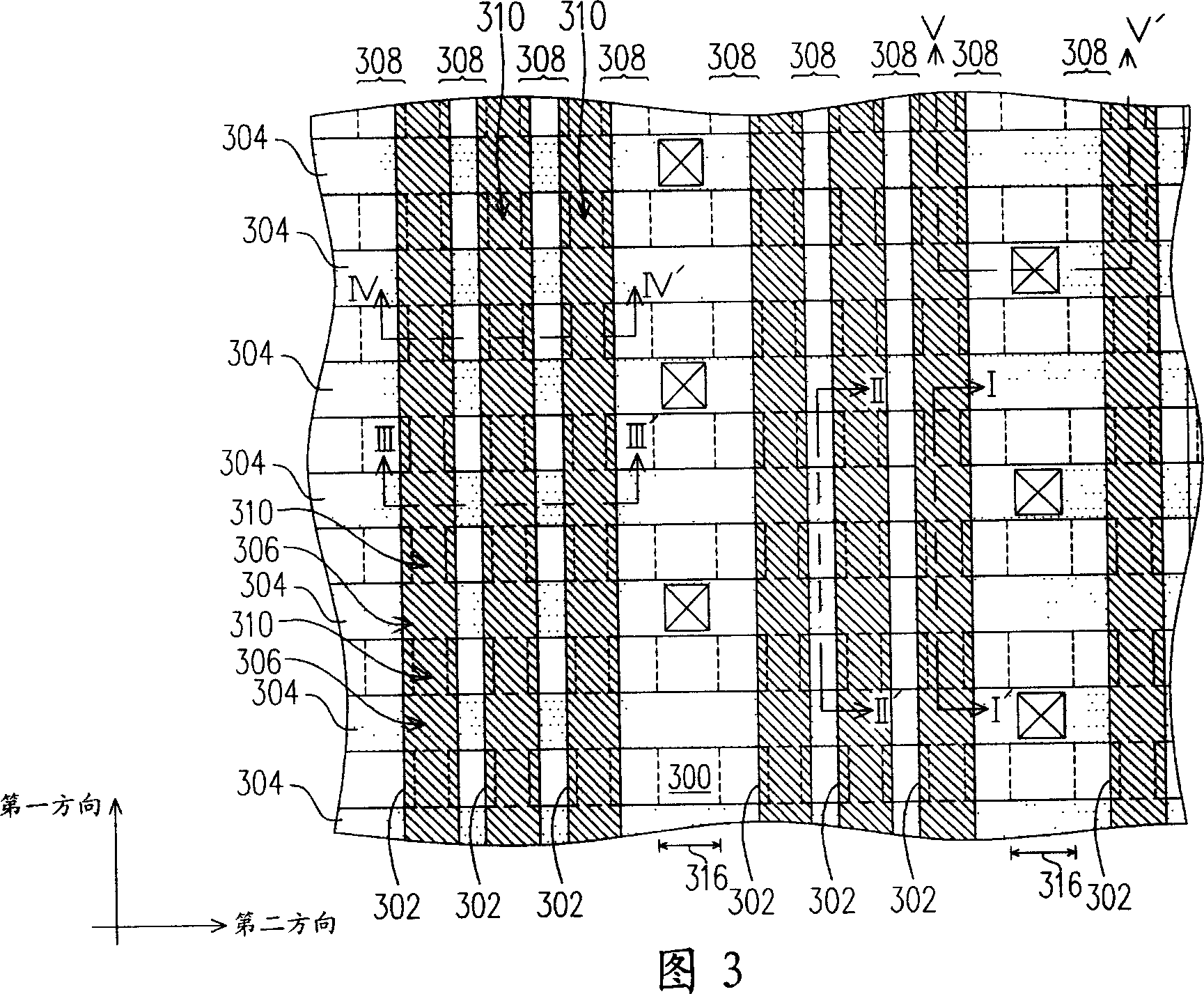

[0050] FIG. 3 is a top view of a NOR flash memory body according to a first embodiment of the present invention. Figure 4-I , Figure 4-II , Figure 4-III and Figure 4-IV Then it is respectively the sectional view of I-I' line segment, II-II' line segment, III-III' line segment and IV-IV' line segment in Fig. 3 .

[0051] Please refer to Figure 3 together with Figure 4-I , Figure 4-II , Figure 4-III and Figure 4-IV As shown, the NOR flash memory body of this embodiment is basically composed of a substrate 300, several control gates 302, several doped regions 304, isolation layers 306, several isolation structures 308, and multiple floating gates. 310 . The tunneling dielectric layer 312 and the inter-gate dielectric layer 314 are formed. Wherein, the control gate 302 is arranged on the substrate 300 in a first direction, and the doped region 304 is arranged in the substrate 300 in a second direction, and in the NOR flash memory body of this embodiment, the doped reg...

no. 2 example

[0057] The manufacturing process of the NOR flash memory body of the present invention will be described in detail later, but it is only used as an example of the application of the present invention, rather than limiting the present invention to the following methods. In addition, if the "main component symbol" used below is the same as that of each previous figure, it represents the same or a similar component.

[0058] Figures 6A-I to Figure 6D-I It is a sectional view of the manufacturing process of the I-I' line segment of Fig. 3. Figure 6A-II to Figure 6E-II It is a sectional view of the manufacturing process of the II-II' line segment in Fig. 3 . Figure 6A-III to Figure 6E-III It is a sectional view of the manufacturing process of the III-III' line segment in Fig. 3 . Figures 6A-IV to Figure 6E-IV It is a sectional view of the manufacturing process of the IV-IV' line segment of Fig. 3 .

[0059] Please also refer to FIGS. 6A-I to 6A-IV. In a substrate 300, sev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com