Non-volatile memory body and operating method and mfg. method thereof

A technology of manufacturing method and operation method, applied in semiconductor/solid-state device manufacturing, electric solid-state device, semiconductor device, etc., can solve problems such as easy leakage of charge, thermal hole damage of tunnel oxide layer, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029]

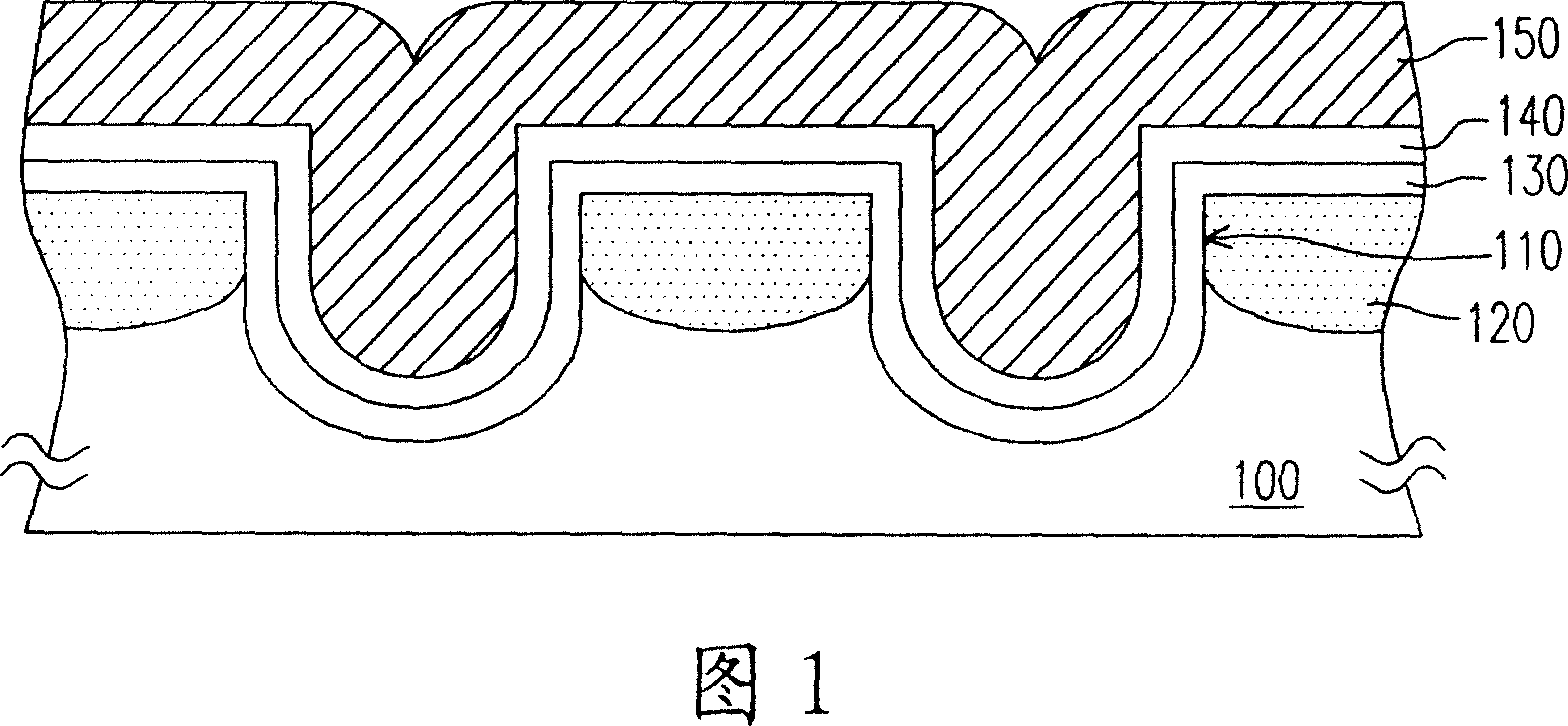

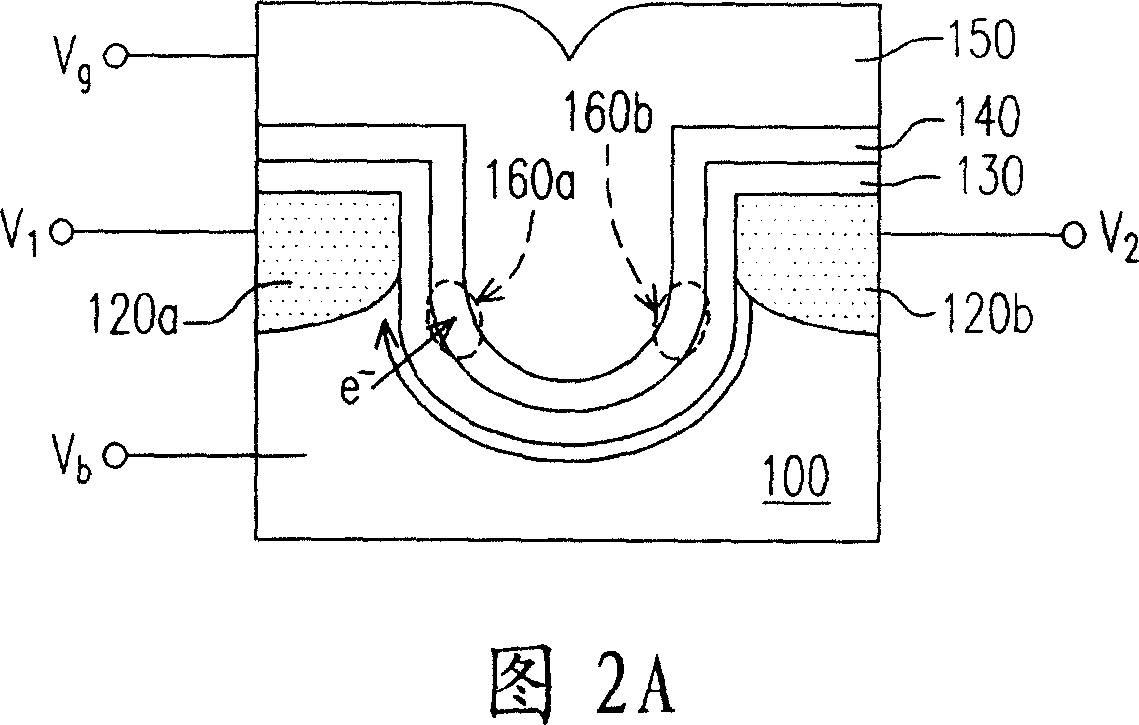

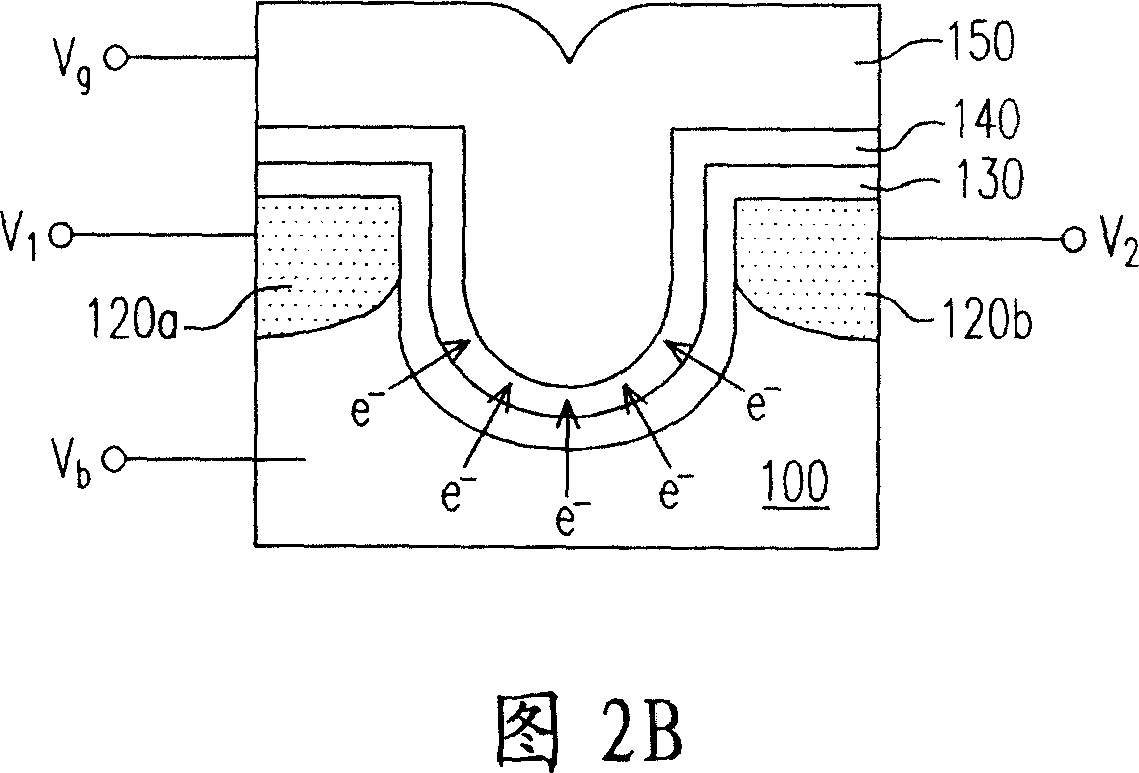

[0030] 1 is a cross-sectional view of a non-volatile memory array structure in a preferred embodiment of the present invention, and FIG. 6F is a top view of the structure, and FIG. 1 corresponds to the IV-IV' section of FIG. 6F. 1 and 6F, the non-volatile memory array at least includes a semiconductor substrate 100 having a plurality of trenches 110, buried bit lines 120, a charge trapping layer 140 and a plurality of word lines 150.

[0031] The aforementioned substrate 100 is, for example, a substrate mainly composed of p-doped silicon, and each trench 110 preferably has a rounded bottom to reduce stress and channel leakage current. The buried bit lines 120 are located in the substrate 100 between the trenches 110 and can be formed by high concentration n-type doping, such as phosphorus ions and / or arsenic ions. The charge trapping layer 140 is disposed on the substrate 100 and in the trench 110, and its material is, for example, SiN, Al 2 o 3 , HfO 2 , HfAlO o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com