Method for fabricating grid dielectric layer, and semiconductor components

A manufacturing method and a technology for a gate dielectric layer, which are applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as the inability to increase the on-state current of semiconductor components.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

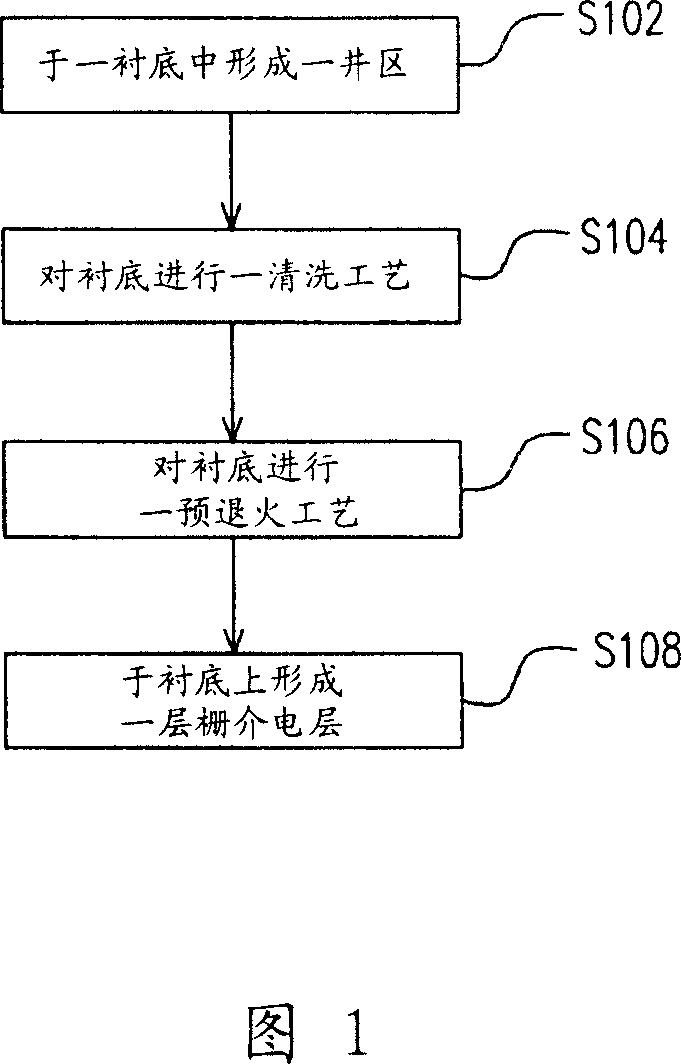

[0039] FIG. 1 is a flowchart illustrating the fabrication of the gate dielectric layer proposed by the present invention.

[0040] First, a well region is formed in a substrate (S102). Next, a cleaning process is performed on the substrate (S104). Then, a pre-annealing process is performed on the substrate (S106). Next, a gate dielectric layer is formed on the substrate (S108).

[0041] The gate dielectric layer formed according to the above method, because the pre-annealing process is performed after the native oxide layer is removed by the cleaning process, can effectively compensate for the lattice defects caused by the ion implantation process. In this way, the formed gate oxide layer has better quality and can effectively increase the on-state current of the semiconductor device.

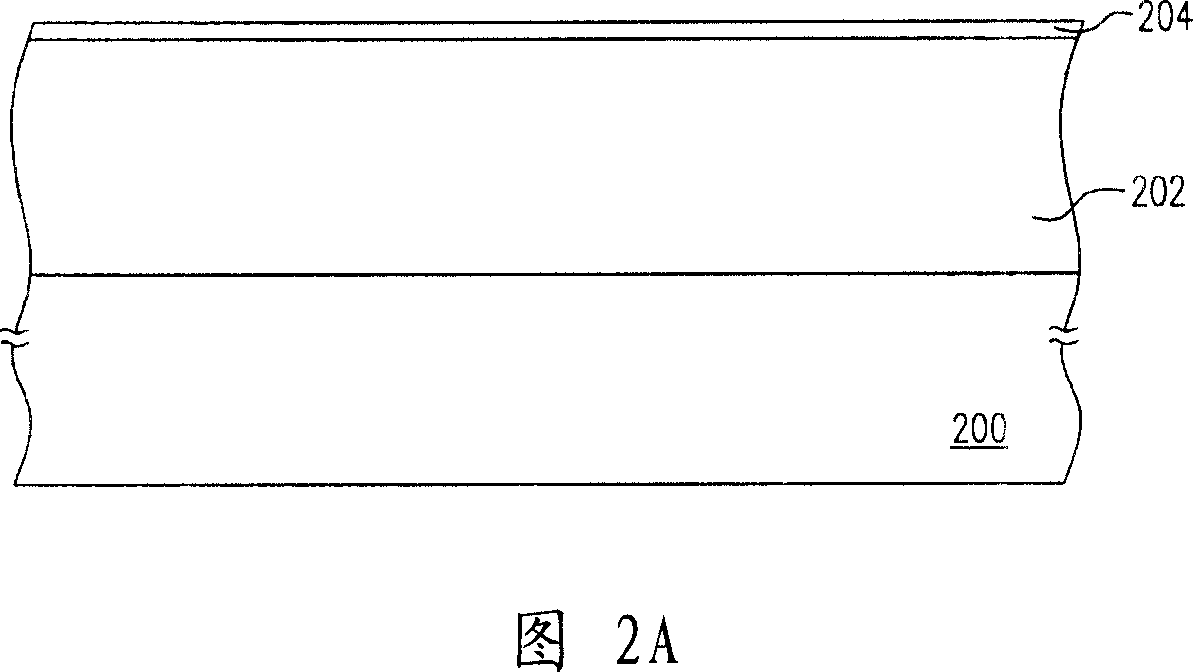

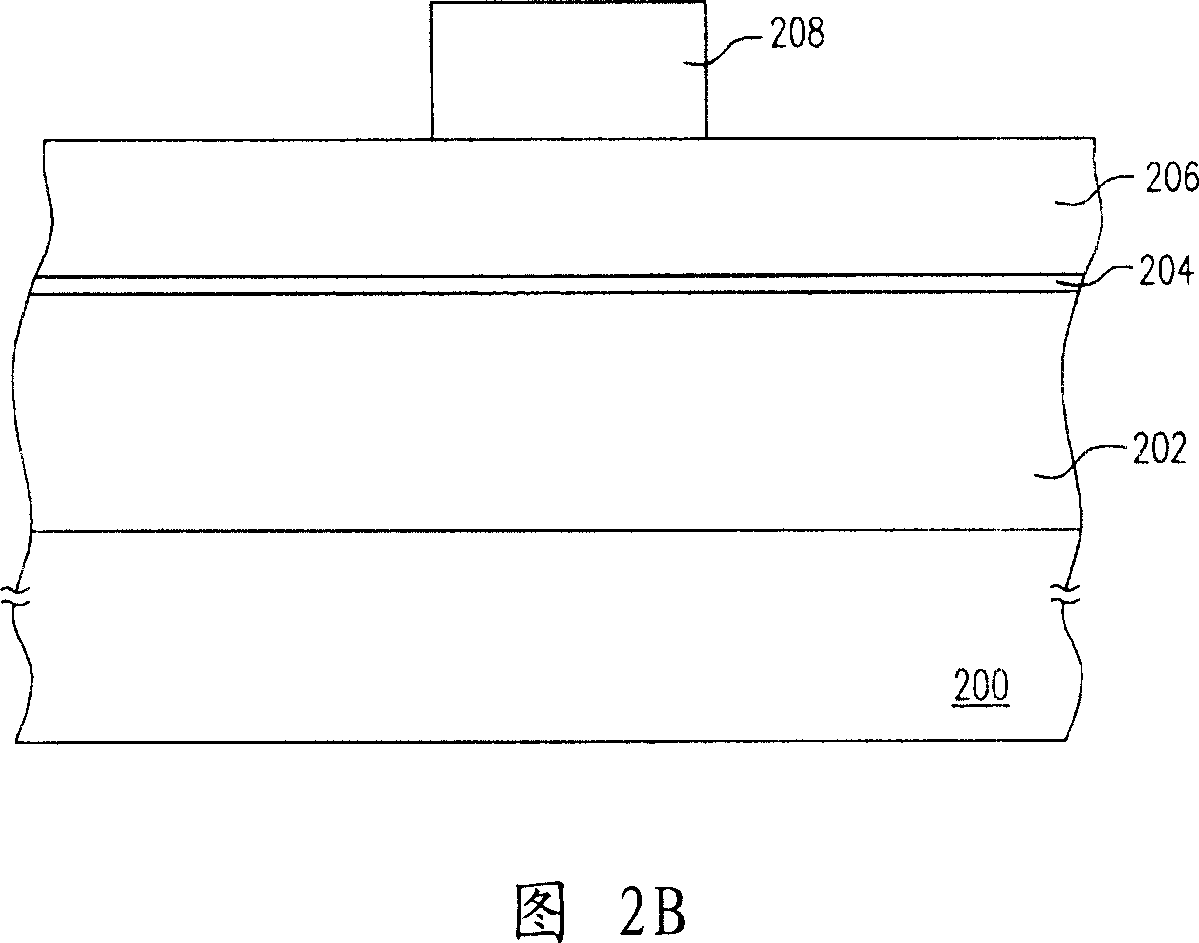

[0042] 2A-2D are cross-sectional views of a manufacturing process of a semiconductor device according to an embodiment of the present invention.

[0043] Please refer to FIG. 2A , the semic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More