Circuit-board laying-out method

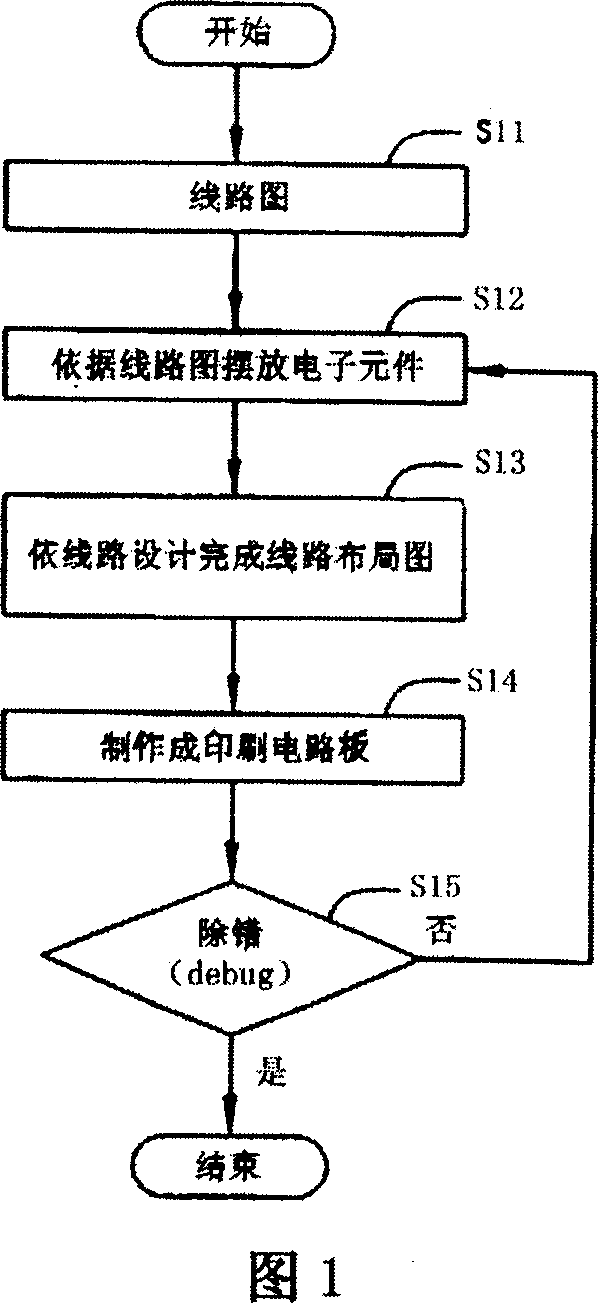

A layout method and circuit board technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as unable to debug and repair, time-consuming and laborious, and prolonged debugging time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

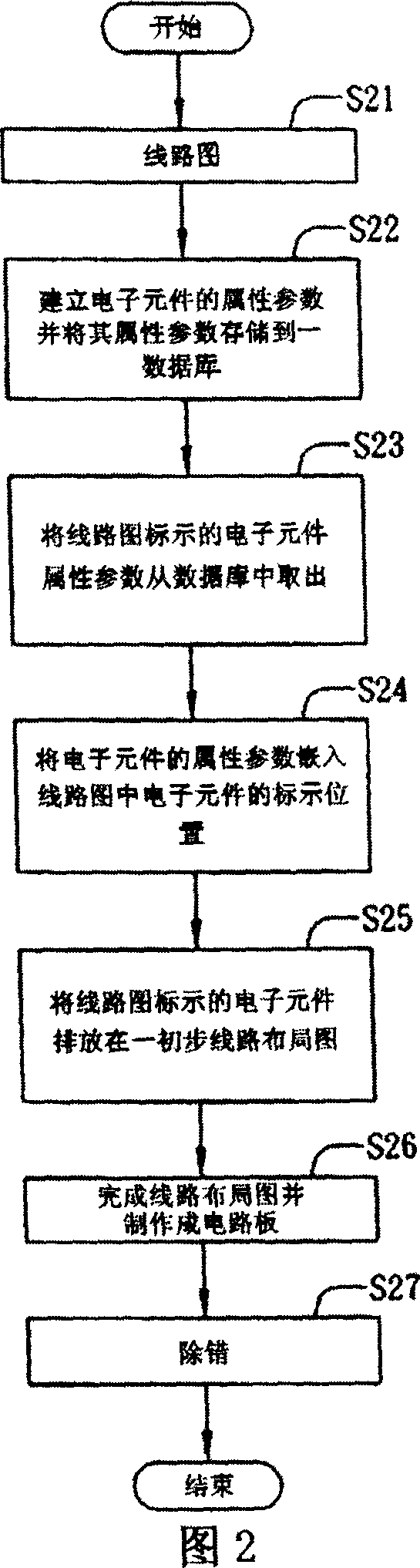

[0020] 2 and 3 at the same time, the circuit board layout method of the present invention includes the following steps. As shown in step S21, a circuit diagram 20 is first provided; then, in step S22, the circuit board layout method according to the electronic component 20a in the circuit diagram 20 is established. Attribute parameters, and store the electronic component 20a and its attribute parameters 21 in a database. The electronic component 20a is a chipset, a central processing unit, a driver chip, a control chip, a special application chip or a passive component. The passive component is Resistors, capacitors, inductors or switches; then in step S23, the attribute parameters 21 of the electronic component 20a marked in the circuit diagram 20 are retrieved from the database; then, as shown in step S24, the electronic component 20a in the circuit diagram 20 The attribute parameter 21 is embedded in the position marked by the electronic component 20a in the circuit diagram 20,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More