Stacking system and method

a technology of integrated circuits and stacking chips, applied in the direction of printed circuit manufacturing, printed circuit non-printed electric components association, printed circuit aspects, etc., can solve the problems of not providing a technology for stacking chip scale packages, significant expense, and require topologies of added cost and complexity, and achieve reasonable cost production, easy to understand and manage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

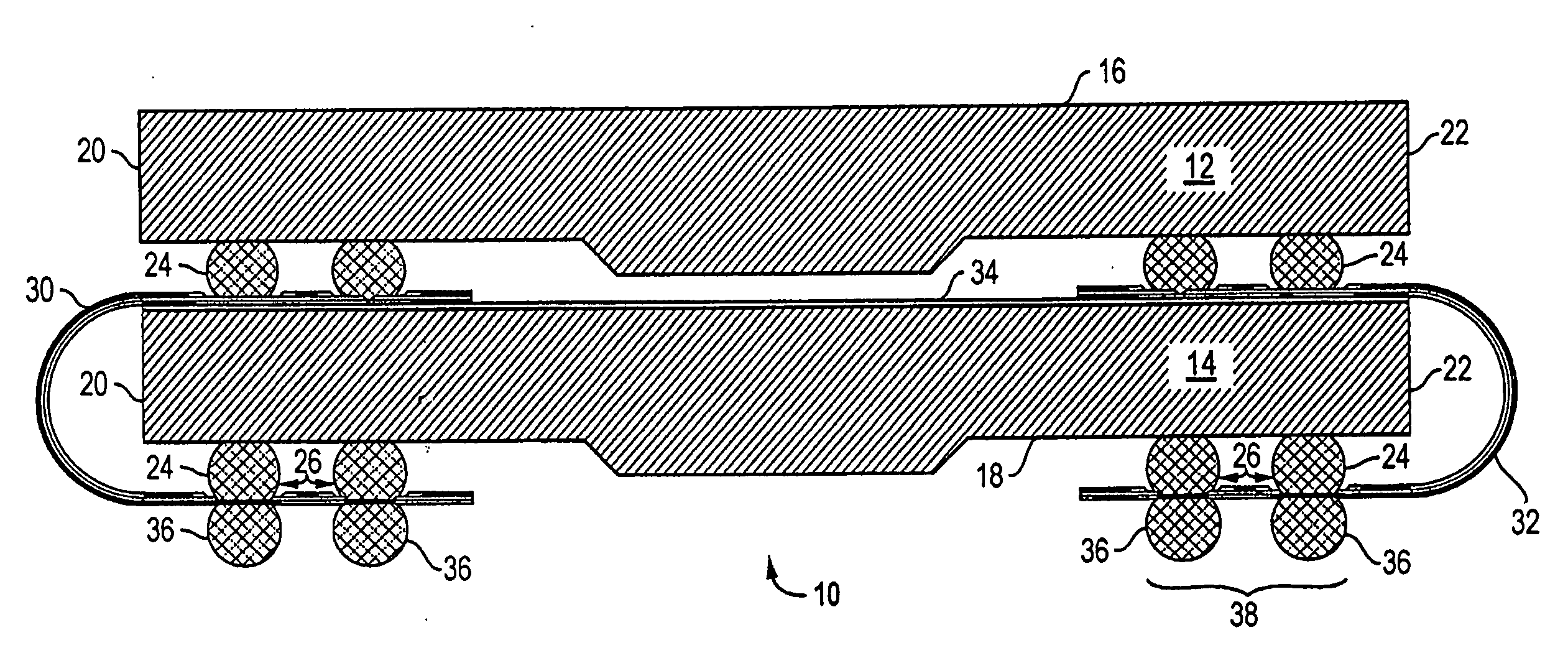

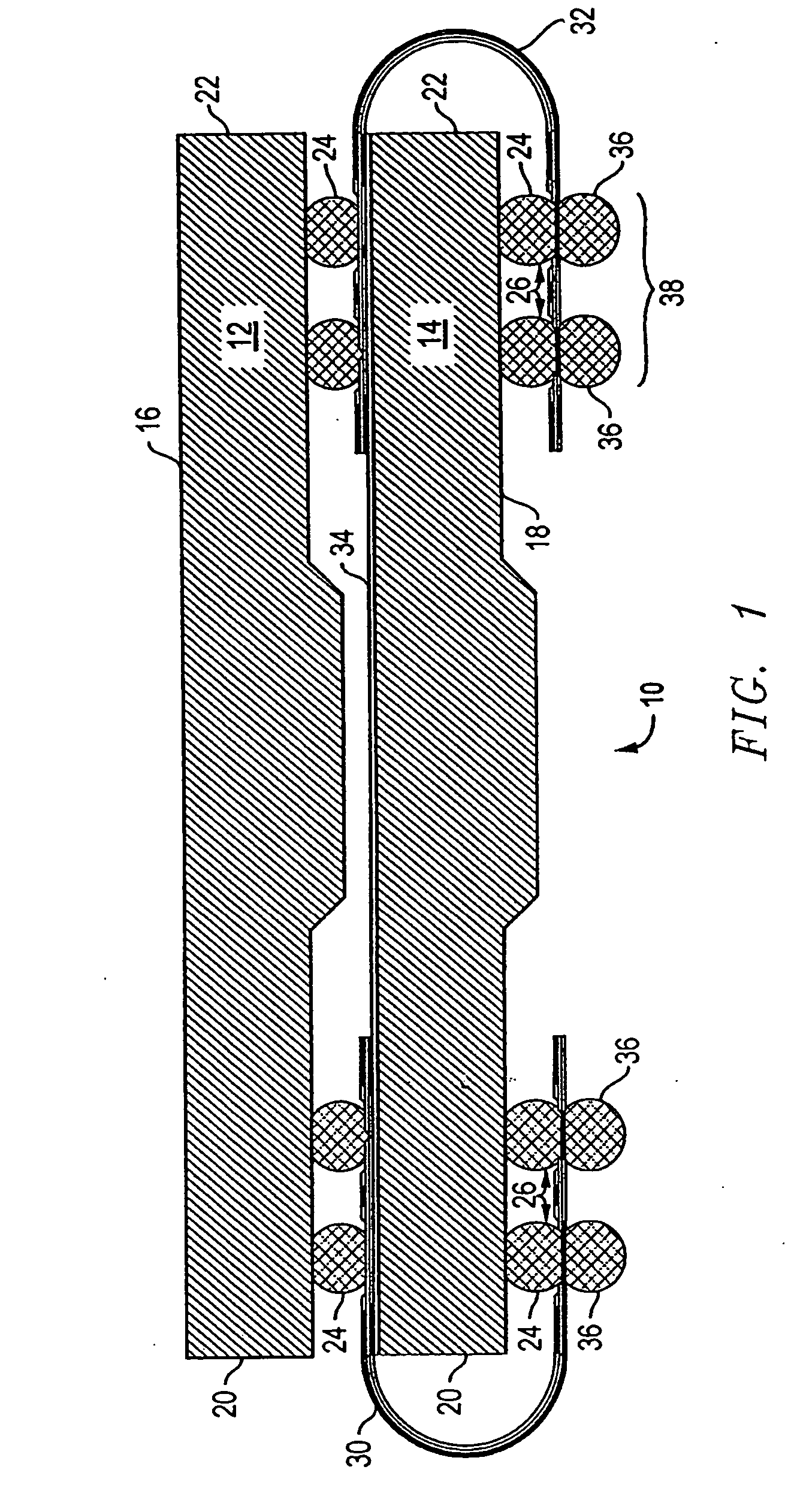

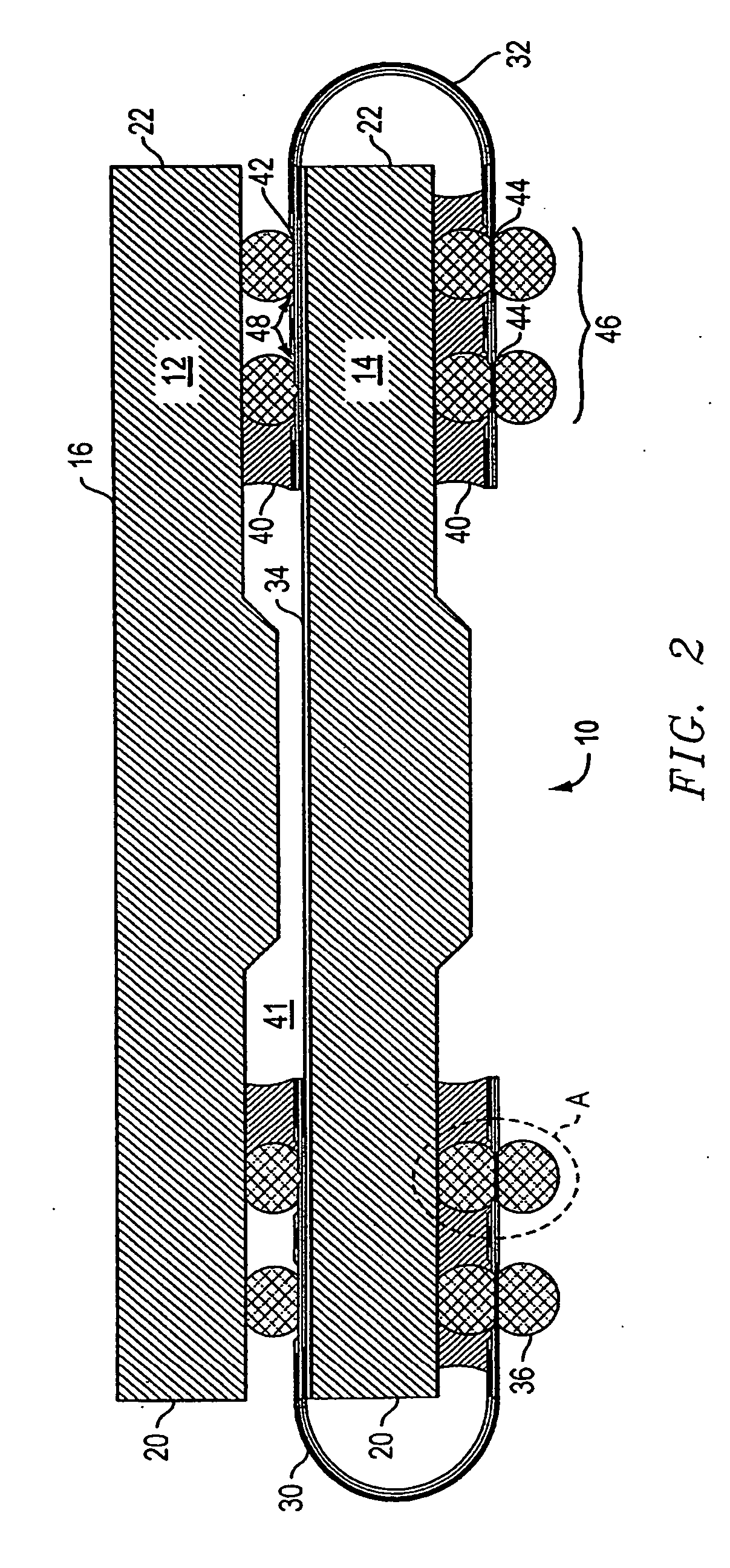

[0041]FIG. 1 is an elevation view of module 10 devised in accordance with a preferred embodiment of the present invention. Module 10 is comprised of upper CSP 12 and lower CSP 14. Each of CSPs 12 and 14 have an upper surface 16 and a lower surface 18 and opposite lateral sides 20 and 22.

[0042] The invention is used with CSP packages of a variety of types and configurations such as, for example, those that are die-sized, as well those that are near chip-scale as well as the variety of ball grid array packages known in the art. Collectively, these will be known herein as chip scale packaged integrated circuits (CSPs) and preferred embodiments will be described in terms of CSPs, but the particular configurations used in the explanatory figures are not, however, to be construed as limiting. For example, the elevation views of FIGS. 1 and 2 are depicted with CSPs of a particular profile known to those in the art, but it should be understood that the figures are exemplary only. Later fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More