Method to increase charge retention of non-volatile memory manufactured in a single-gate logic process

a logic process and non-volatile memory technology, applied in the field of non-volatile memory, can solve the problems of difficult to fabricate both of these circuits on the same chip, high wafer price, and minor local degradation of gate dielectric quality, and achieve the effects of thinning or removing this structure, preventing the formation of silicide, and reducing the diffusion of metallic particles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

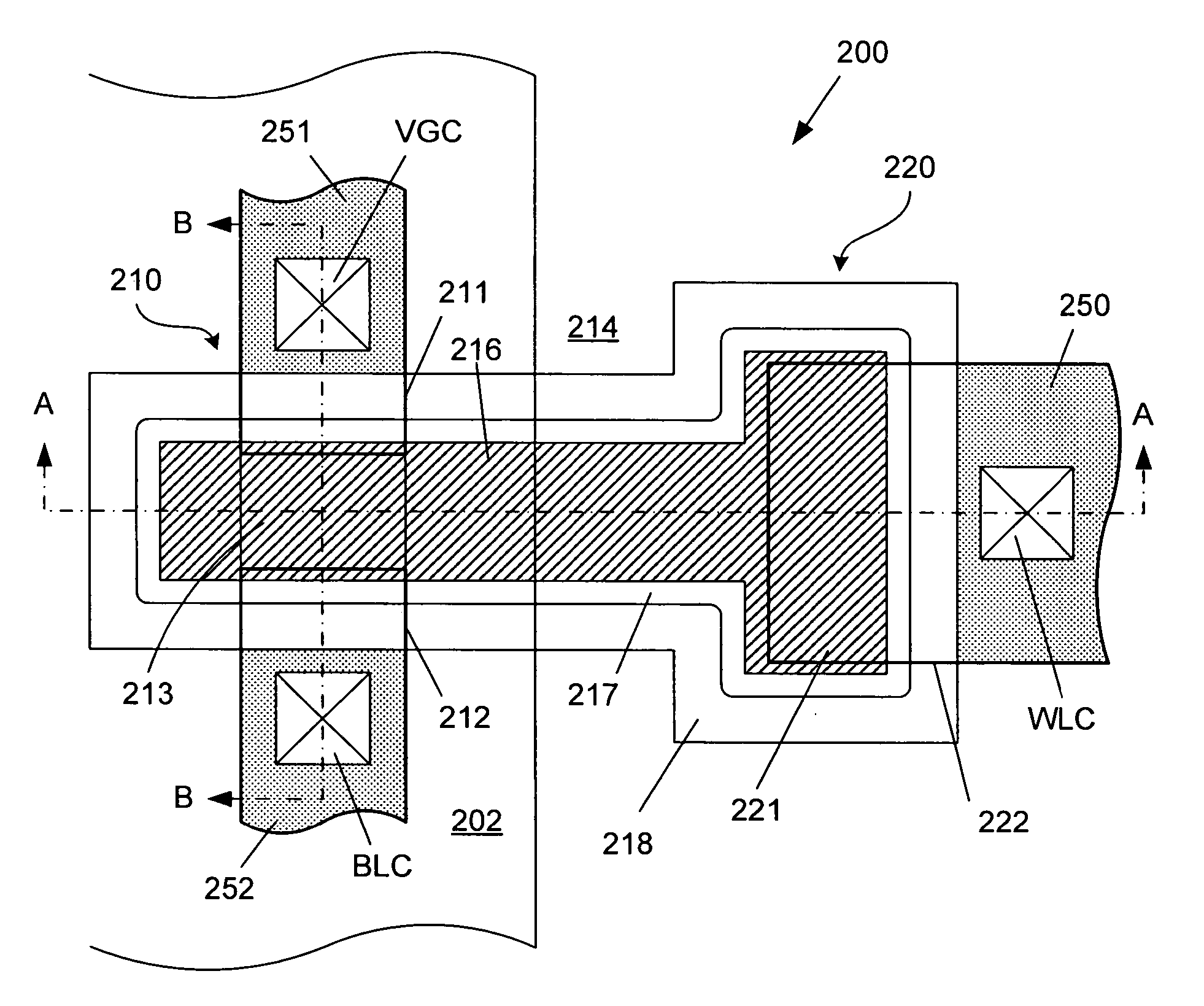

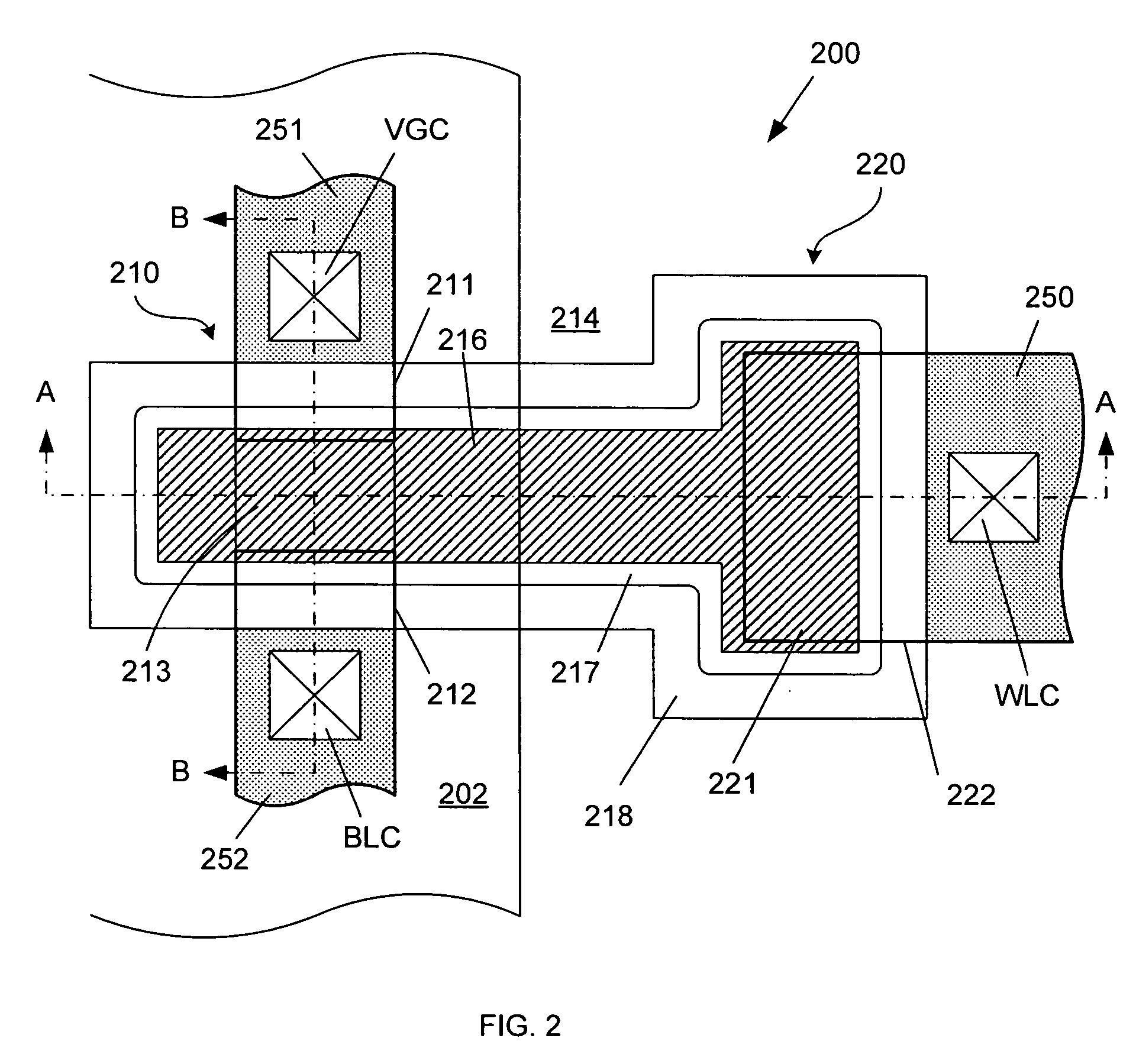

[0031]FIG. 2 is a top layout view of a non-volatile memory cell 200 in accordance with one embodiment of the present invention. FIG. 3A is a cross-sectional view of the non-volatile memory cell of FIG. 2 along section line A-A. FIG. 3B is a cross-sectional view of the non-volatile memory cell of FIG. 2 along section line B-B. Non-volatile memory cell 200 can be operated in response to a positive Vdd supply voltage and a Vss supply voltage of 0 Volts.

[0032] Note that the general layout of non-volatile memory cell 200 is similar to the layout of the NVM cell described in commonly owned U.S. Pat. No. 6,512,691 (hereinafter, the '691 Patent). The portions of the '691 Patent which describe the fabrication and operation of common elements in the NVM cell 200 of the present invention and the NVM cell of the '691 Patent are hereby incorporated by reference. Although the present invention is described using a specific NVM cell 200, it is understood that the present invention is in no way li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More