Control of Critical Dimensions of Etched Structures on Semiconductor Wafers

a technology of etched structure and critical dimension, which is applied in the direction of semiconductor devices, solid-state devices, testing/measurement of semiconductor/solid-state devices, etc., can solve the problems of cd and profile indicating processing problems, adversely affecting the performance of finished semiconductor devices, and loss of photoresis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

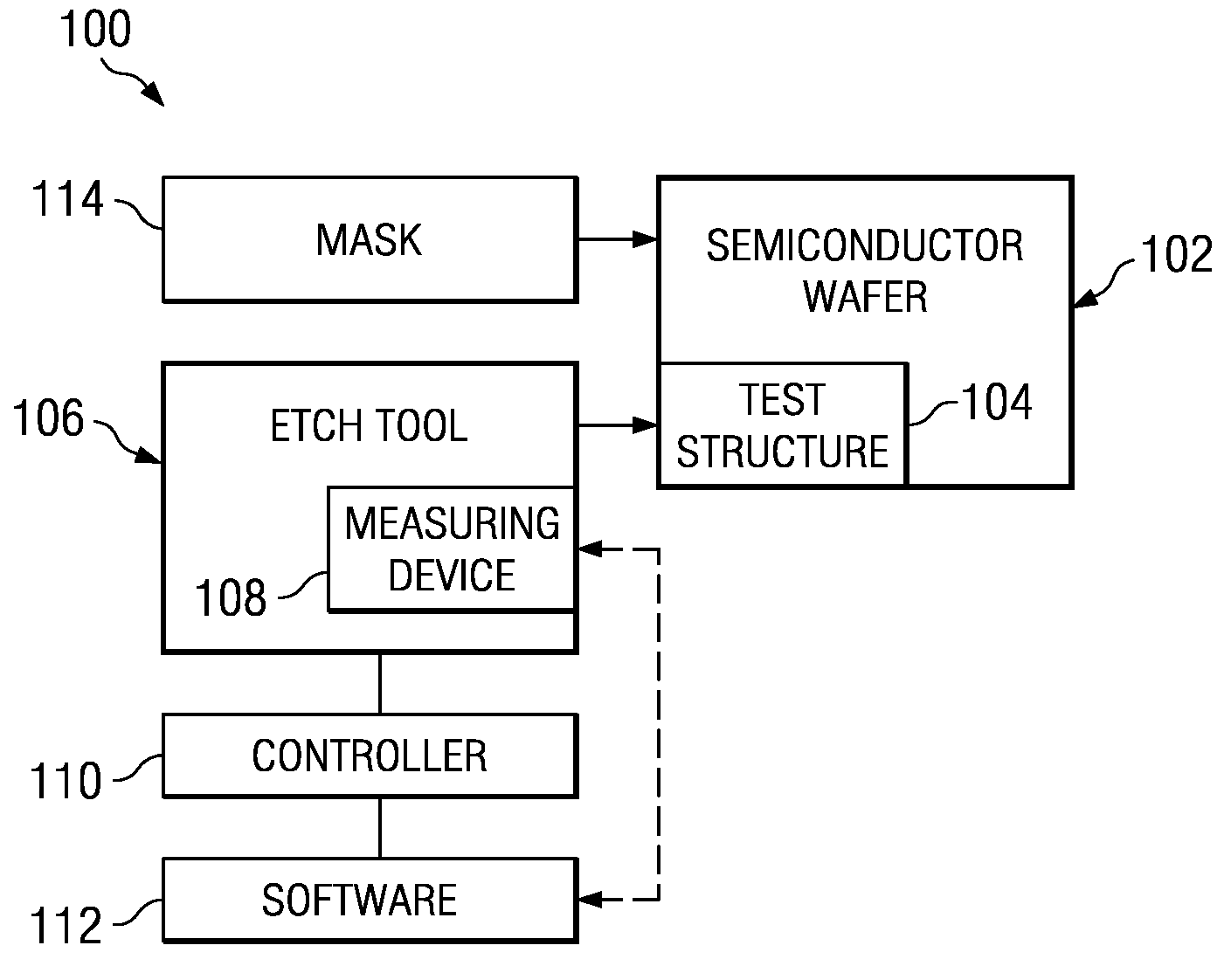

[0021]With reference now to the figures and in particular with reference to FIG. 1, a block diagram of a system in which the present invention may be implemented is depicted according to an exemplary embodiment of the present invention. The system is designated by reference number 100. Semiconductor wafer 102 is depicted, onto which test structure 104 is etched. In order to etch test structure 104 onto semiconductor wafer 102, etch tool 106 and mask 114 is used. Measuring device 108 is part of etch tool 106 and is capable of measuring the CDs of test structure 104.

[0022]As test structure 104 is being etched on the semiconductor wafer 102, measuring device 108 provides real-time, in situ measurement and feed back of the process. Measuring device 108 may be many different types of devices, including, but not limited to, a scanning electron microscope, a mechanical probe making direct electrical contact with etched structures, or a device with image recognition software capable of anal...

PUM

| Property | Measurement | Unit |

|---|---|---|

| critical dimension | aaaaa | aaaaa |

| scanning electron microscope | aaaaa | aaaaa |

| magnetic field | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More