Method for suppressing lattice defects in a semiconductor substrate

a technology of semiconductor substrate and lattice, applied in the field of semiconductor substrate fabrication, can solve problems such as crystal damage, and achieve the effect of suppressing the formation of leakage-promoting defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011]The following detailed description is made with reference to the figures. Preferred embodiments are described to illustrate the present invention, not to limit its scope, which is defined by the claims. Those of ordinary skill in the art will recognize a variety of equivalent variations on the description that follows.

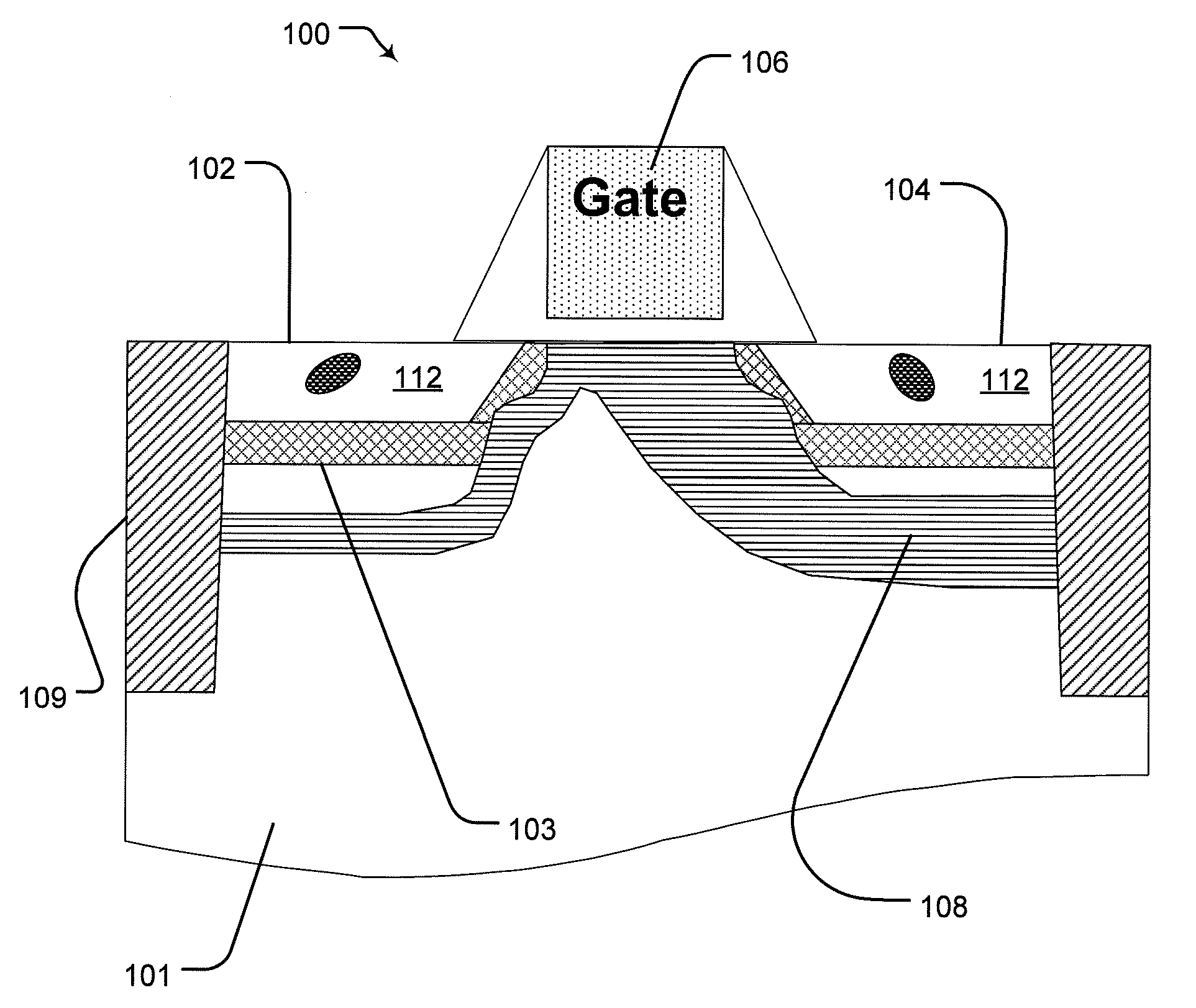

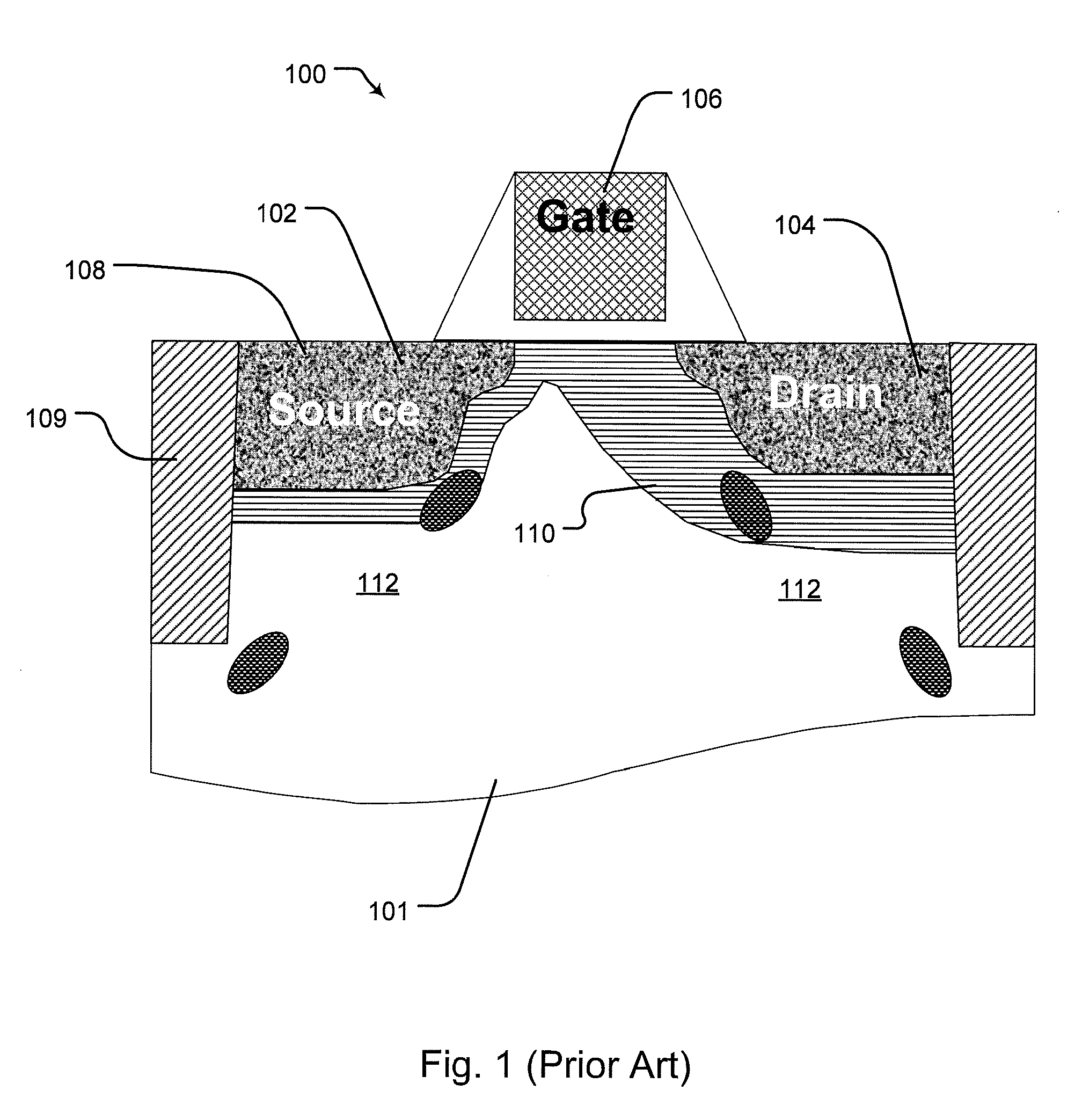

[0012]The problem addressed by the present disclosure is seen in FIG. 1, which depicts a typical MOSFET 100 after undergoing ion implantation. The transistor is formed on a silicon substrate 101 and includes source 102, drain 104 and gate 106. The depletion layer 108 adjacent each electrode and extending across the channel between the source and drain, is well known in the art. The depicted cell is one member of an array that can encompass millions of cells, as known in the art, and the cell is separated from other members of the array by Shallow Trench Isolators (STI) 109, filled with dielectric fill material.

[0013]The source and drain are formed in the silicon ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More