Stacked memory device with metadata mangement

a memory device and metadata technology, applied in the field of memory devices, can solve the problems of significant performance bottlenecks in the bandwidth and latency of the memory bandwidth and latency, and the system implementing 3d stacked memory can continue to be bandwidth-limited

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

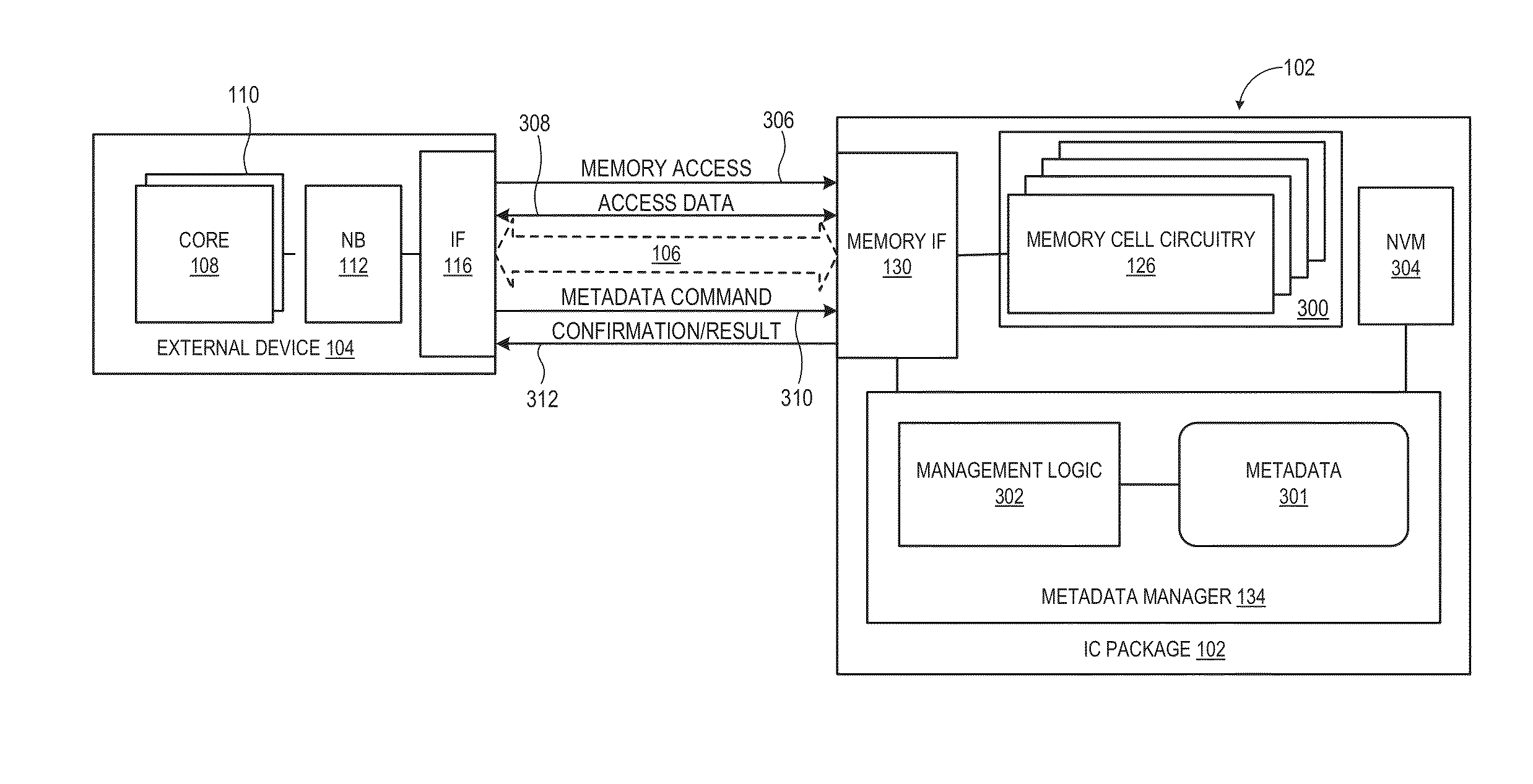

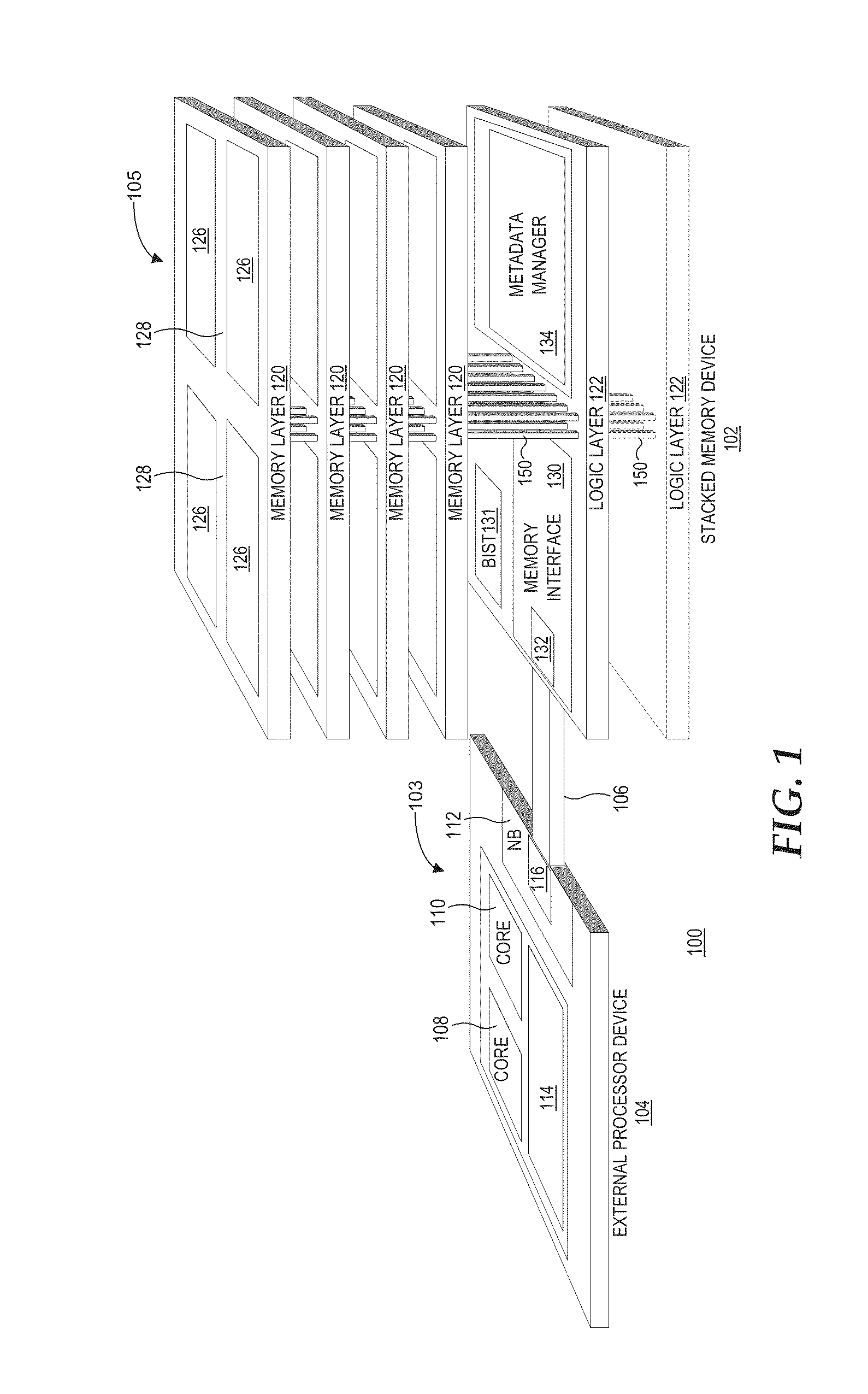

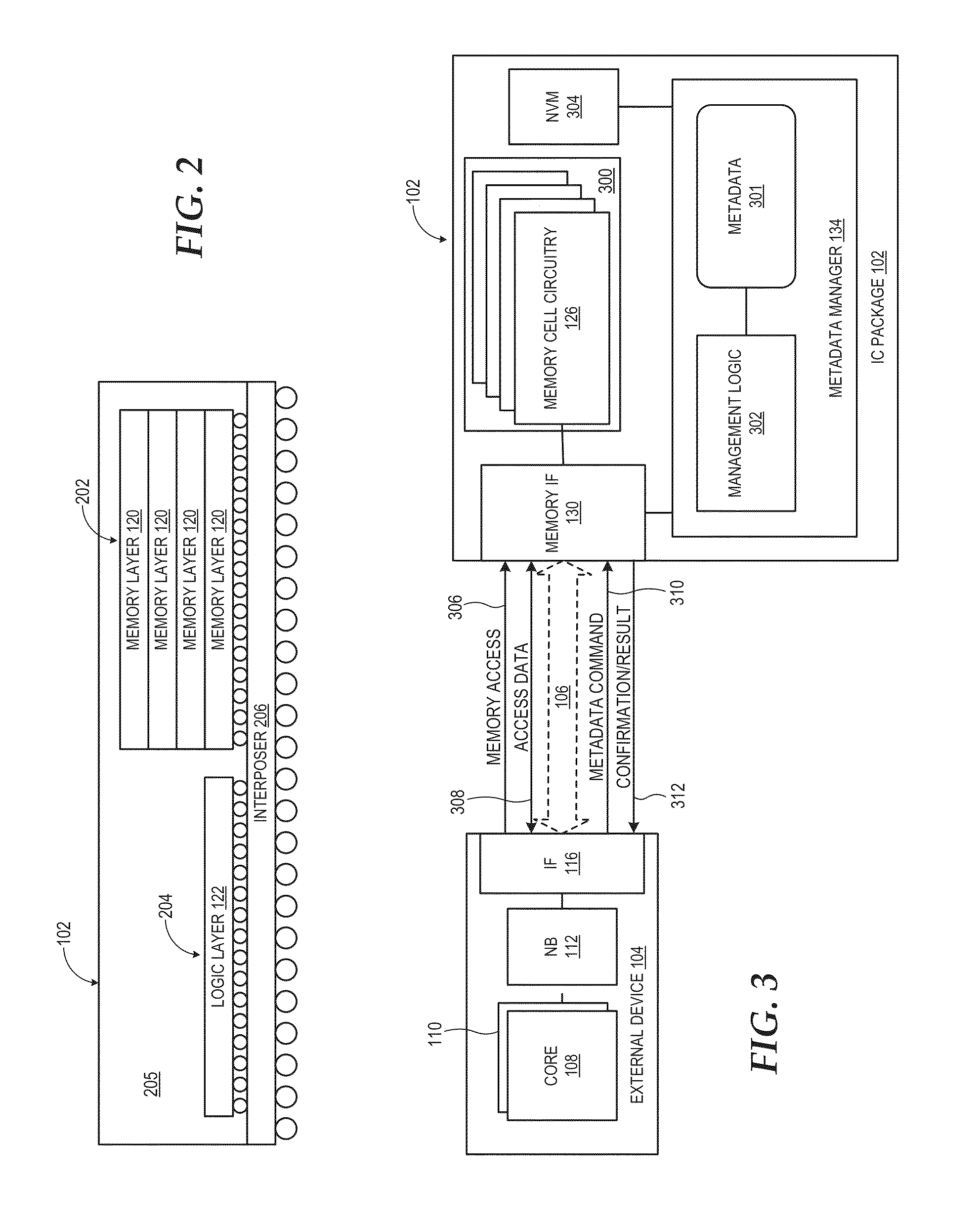

[0022]FIGS. 1-14 illustrate example techniques for improved processing efficiency and decreased power consumption in a processing system through the use of a stacked memory device implementing an integrated metadata manager to offload metadata management for operational data stored in memory cell circuitry of the stacked memory device. The stacked memory device includes a set of stacked memory layers and a set of one or more logic layers, wherein the one or more logic layers implement the metadata manager and a memory interface. The memory interface is coupled to the memory cell circuitry and is coupleable to one or more devices external to the stacked memory device. The memory interface operates to perform memory accesses in response to memory access requests from both the metadata manager and the one or more external devices. The metadata manager comprises logic to perform one or more metadata management operations for metadata stored at the stacked memory device in association wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More