Ias voltage generator for reference cell and bias voltage providing method therefor

a reference cell and bias voltage technology, applied in static storage, digital storage, instruments, etc., can solve the problems of deterioration of memory cells, read disturb, and longer time length of bias voltage applied to reference cells, so as to achieve effective mitigation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

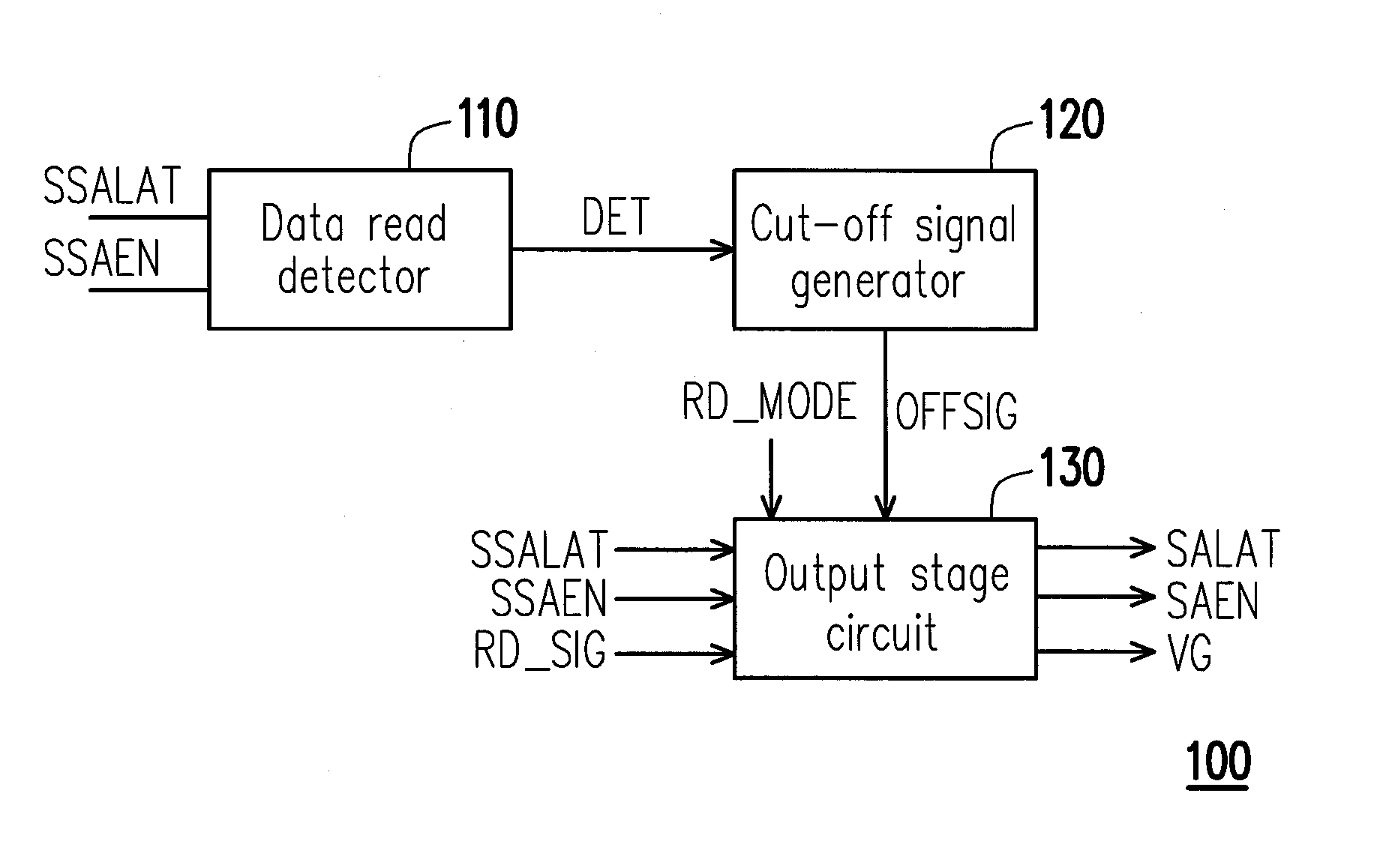

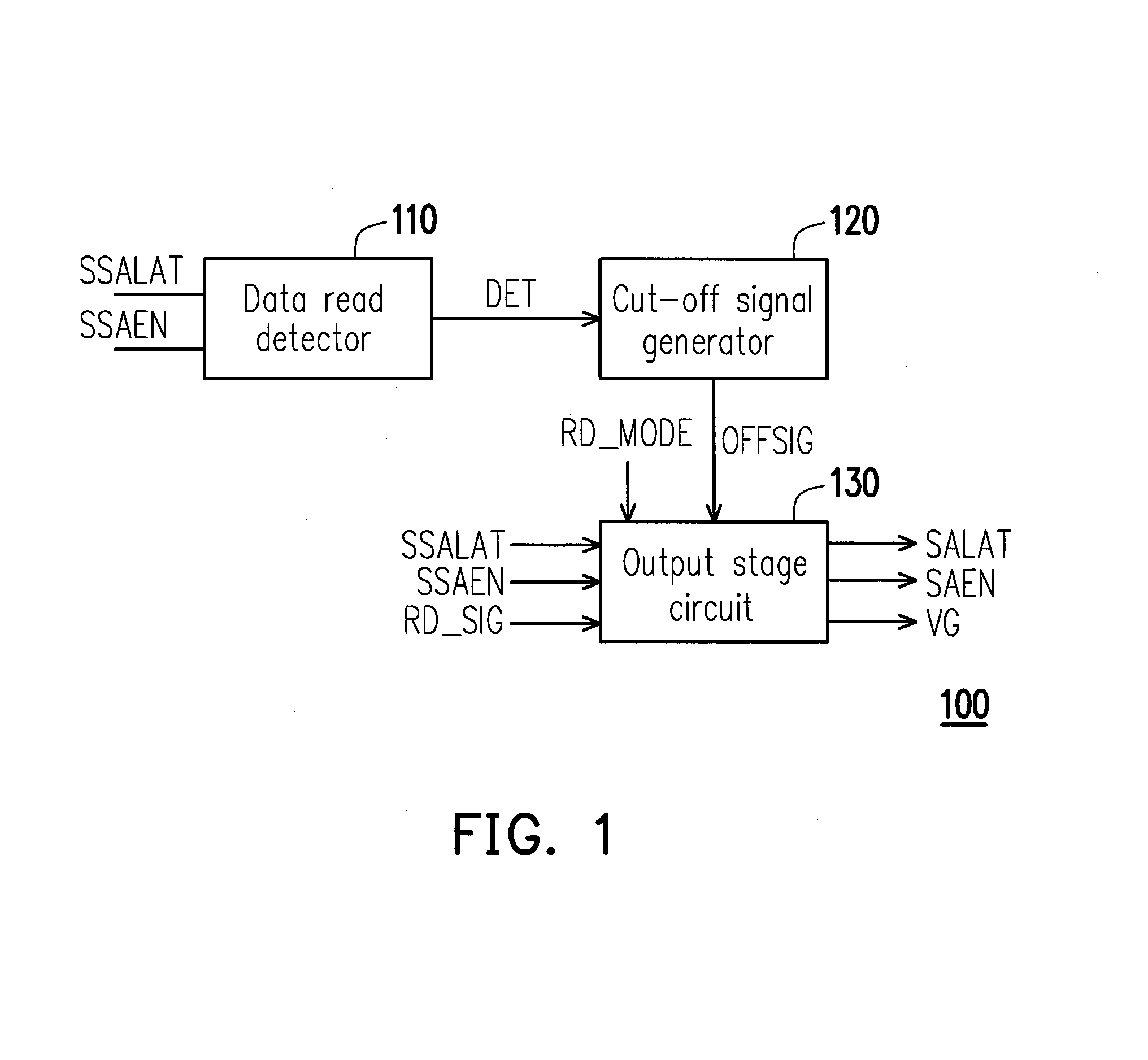

[0019]With reference to FIG. 1, FIG. 1 is a schematic diagram illustrating a bias voltage generator 100 for a reference cell. The bias voltage generator 100 is adapted to a serial interface flash memory, such as a serial peripheral interface (SPI) flash memory. The bias voltage generator 100 includes a data read detector 110, a cut-off signal generator 120 and an output stage circuit 130. The data read detector 110 receives a sense amplifier enable signal SSAEN and a sense amplifier latch signal SSALAT, which are clock signals in a synchronized clock system, and generates a detection signal DET according to transition points of the sense amplifier enable signal SSAEN and the sense amplifier latch signal SSALAT. The cut-off signal generator 120 is coupled with the data read detector 110. The cut-off signal generator 120 receives and delays the detection signal DET for a time delay to generate a cut-off signal OFFSIG. A start-up time of the cut-off signal OFFSIG is decided according t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More