SCR controlled by the power bias

a power bias and power bias technology, applied in the field of circuit protection, can solve the problems of nodes that connect to power supplies, excessive current, and more of a problem of catching up

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

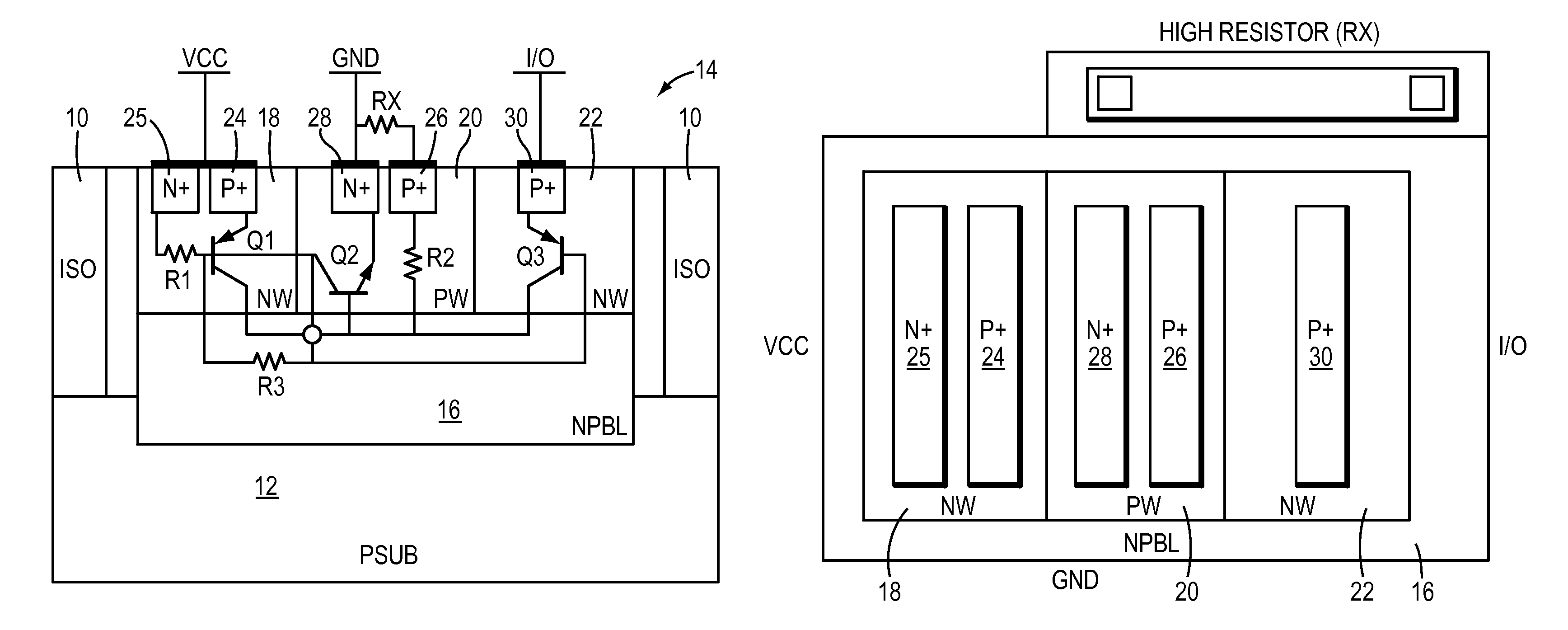

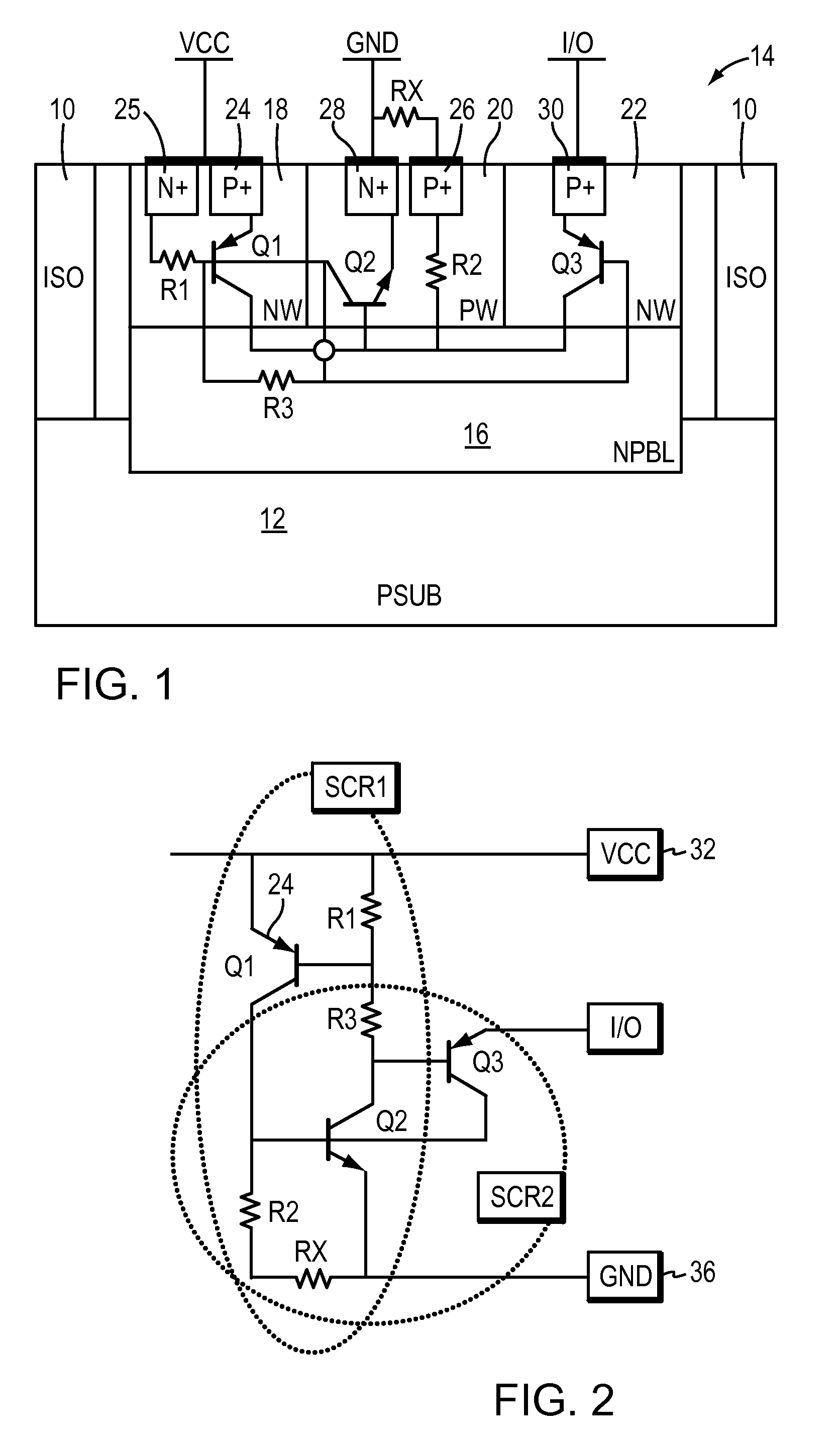

[0023]FIG. 1 shows an IC (integrated circuit) composite dual SCR and FIG. 2 is an equivalent circuit schematic. The dual SCR 14 shares a common circuit element, the NPN bipolar transistor Q2 of FIG. 2.

[0024]FIG. 1 shows isolation diffusions, ISOs 10, that connect to the P-type substrate 12 and isolate the dual SCR 14. An NPBL (N+-type buried layer) 16 underlies the dual SCR. Two NW 18 and 22 (N-type Wells) wells are formed on either side of a P+ well 20 that penetrates to the NPBL 16. A P+ electrode 24 is diffused in the NW 18 to form the emitter of PNP Q1. Q1 base is brought to an N+ electrode 25, and the base and the emitter of Q1 are connected together and tied to Vcc. An inherent resistor R1 exists in the base connection since the N-type structure 18 is not highly doped. The collector of Q1 connects via the NPBL 16 to the P+ electrode 26 in the P-type structure 20 through the resistance R2.

[0025]The base of Q1 also forms the collector of the NPN Q2, and the NPBL 16 forms the bas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More