Program circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

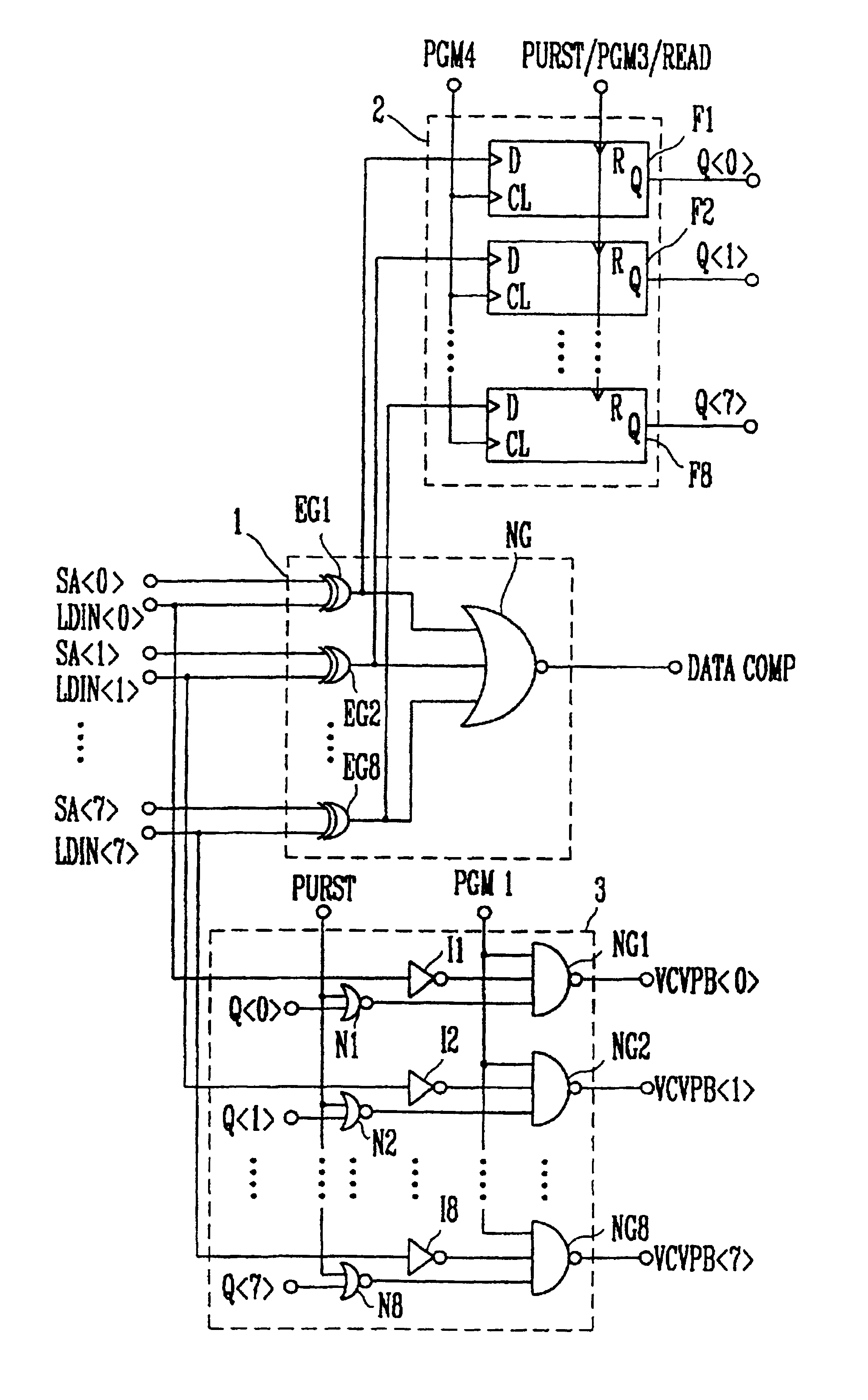

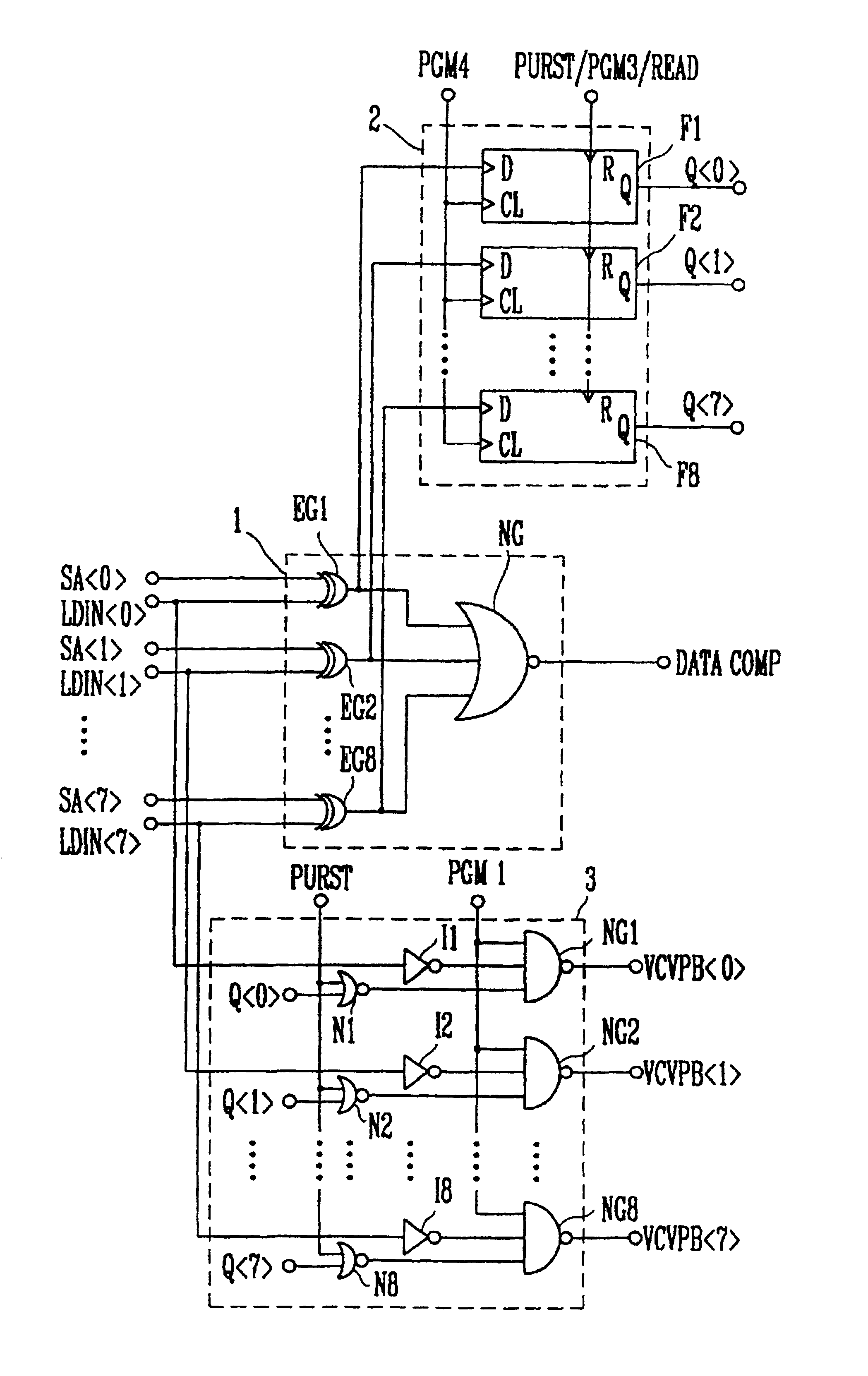

[0014]The accompanying drawing is a circuit diagram for explaining a program circuit according to the present invention.

[0015]The program circuit according to the present invention is consisted of a comparator 1, a data latch circuit 2, and a control circuit for generating a high voltage 3, and added to the flash memory device.

[0016]The comparator 1 comprises of a plurality of exclusive NOR gates EG1 through EG8 to which output data LDIN0 through LDIN7 of a data input buffer and output data SA0 through SA7 of a sense amplifier are inputted, respectively. Also, the comparator 1 comprises a NOR gate NG to which output signals of the exclusive NOR gates EG1 through EG8 are inputted. The NOR gate NG outputs logical combination signals via an output terminal DATA COMP.

[0017]The data latch circuit 2 is consisted of a plurality of flip-flops F1 through F8. Each of flip-flops F1 through F8 comprises a data input terminal D to which an output signal of one of the exclusive NOR gates EG1 thro...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap