Dual mosaic structure, interconnect structure and methods for fabricating the same

A technology of dual damascene structure and internal connection structure, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve problems affecting the reliability of integrated circuit devices, peeling, and forming holes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] Hereinafter, the description "low dielectric constant" is used to indicate a lower dielectric constant than that of conventional silicon dioxide. Preferably, low dielectric constant refers to a dielectric constant lower than 4.

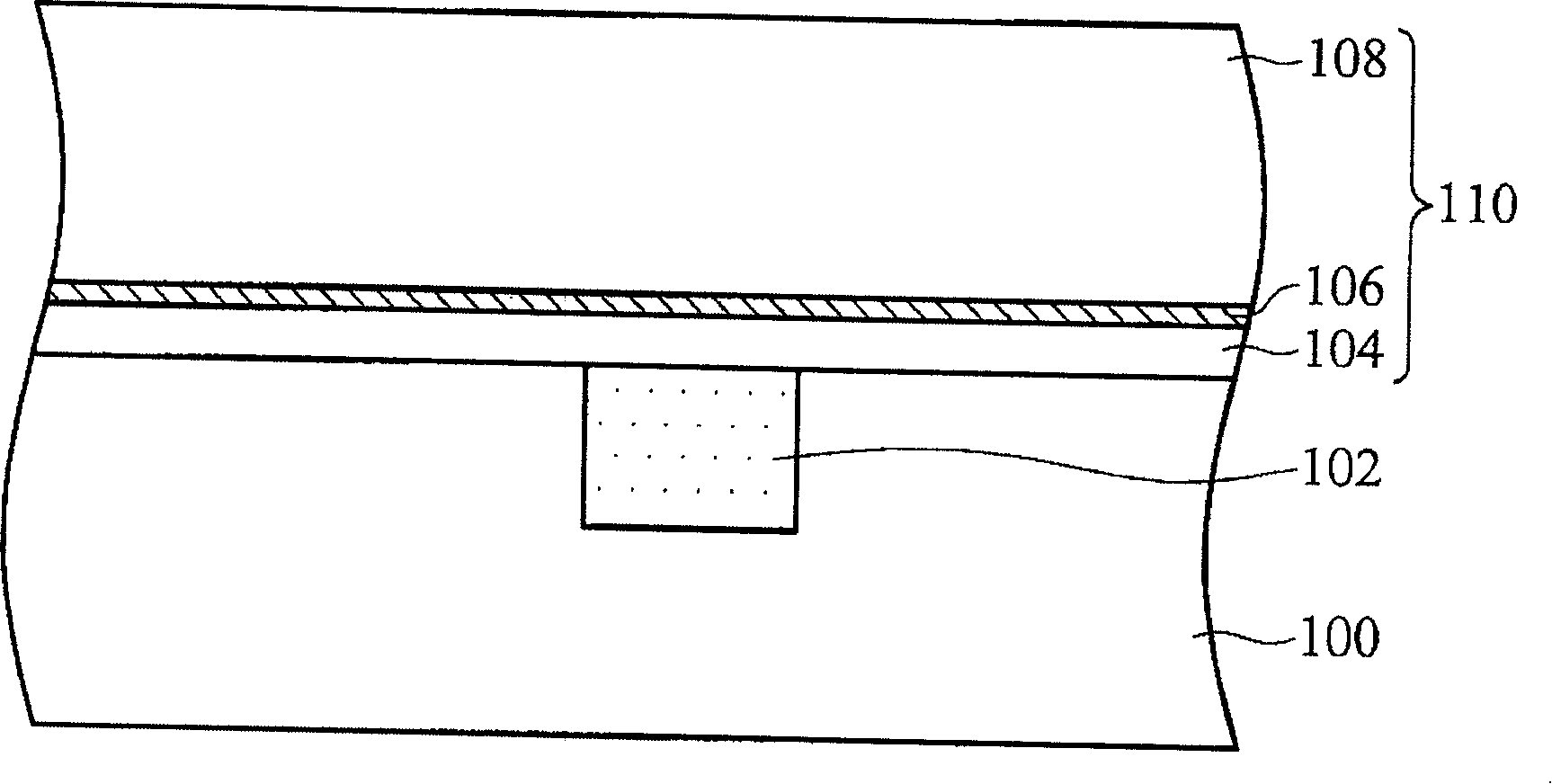

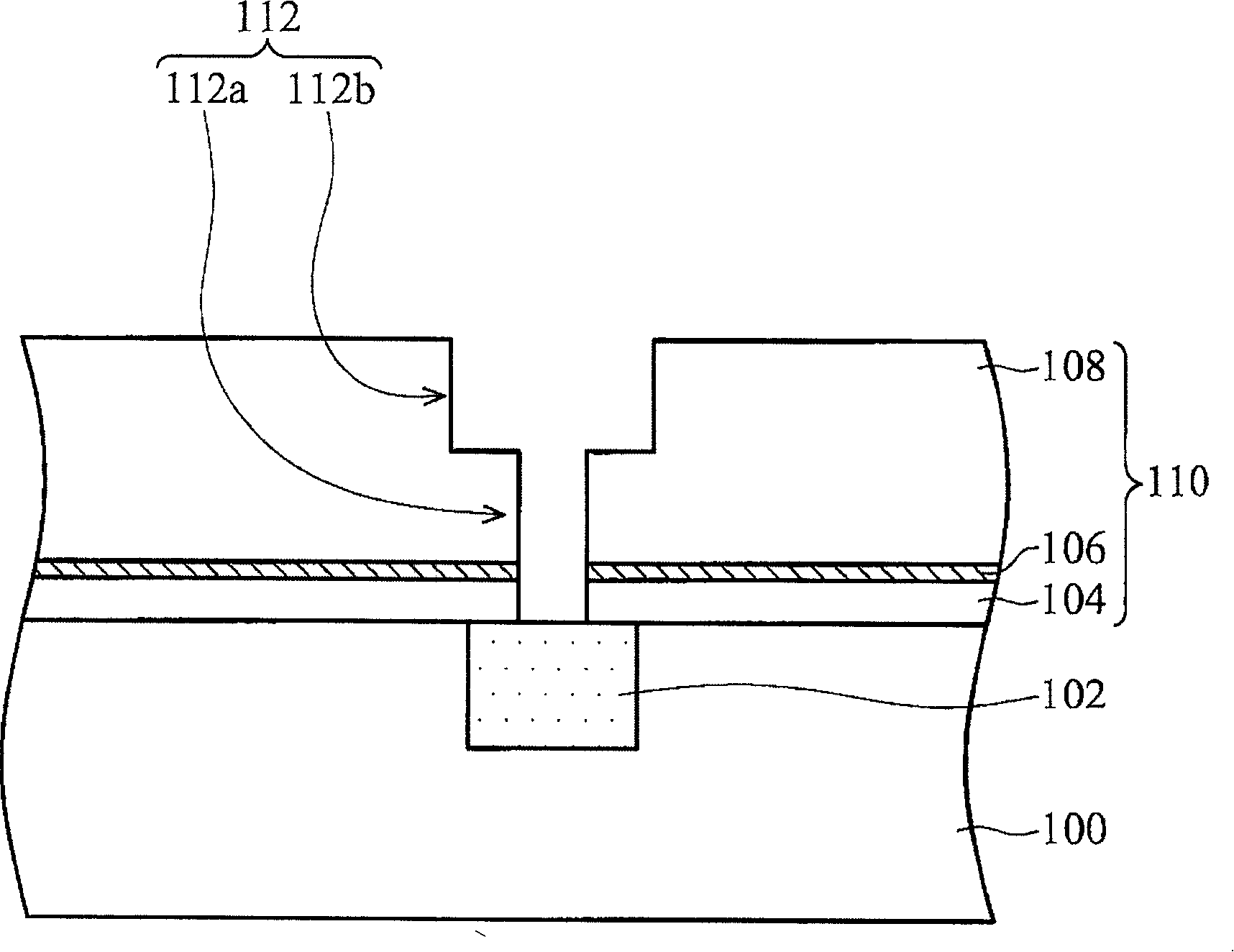

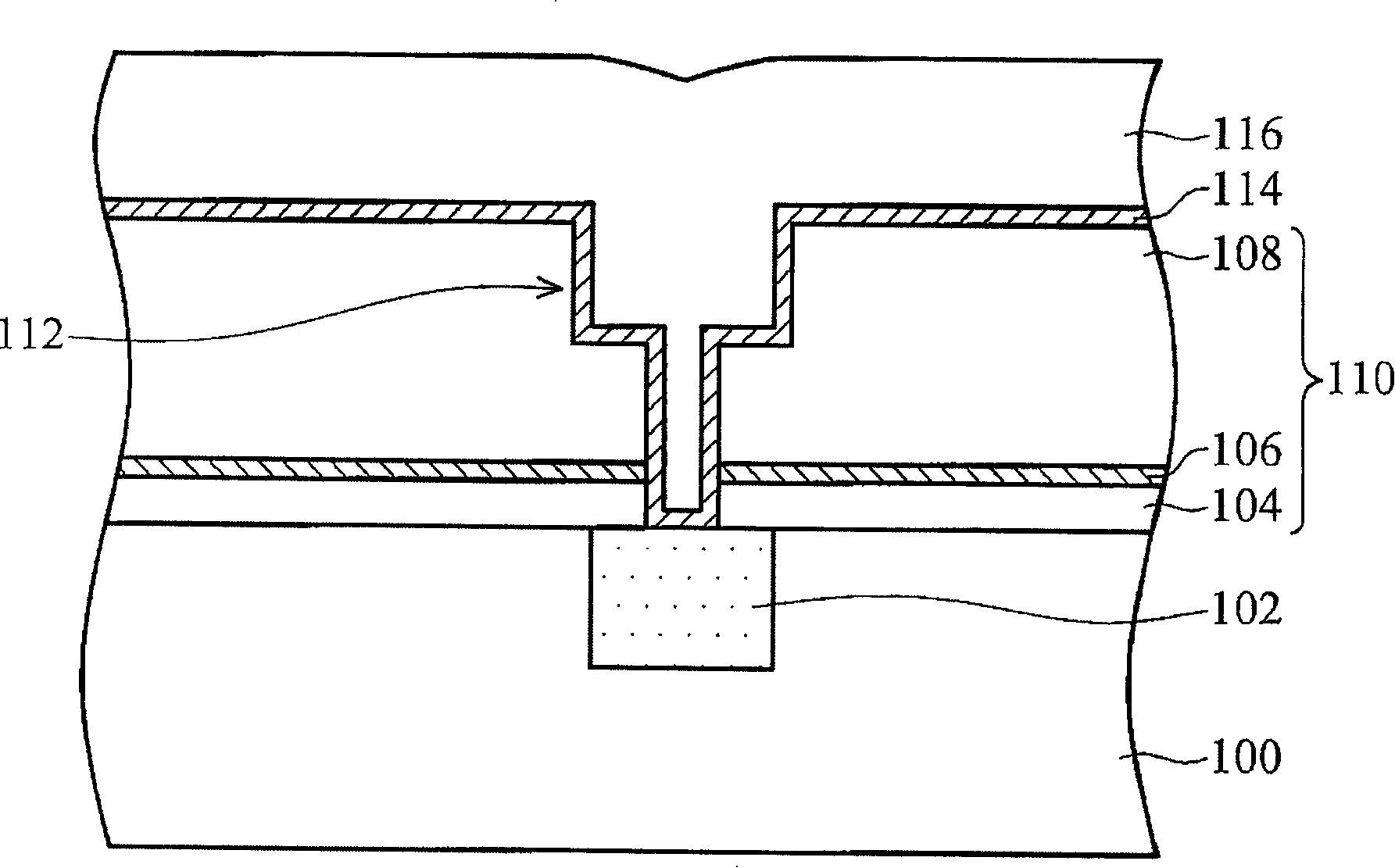

[0039] Embodiments of the interconnect structure and method of manufacture of the present invention will cooperate with Figure 1 to Figure 4 Describe in detail as follows. Please refer to figure 1 As shown, a semiconductor substrate is provided on which semiconductor devices and other conductive structures are disposed. To simplify the drawing, a flat substrate 100 is shown here. In addition, if figure 1 As shown, a conductive member 102 is formed in the substrate 100, which may be electrically coupled to a semiconductor device or a wire (not shown) therebelow.

[0040] Next, the low-k dielectric layers 104 , 108 with the first stress type and the stress adjustment layer 106 with the second stress type are alternately formed on the subs...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More