Stack structure for metal inlay, forming method and metal inlay method thereof

A technology of metal damascene and stack structure, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems affecting the yield of the process, and achieve the effect of alleviating problems and reducing reactions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

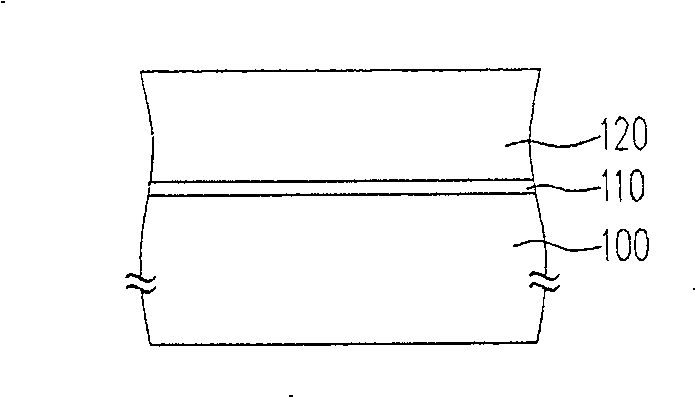

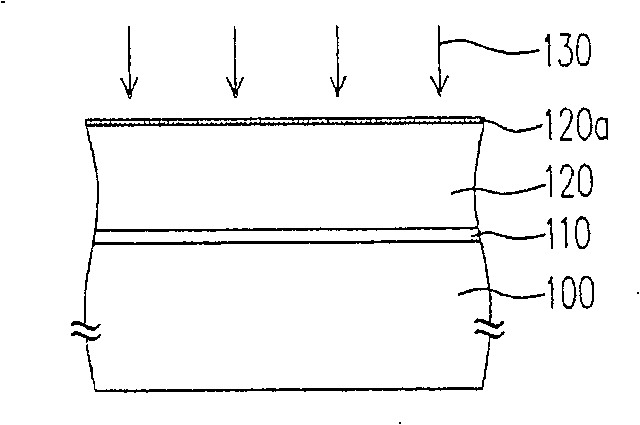

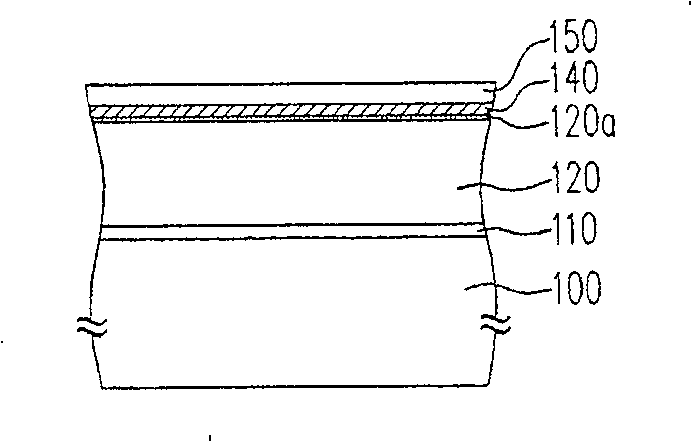

[0034] The specific example of the forming method of the stacked layer of the present invention will coordinate Figure 1A to Figure 1C Details are as follows.

[0035] Please refer to Figure 1A , forming a dielectric layer 120 on the substrate 100 . The material of the dielectric layer 120 is, for example, a low dielectric constant material with a dielectric constant lower than 4, such as fluorine doped glass (FSG) or carbon doped glass (Si—O—C). Usually, before forming the dielectric layer 120 , there is already a capping layer 110 on the substrate 100 , the material of which is eg silicon nitride or silicon oxynitride.

[0036] Please refer to Figure 1B After the dielectric layer 120 is formed, a processing step 130 is performed to reduce the doping concentration of the upper surface layer 120 a of the dielectric layer 120 . The processing step 130 is, for example, a plasma processing procedure, so that the doping concentration of the dielectric layer 120 at the upper...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More