Preparation method of fin channel dual-bar multi-functional field effect transistor

A field effect transistor and multifunctional technology, which is applied in the field of fin-channel double-gate multifunctional field effect transistor and its preparation, can solve the problem of affecting the DC characteristics and reliability of the device, long programming/erasing time, and affecting the reliability of the device. and other problems, to achieve the effect of improving programming/erasing speed, improving DC characteristics and reliability, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] The fin channel dual-gate multifunctional field effect transistor provided by the present invention and its preparation method will be described in detail below in conjunction with the accompanying drawings, but this does not constitute a limitation to the present invention.

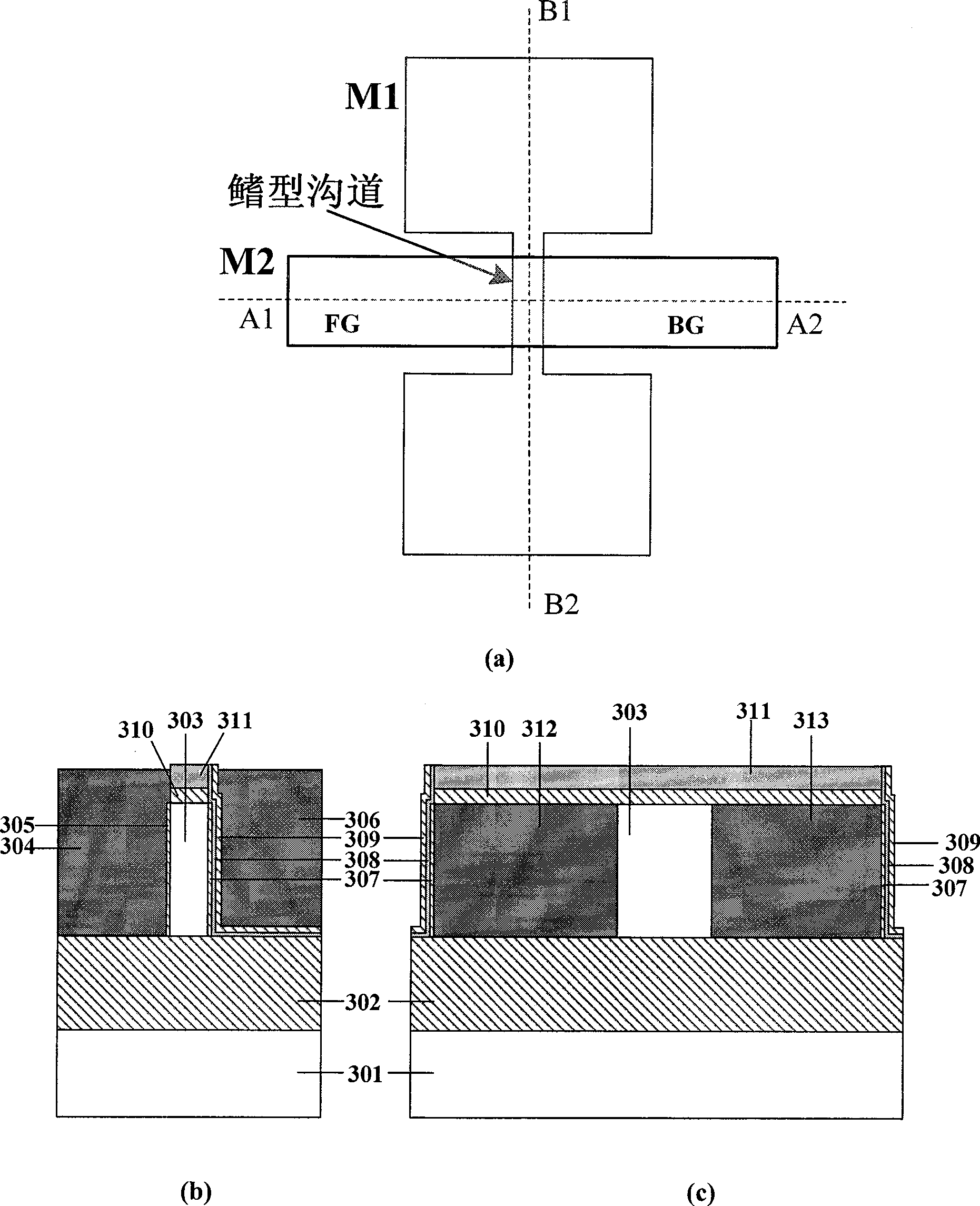

[0058] Such as image 3 Shown in (a)-(c) are the fin-type channel dual-gate multifunctional field effect transistors of this embodiment. The device is based on SOI substrate. Such as image 3 (a) shows the layout of the device, M1 is the active area version, and M2 is the gate version. Such as image 3 (b) and (c) are the cross-sectional structures of the device along the vertical direction of the channel (A1A2 direction) and along the channel direction (B1B2 direction), respectively. From the cross-sectional structure along the vertical direction of the channel, the field effect transistor is located on the silicon dioxide buried layer 302 of the SOI substrate, and the cross section of the ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More