Chip package body

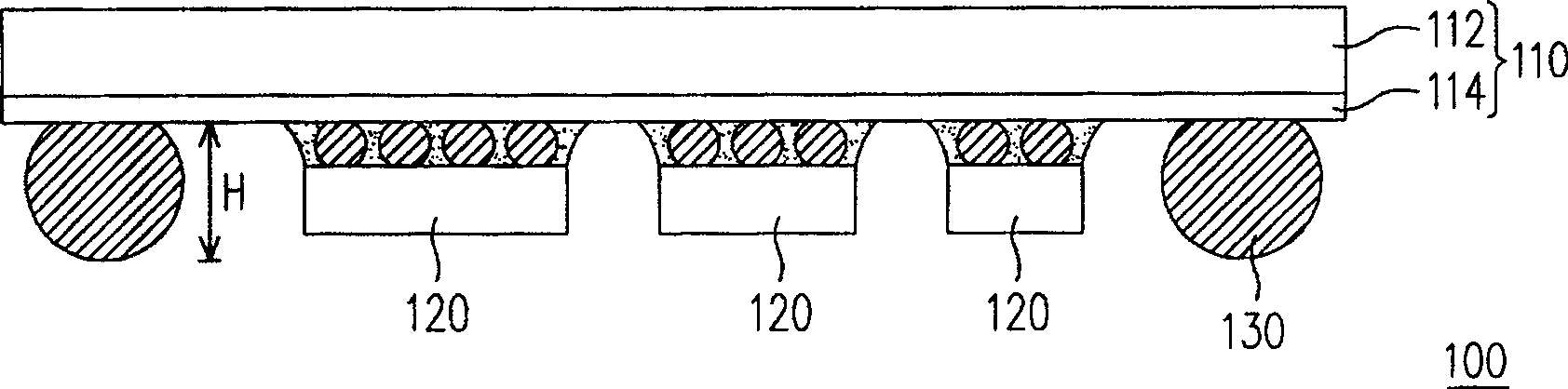

A chip packaging and chip technology, which is applied to semiconductor devices, electric solid-state devices, semiconductor/solid-state device components, etc., can solve the problem of low utilization rate of bearing space, inability to reduce, and shorten the distance between the chip package body 100 and the next-level electronic device and other problems to achieve the effect of high component configuration density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the above-mentioned features and advantages of the present invention more comprehensible, a detailed description is given below of preferred embodiments in conjunction with the accompanying drawings.

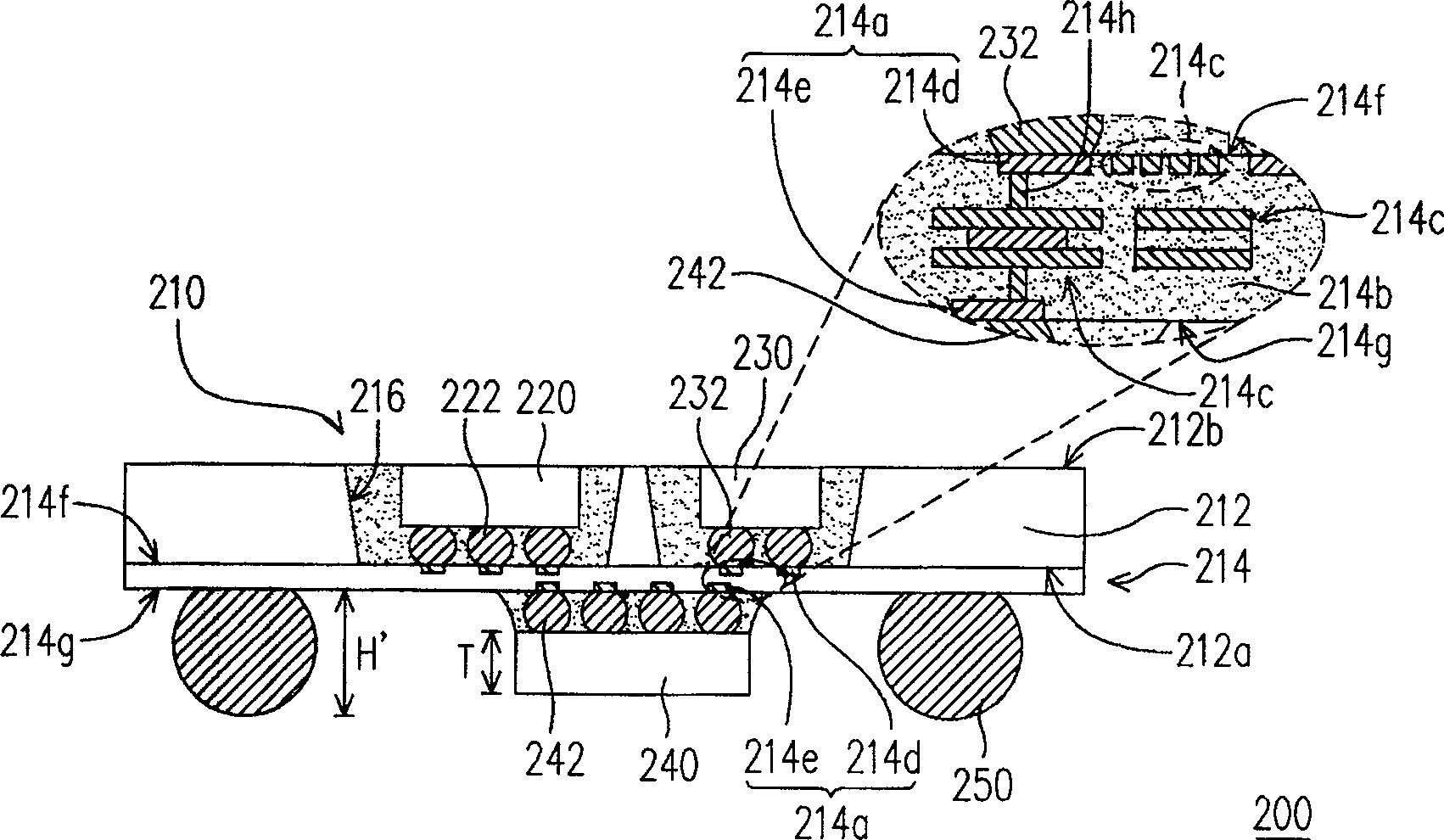

[0015] Please refer to figure 2 , Which shows a schematic side view of a chip package according to the first embodiment of the present invention. The chip package 200 includes a carrier 210 and a plurality of chips 220, 230, and 240. The carrier 210 includes a silicon substrate 212 and an integrated passive device layer 214. The silicon substrate 212 has two surfaces 212a and 212b opposite to each other. The integrated passive device layer 214 is disposed on the surface 212a. The chips 220, 230, and 240 are respectively disposed above the two opposite sides of the integrated passive device layer 214 and are electrically connected to the integrated passive device layer 214.

[0016] Since the chips 220, 230, and 240 are respectively disposed on opposite sides...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More