Memory device

A storage device and storage unit technology, applied in information storage, static memory, digital memory information, etc., can solve the problems of thermal deterioration of wiring, difficulty in realizing 3-dimensional capacitor array, and the need for polycrystallization, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

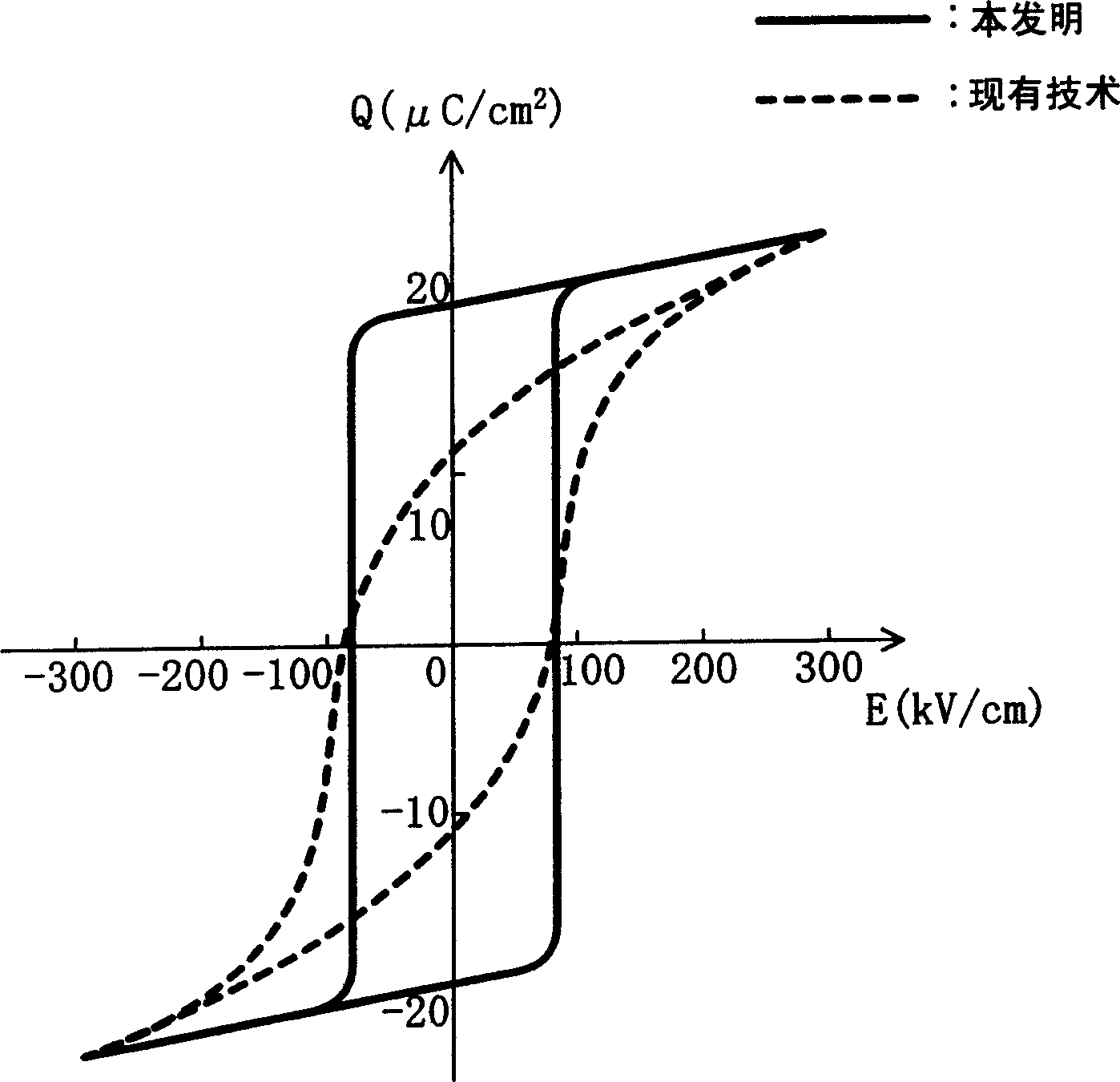

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

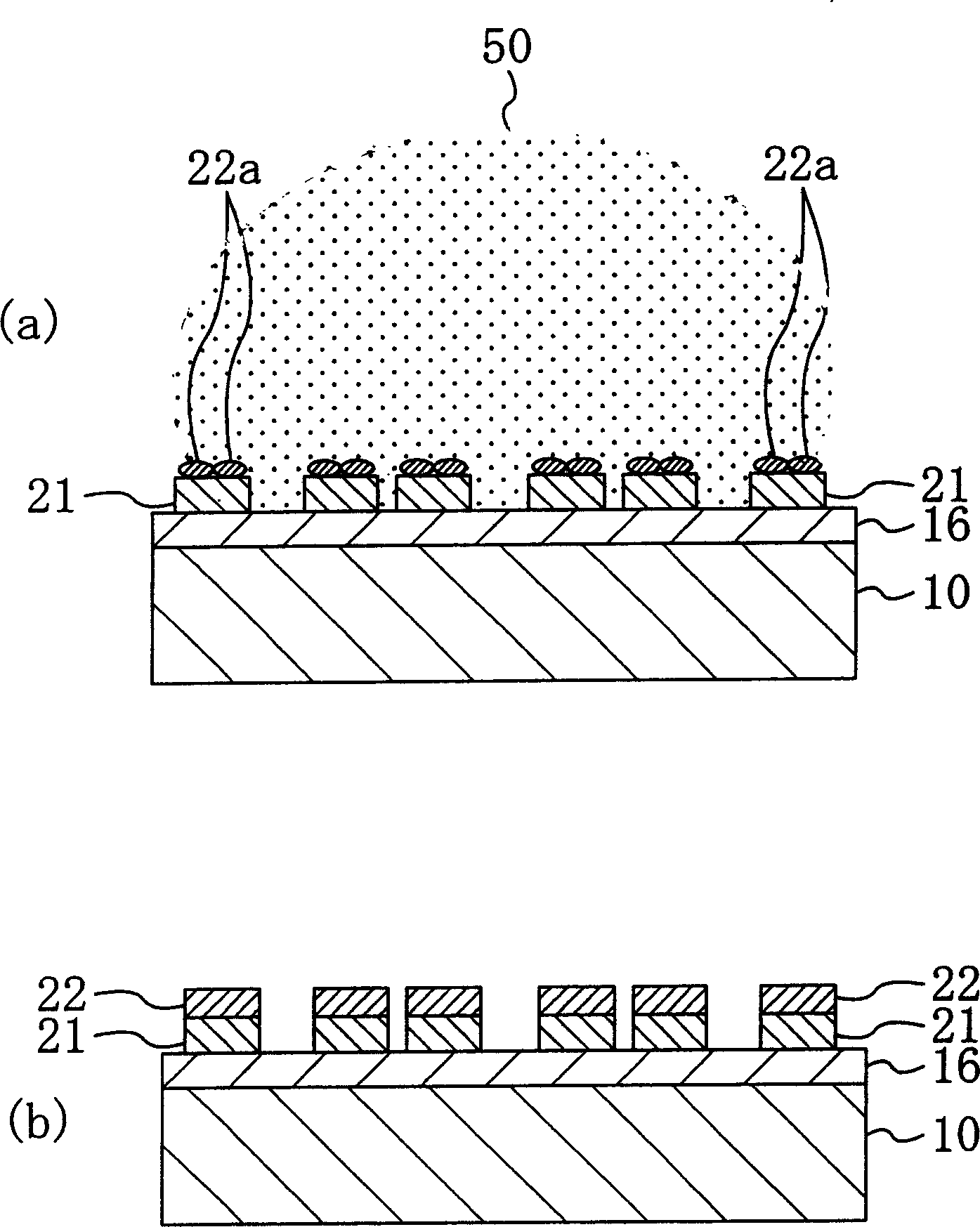

[0046] A first embodiment of the present invention will be described below with reference to the drawings.

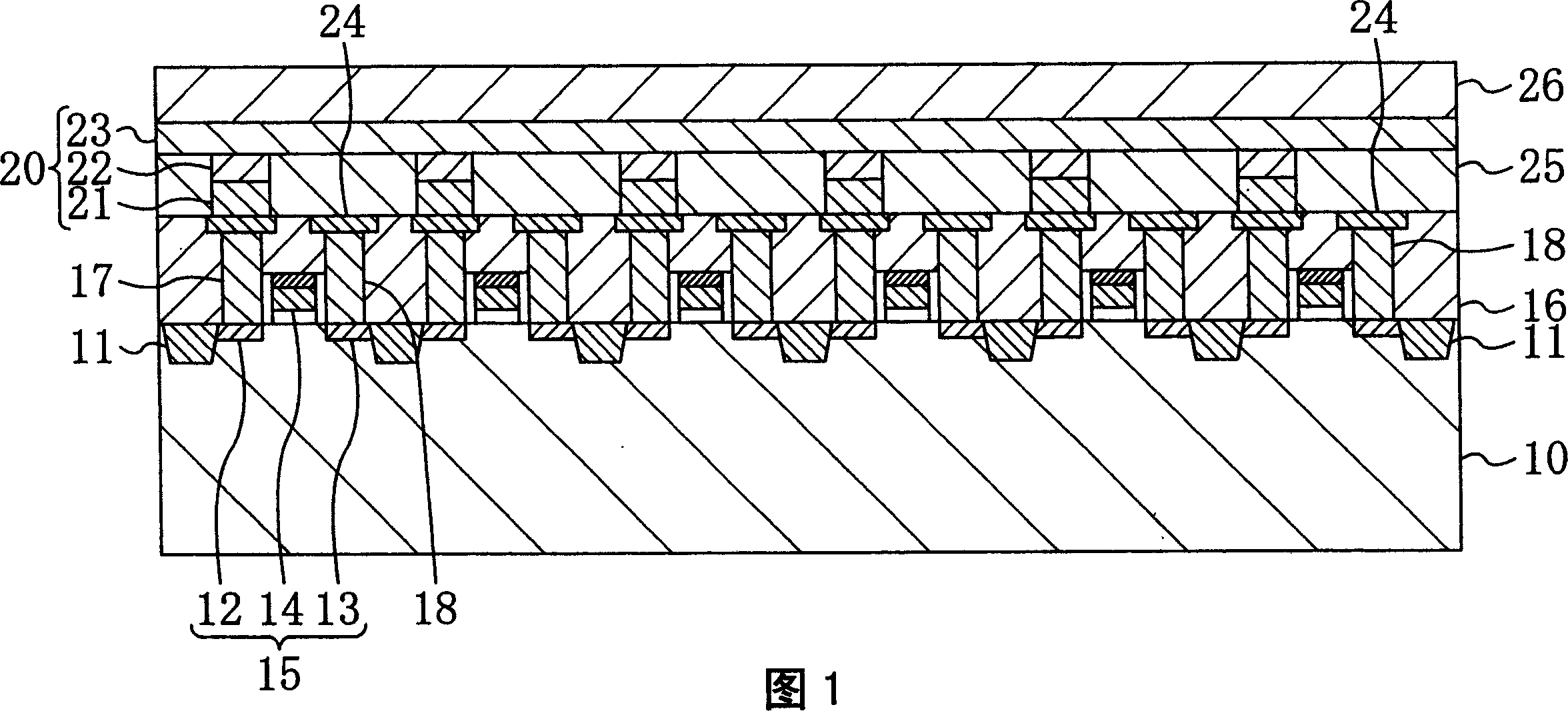

[0047] FIG. 1 is a cross-sectional view showing the structure of a memory cell array which is a main part of a memory device according to a first embodiment of the present invention.

[0048] As shown in FIG. 1 , a plurality of device regions divided by a plurality of device isolation regions 11 made of silicon oxide are formed on an upper portion of a semiconductor substrate 10 made of, for example, silicon. In each element region, a selection transistor 15 is formed as a switching element for selection. Each selection transistor 15 includes a source region 12 and a drain region 13 formed at intervals, and a gate 14 formed in a region between the source region 12 and the drain region 13 on the semiconductor substrate 10 .

[0049] The first insulating layer 16 is formed on the entire surface including each element isolation region 11 and each gate electrode 14 on the ...

no. 2 Embodiment

[0069] A second embodiment of the present invention will be described below with reference to the drawings.

[0070] 4 is a cross-sectional view showing the configuration of a memory cell array, which is a main part of a memory device according to a second embodiment of the present invention. In the second embodiment, the memory cell array is three-dimensional, that is, arranged by stacking two layers, so as to increase the arrangement density of the memory cells. In FIG. 4, the same components as those shown in FIG. 1 are denoted by the same reference numerals, and description thereof will be omitted here.

[0071] As shown in FIG. 4 , a peripheral circuit 40 including a selection transistor 15 , a first capacitor array layer 41 and a second capacitor array layer 42 in which a plurality of capacitors are arranged in an array are sequentially formed on a substrate 10 .

[0072] The first cell plate line 32A is formed after interposing the second insulating layer 31 between th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More