Making method for memory capacitor

A technology for storage capacitors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., to achieve the effect of improving effective doping concentration and conductivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

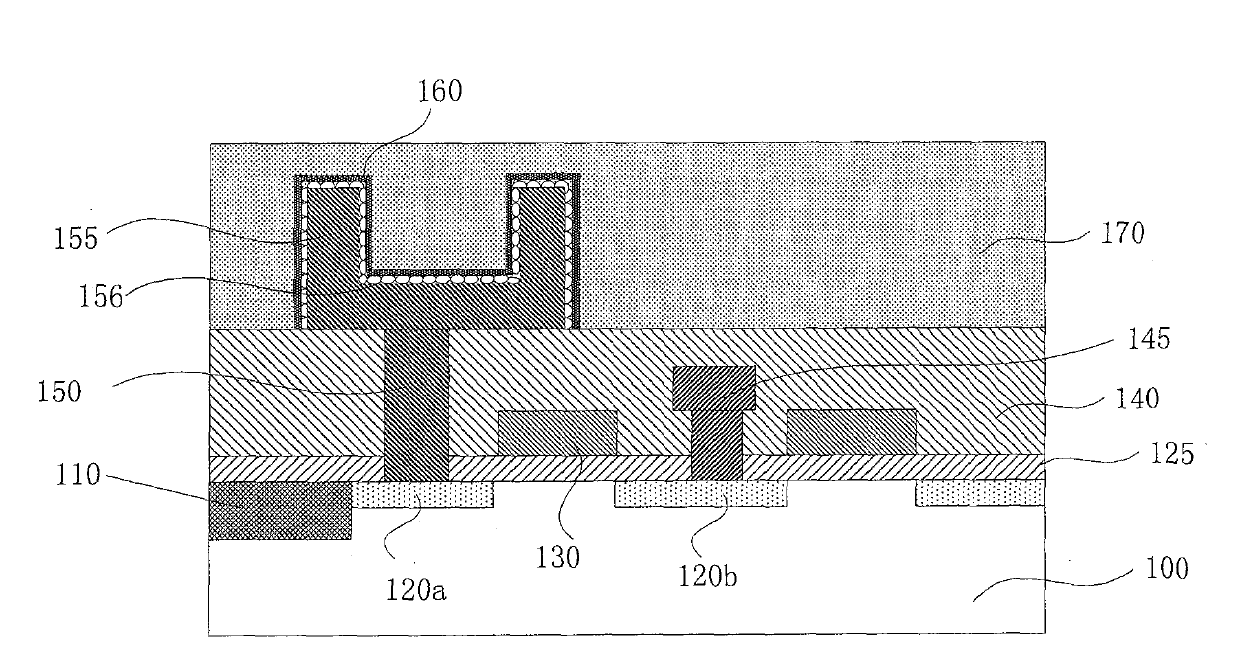

[0064] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0065] image 3 It is a flow chart of the first embodiment of the manufacturing method of the present invention.

[0066] Such as image 3 As shown, a semiconductor substrate is provided on which a device layer, such as a metal oxide transistor (MOS), is formed. The metal oxide transistor includes a source, a drain and a gate, and a conductive channel is formed between the source and the drain. An insulating layer is deposited on the substrate on which the metal oxide transistor is formed, and a connection hole is formed by etching on the insulating layer ( S400 ).

[0067] Forming a capacitor first plate, such as doped polysilicon, on the insulating layer (S410). The first pole plate is electrically connected to the source of the MOS transistor on the substrate through the connection hole on the insulating layer. The thickness and sha...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More