Grid dielectric layer manufacturing method

A manufacturing method and technology of gate dielectric layer, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as low silicon-hydrogen bond energy, reduce threshold voltage, improve mobility, and improve reliability degree of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

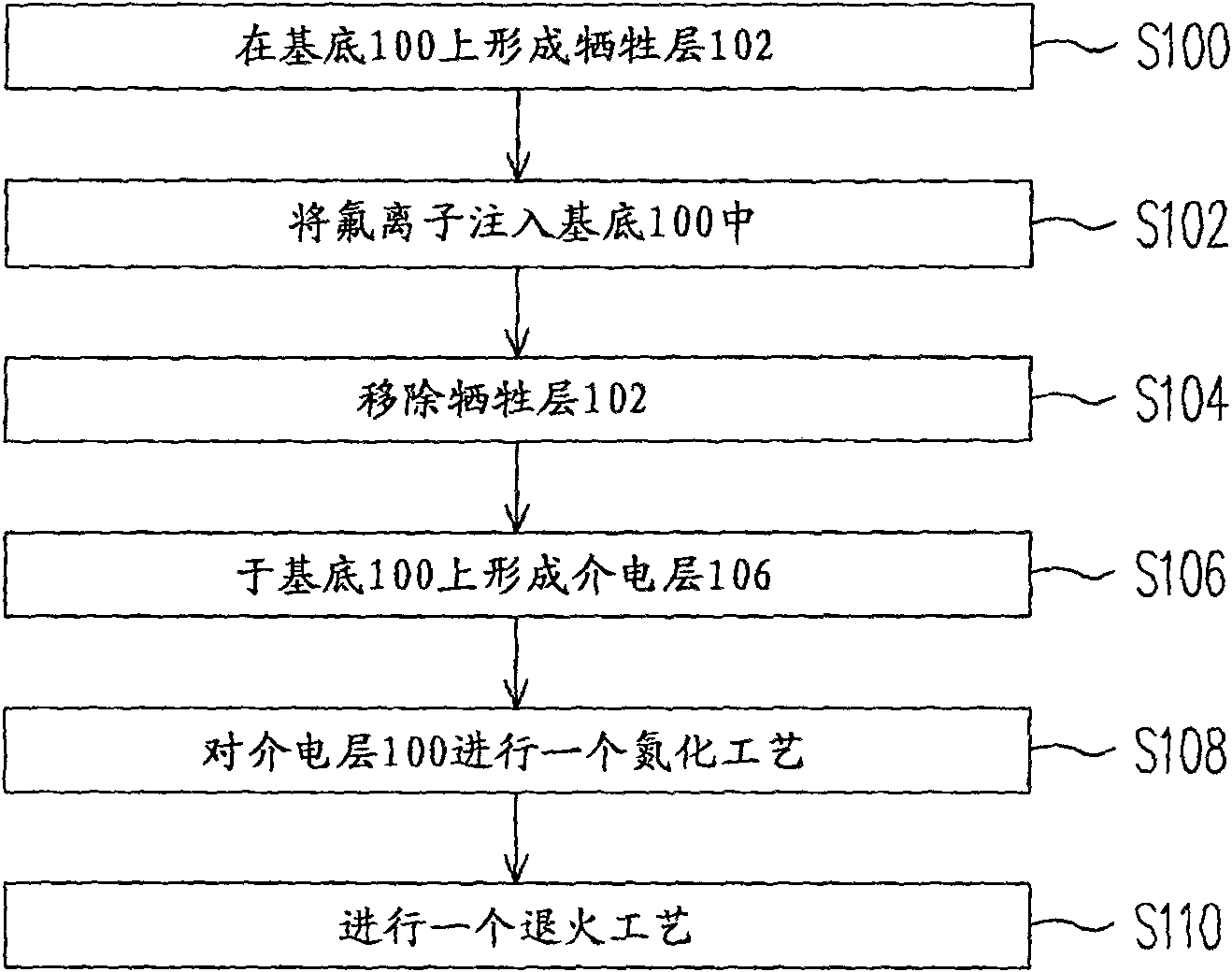

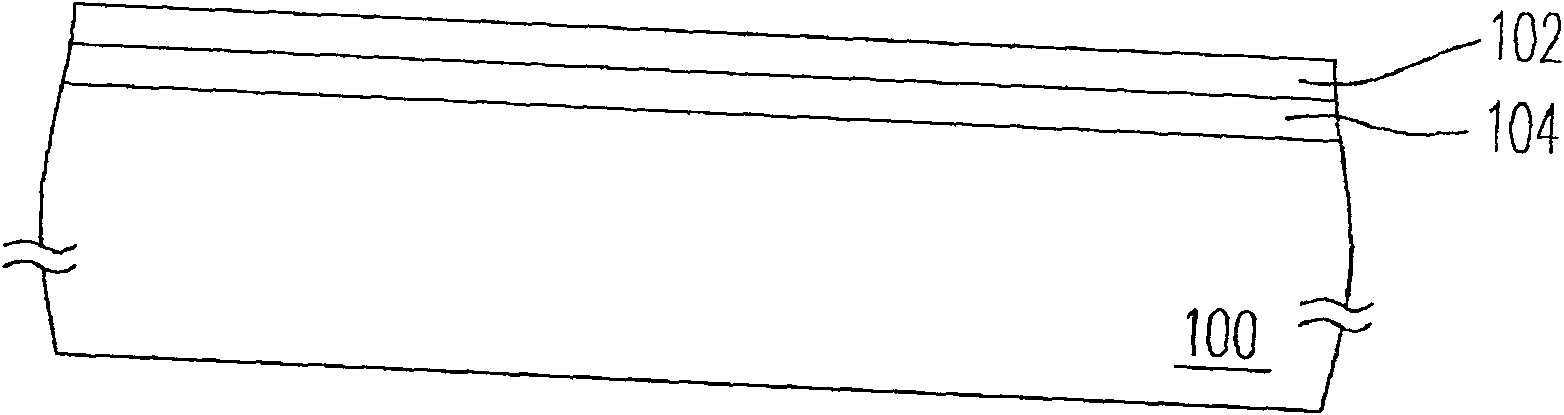

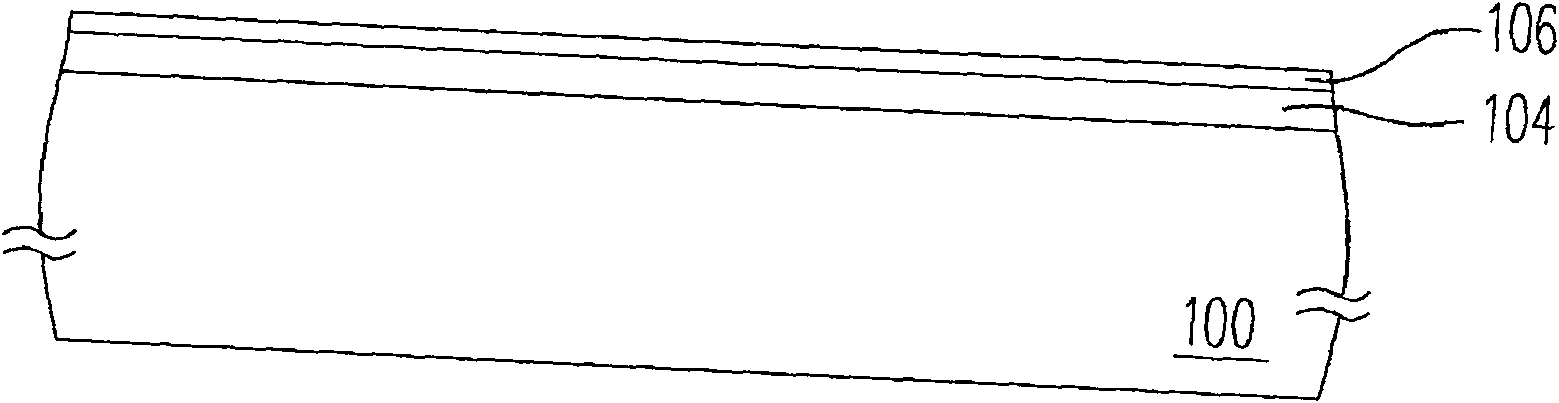

[0043] figure 1 What is shown is a flowchart of a method for manufacturing a gate dielectric layer according to an embodiment of the present invention. Figure 2A to Figure 2B Shown is a cross-sectional view of the manufacturing process of the gate dielectric layer according to an embodiment of the present invention.

[0044] First, please also refer to figure 1 and Figure 2A , proceed to step S100 to form a sacrificial layer 102 on the substrate 100 . The material of the sacrificial layer 102 is, for example, silicon oxide. The method of forming the sacrificial layer 102 is, for example, a thermal oxidation method.

[0045] Next, step S102 is performed to implant fluorine ions into the substrate 100 to form a doped region 104 . A method of implanting fluorine ions into the substrate 100 is, for example, an ion implantation method. Since the substrate 100 is covered with the sacrificial layer 102, the sacrificial layer 102 can prevent the fluorine ions from directly bom...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More