Method for forming device isolation region

A technology for device isolation and peripheral circuit area, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of insulating oxide layer depression, polysilicon residue, active device short circuit, etc., and achieve the effect of improving the depression situation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

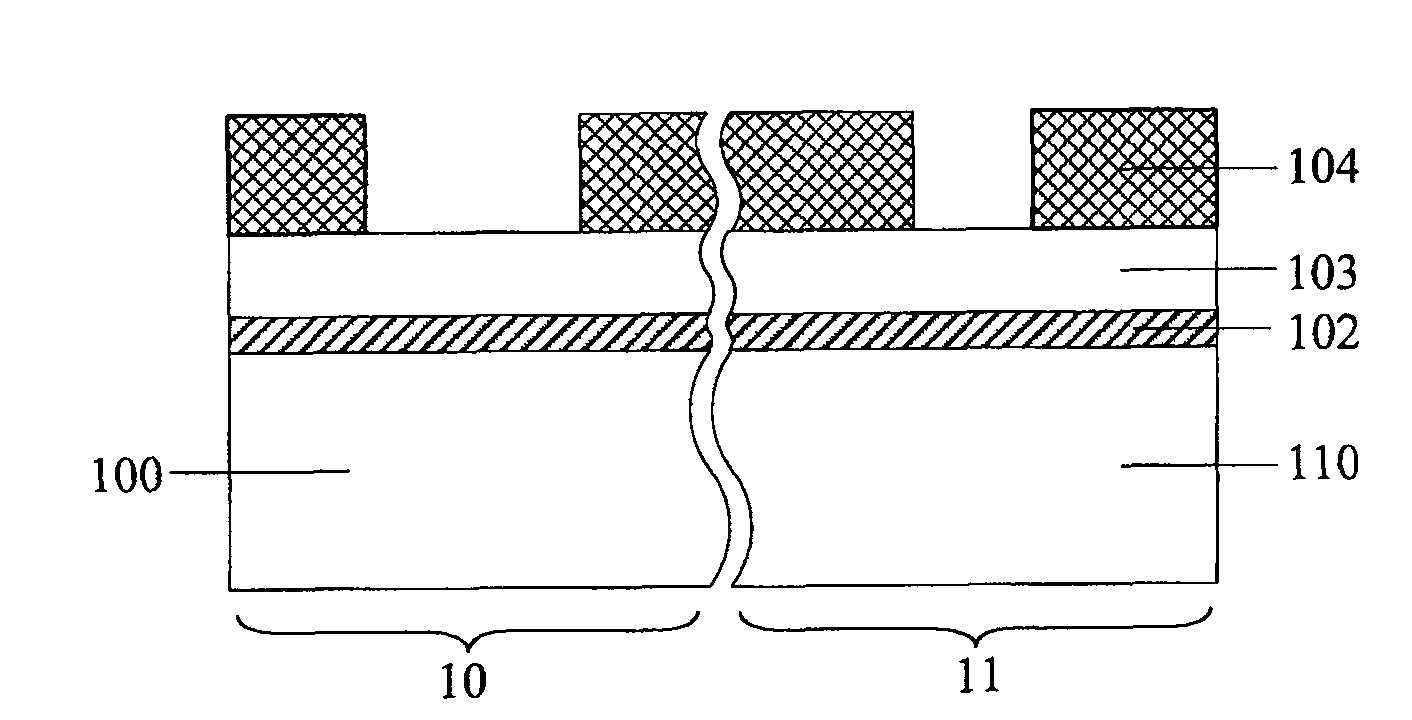

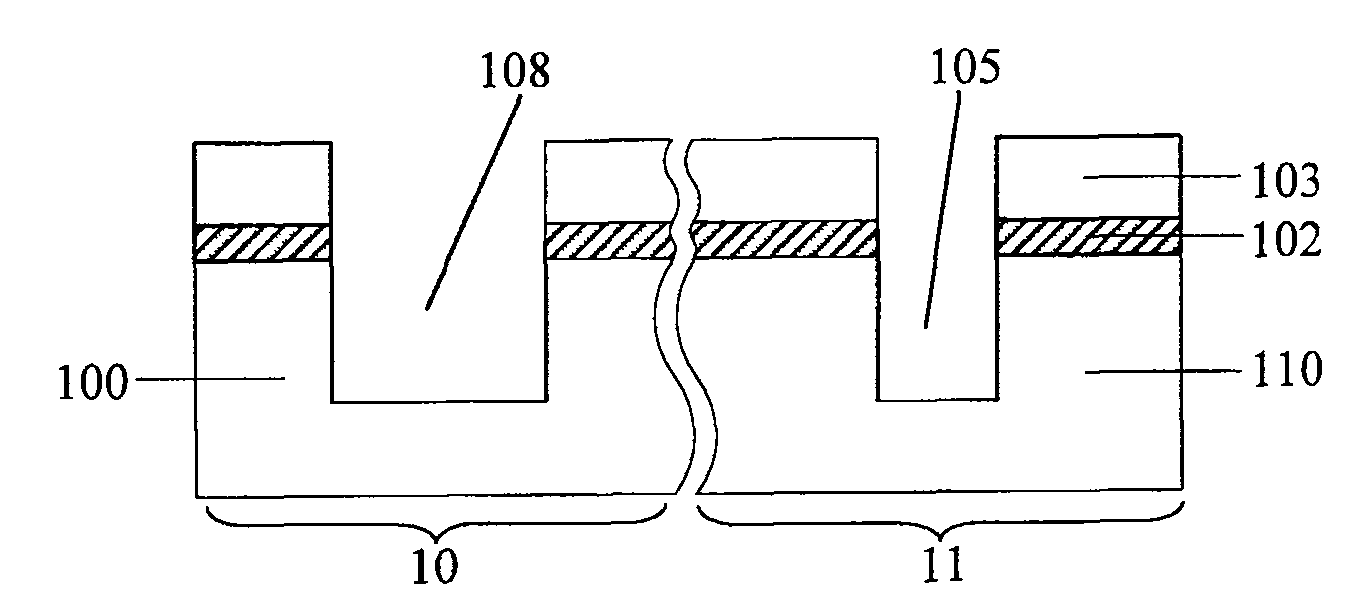

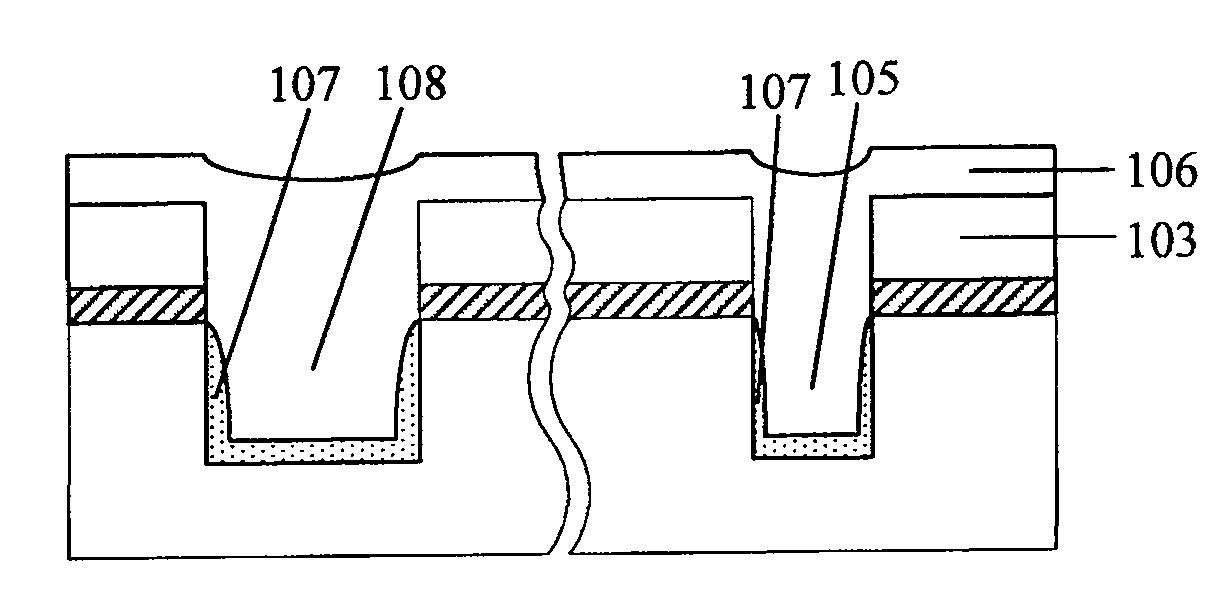

[0021] As the semiconductor technology enters the deep submicron era, the active area isolation of devices below 0.18 μm has mostly been produced by shallow trench isolation technology. Shallow trench isolation technology is an effective method to solve the "bird's beak" problem caused by local oxidation isolation in MOS circuits. However, due to the high aspect ratio of the shallow trenches of deep submicron components, and the high-density plasma chemical vapor deposition (HDP-CVD) method has two functions of "etching" and "deposition", so the process of deposition At the same time, an etching reaction to peel off the deposit will also be carried out, so that the high-density plasma chemical vapor deposition method has good trench filling ability, so it is applied to the insulating oxide layer in the formation of the shallow trench isolation structure.

[0022] Use high-density plasma chemical vapor deposition to fill the shallow trenches in the peripheral circuit area with ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More