Manufacturing design method for integrated circuit

A manufacturable, initial design technology, used in circuits, semiconductor/solid-state device manufacturing, computing, etc., can solve the problem of not providing unfilled pattern target pattern density, reducing pattern density, etc., to reduce feature size unevenness and grinding. The effect of reducing defects, reducing production costs, and shortening trial production time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

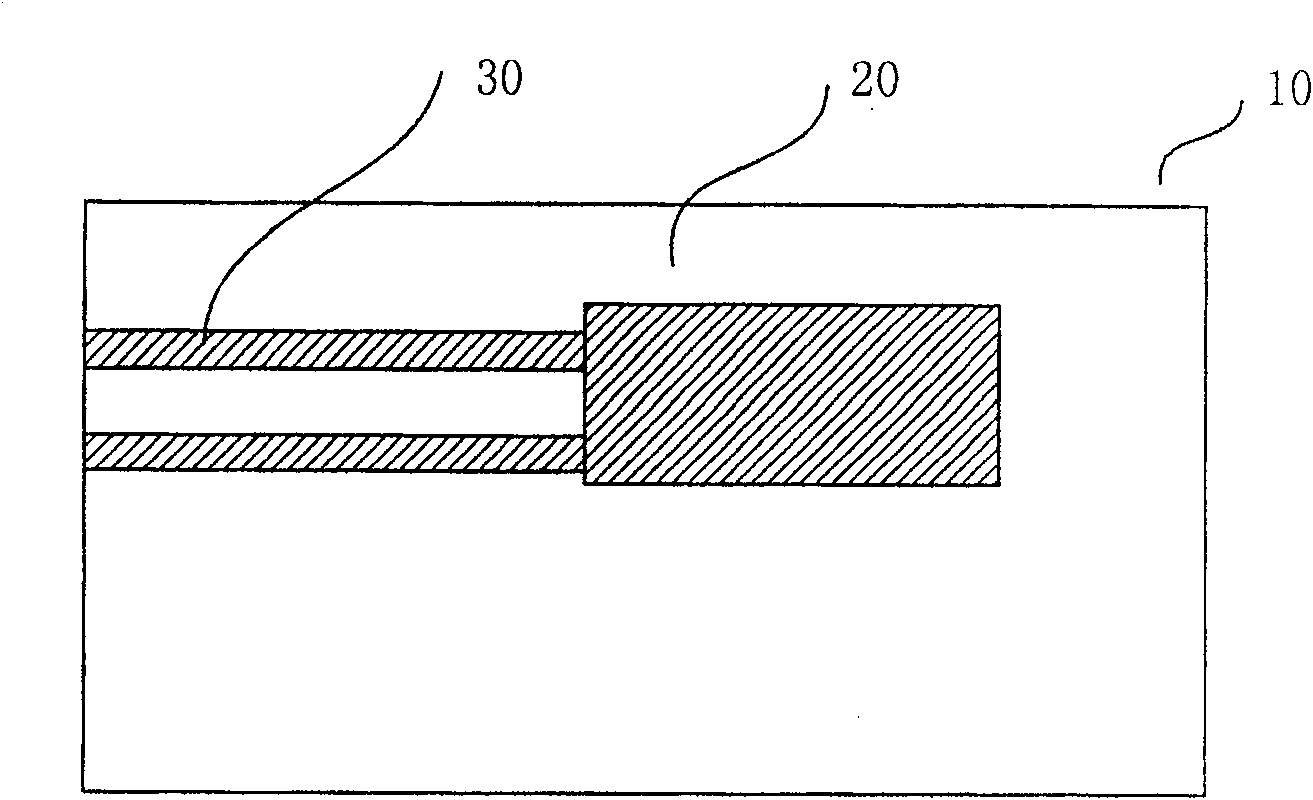

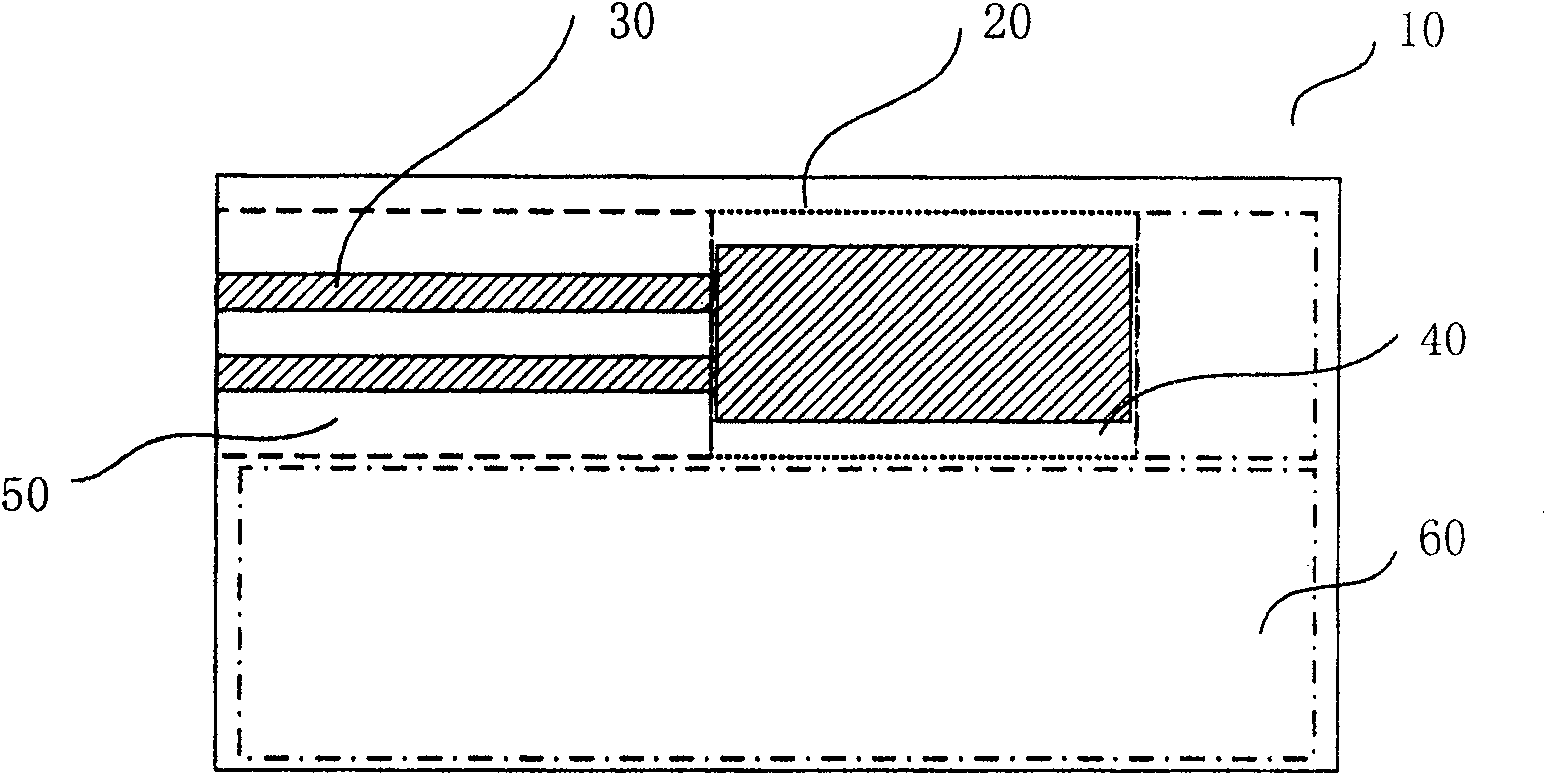

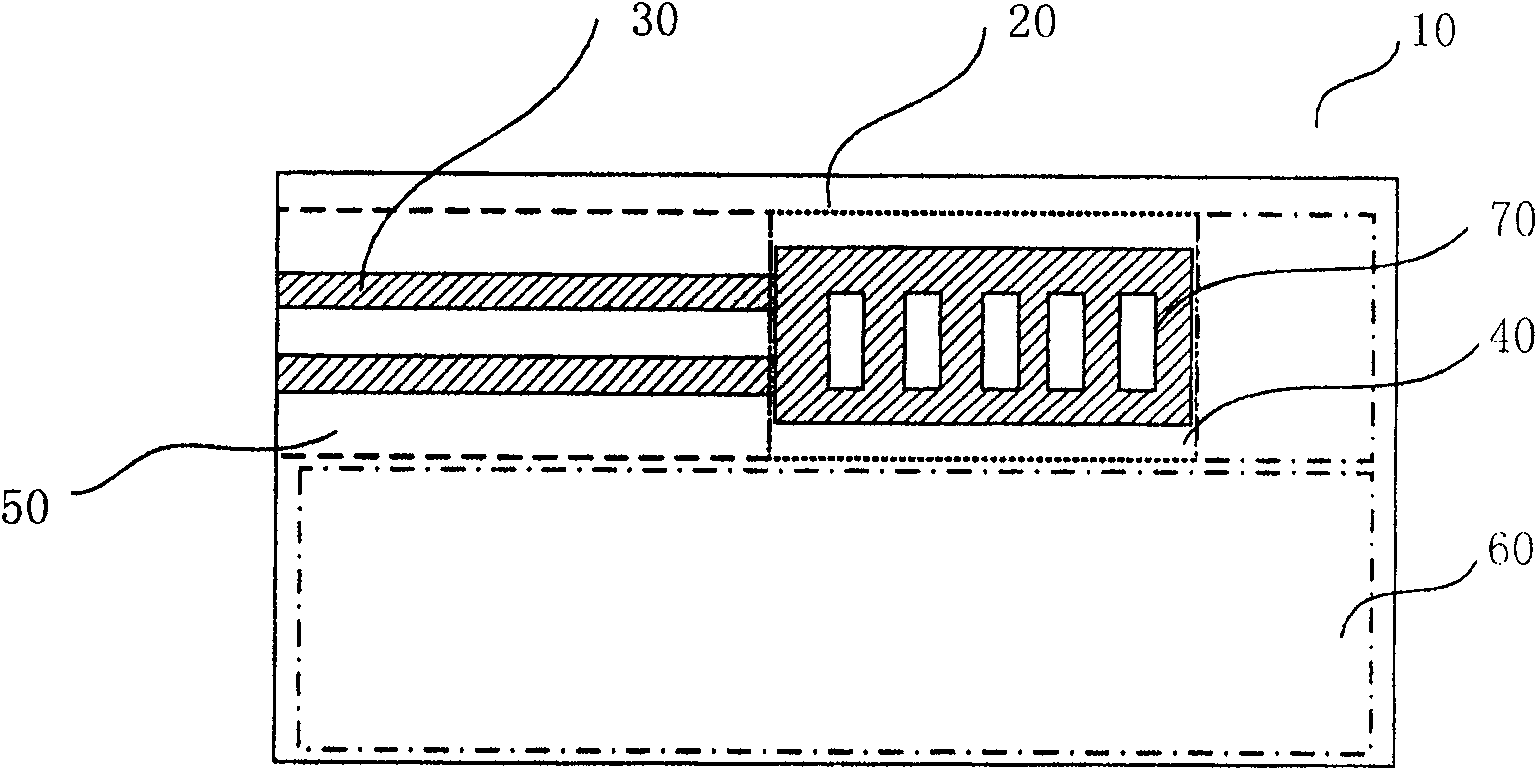

[0069] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0070] The method of the present invention is applicable to the design of any layer in the integrated circuit manufacturing process, including: gate layer, diffusion layer and metal layer, etc. In order to avoid unnecessary incomprehension, well-known circuits, systems and process operations are not described.

[0071] The specific process of adopting the method of the present invention is as follows: firstly, density calculation is performed on the initial design graphics, and the density includes local density and overall density; then, the graphic density is extracted, and then the graphic density is adjusted to the target graphic density, and the target graphic density includes The local target pattern density and the overall target...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More