Flip chip mounting method and flip chip mounting element

A mounting method and flip-chip technology, which are applied in the manufacturing of electric solid-state devices, semiconductor devices, and semiconductor/solid-state devices, etc., can solve the problems of difficult mounting procedures, difficult conduction states, productivity or reliability residues, etc., and achieve high productivity. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

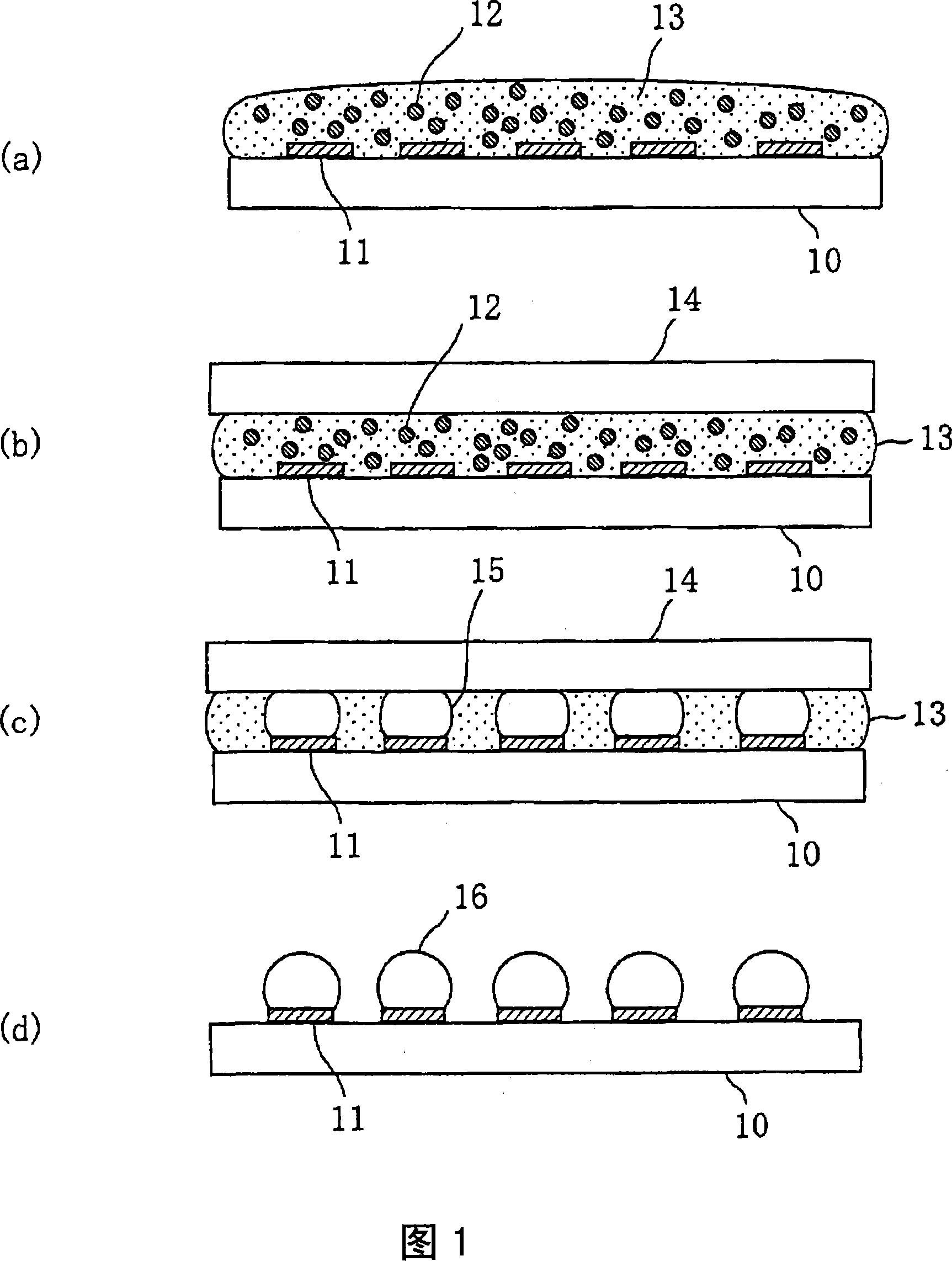

[0067] Referring to FIGS. 1( a ) to ( d ), a method of forming solder bumps according to the other flip chip mounting method will be described. As shown in FIG. 1( a ), a resin 13 containing solder powder (not shown) and a convective additive 12 is supplied on a wiring board 10 on which a plurality of electrodes 11 are formed. Next, as shown in FIG. 1( b ), while bringing the flat plate 14 into contact with the surface of the resin 13 supplied on the wiring board 10 , the wiring board 10 is heated to a temperature at which the solder powder melts. In this heating step, the melted solder powder self-assembles, and as shown in FIG. 1( c ), grown solder balls 15 are selectively formed on a plurality of electrodes 11 . Then, as shown in FIG. 1( d ), when the flat plate 14 is separated from the surface of the resin 13 and the resin 13 is removed, a wiring board 10 in which bumps 16 are formed on a plurality of electrodes 11 is obtained.

[0068] This bump forming method is charact...

Embodiment approach 2

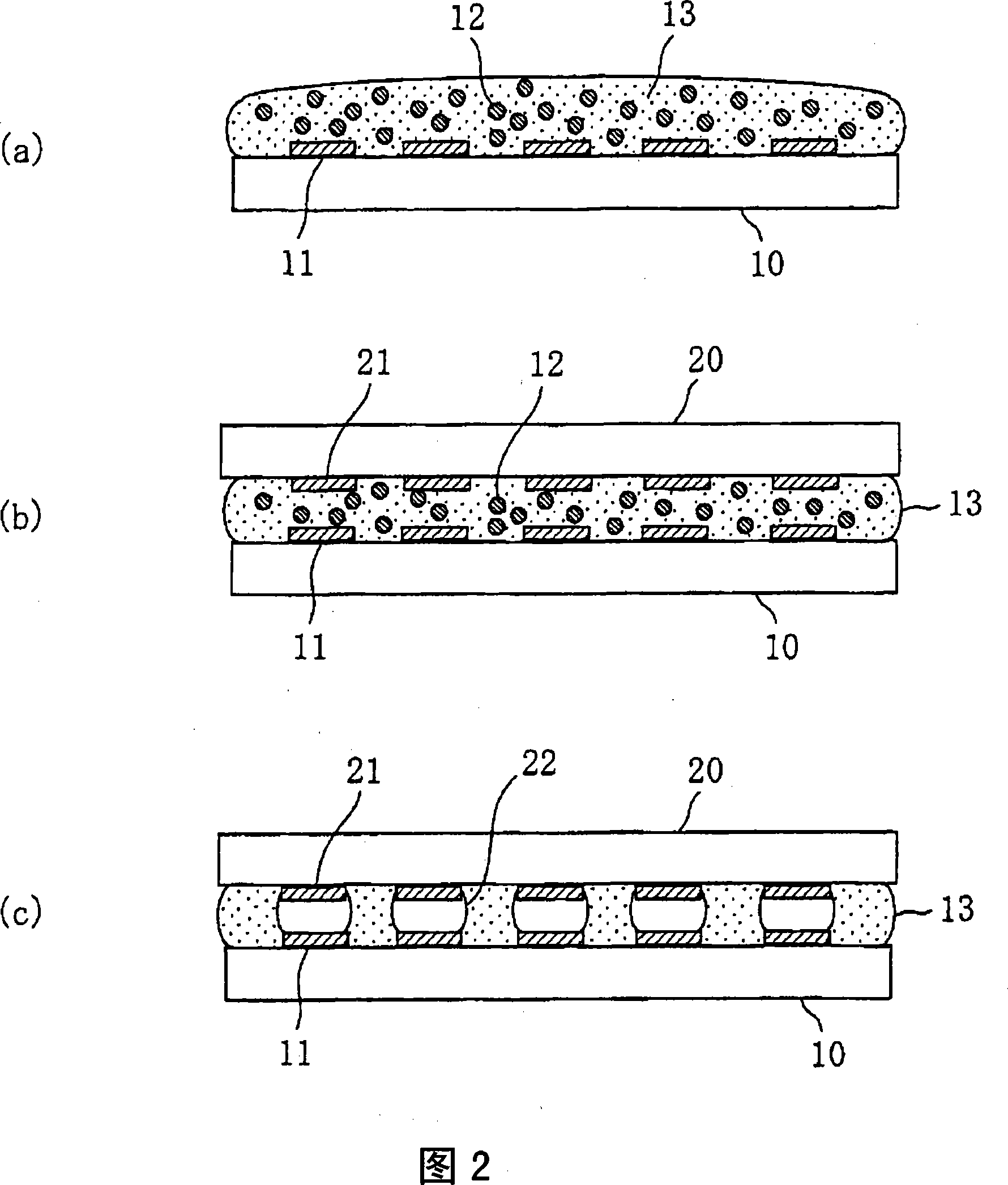

[0093] 2( a ) to ( c ) are diagrams showing basic steps of a flip chip mounting method according to Embodiment 2 of the present invention.

[0094] First, as shown in FIG. 2( a ), a resin 13 containing solder powder (not shown) and a convective additive 12 is supplied on a wiring board 10 having a plurality of electrode terminals 11 . Next, as shown in FIG. 2( b ), the semiconductor chip 20 is brought into contact with the surface of the resin 13 supplied on the wiring board 10 . At this time, the semiconductor chip 20 having a plurality of connection terminals 21 is arranged to face the wiring substrate 10 having a plurality of electrode terminals 11 . Then, in this state, wiring substrate 10 is heated to a temperature at which the solder powder melts or higher. Here, the heating temperature of the wiring board 10 is performed at the boiling point of the convection additive 12 or higher, and the boiling convection additive 12 convects in the resin 13 .

[0095] In this heat...

Embodiment approach 3

[0137] Hereinafter, Embodiment 3, which is various modifications of Embodiment 2, will be described with reference to the drawings.

[0138] Fig. 6 (a), (b) is a diagram showing the structure when a plurality of semiconductor chips (20a, 20b, 20c, 20d) are mounted on the wiring substrate 10, Fig. 6 (a) shows its top view, Fig. 6 (b) shows a cross-sectional view along line BB' of FIG. 6(a).

[0139] Flip-chip mounting of a plurality of semiconductor chips (20a, 20b, 20c, 20d) on the wiring board 10 is performed by the following method.

[0140] First, a resin containing solder powder and a convective additive is preliminarily applied to regions on the wiring board 10 where the respective semiconductor chips (20a, 20b, 20c, 20d) are mounted. Then, each semiconductor chip is brought into contact with the resin surface so that the connection terminals of the respective semiconductor chips face the respective electrode terminals on the wiring substrate 10 . Then, the wiring board...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More