Chip overlap structure and wafer structure for manufacturing the chip stack structure

A chip stacking and chip technology, which is applied to electrical components, electrical solid-state devices, circuits, etc., can solve the problem of increasing the thickness of the chip package stack structure 100 and the difficulty of further improving and reducing the package accumulation of the chip package stack structure 100. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

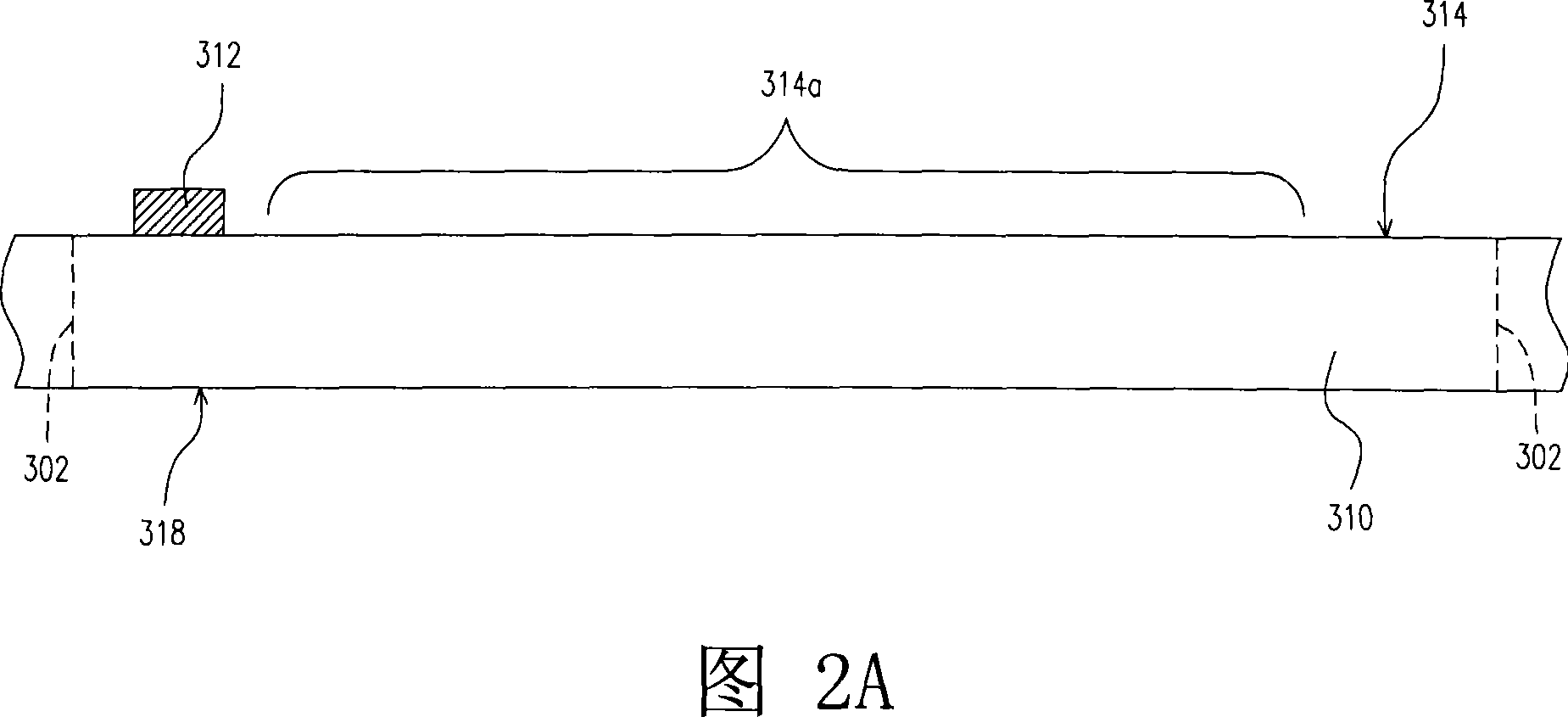

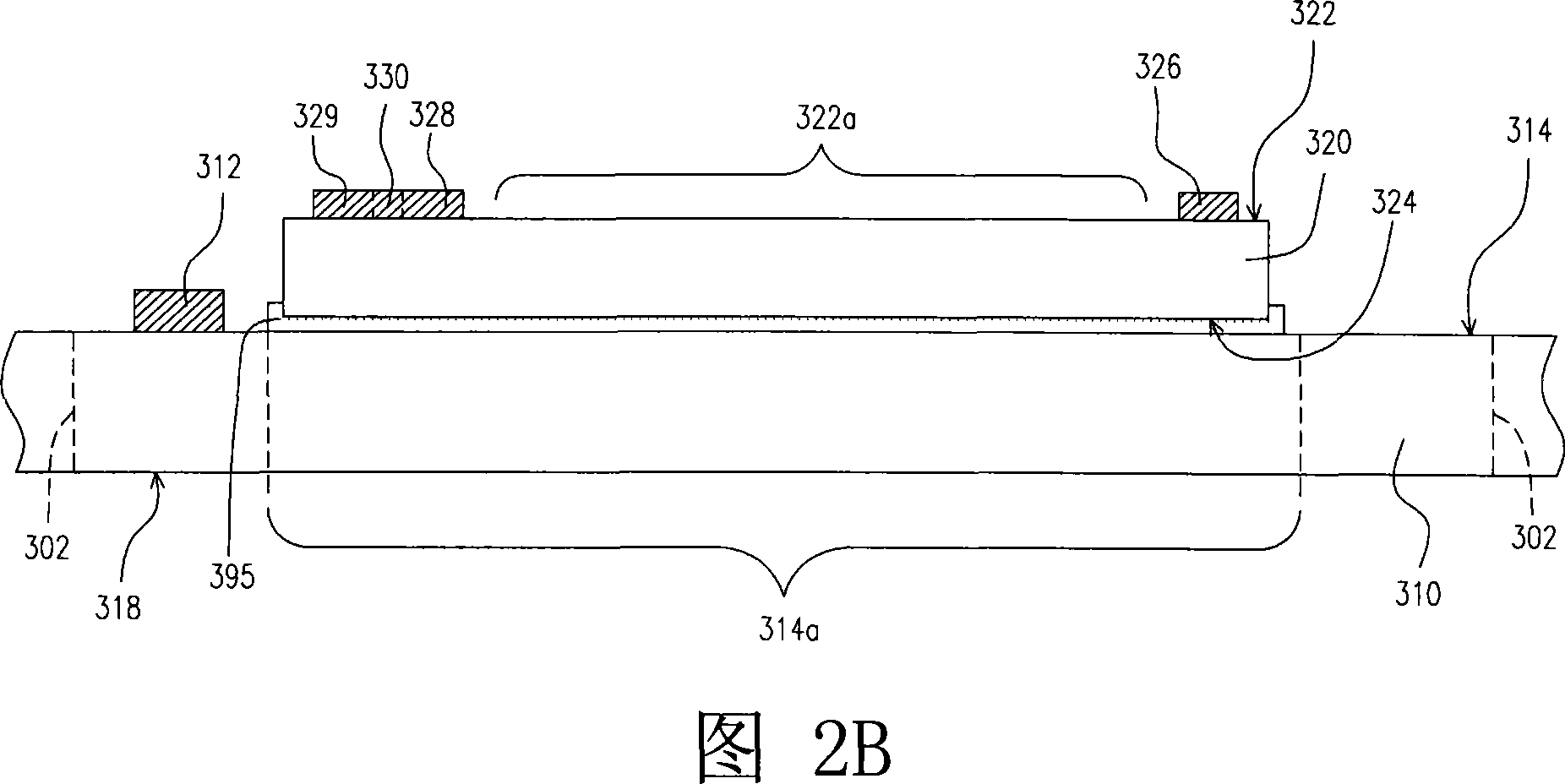

[0033] 2A-2F are schematic cross-sectional views of the fabrication process of the wafer structure according to an embodiment of the present invention. FIG. 3 is a schematic top view of FIG. 2A . Please refer to FIG. 2A and FIG. 3 together. First, a semiconductor substrate 300 is provided, which includes at least one first chip 310 . The junction 302 of two adjacent first chips 310 is marked by a straight line in FIG. 3 , and is marked by a dotted line in FIG. 2A . One or more second contacts 312 are disposed on the active surface 314 of the first chip 310, and the active surface 314 has a chip carrying area 314a, and the second contacts 312 are located outside the chip carrying area 314a.

[0034]Referring to FIG. 2B , a second chip 320 is then provided, wherein the second chip 320 has an active surface 322 and a back surface 324 . Then, the back surface 324 faces the active surface 314 of the first chip 310, and the second chip 320 is disposed in the chip carrying area 314...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More