Semiconductor element and its manufacturing method

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as limited stress in the channel region, and achieve the goals of increasing stress, low power consumption, and suppressing short-channel effects Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

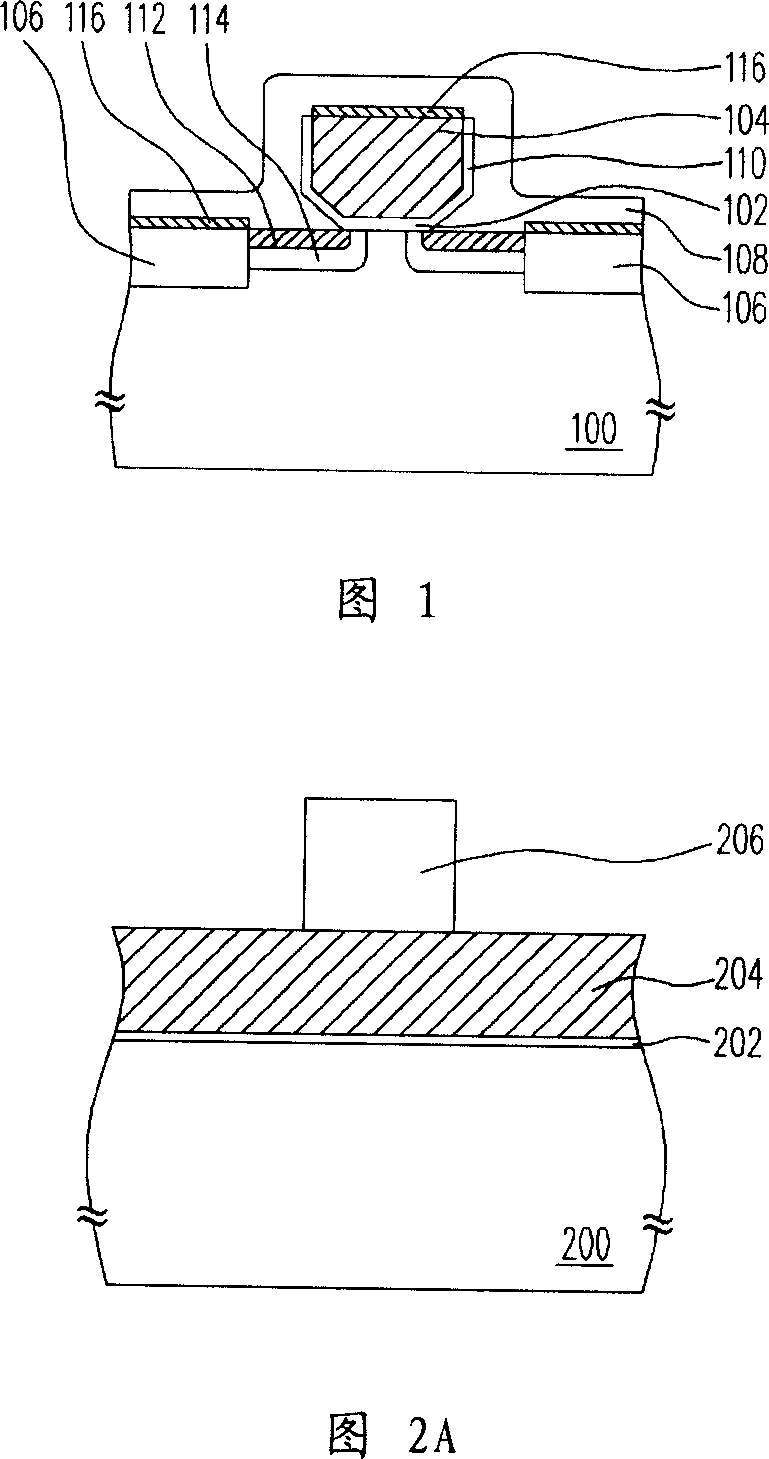

[0047] FIG. 1 is a cross-sectional view of a semiconductor device according to an embodiment of the invention. First, please refer to FIG. 1, the semiconductor element is, for example, an NMOS transistor, including a semiconductor substrate 100, a gate dielectric layer 102, a gate 104, a source / drain region 106, a stress layer 108, a An oxide layer 110 , a lightly doped region 112 , a ring implant region 114 and a metal silicide 116 are lined.

[0048] Wherein, the semiconductor substrate 100 is, for example, a silicon substrate or a substrate with silicon on an insulating layer, and the gate dielectric layer 102 is disposed on the semiconductor substrate 100, and its material is, for example, silicon oxide.

[0049] The gate 104 is disposed on the gate dielectric layer 102, and its material is, for example, doped polysilicon, and the top area of the gate 104 is larger than the bottom area. In this way, since the contact area between the gate 104 and the gate dielectric lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More