Patents

Literature

125results about How to "High speed operation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

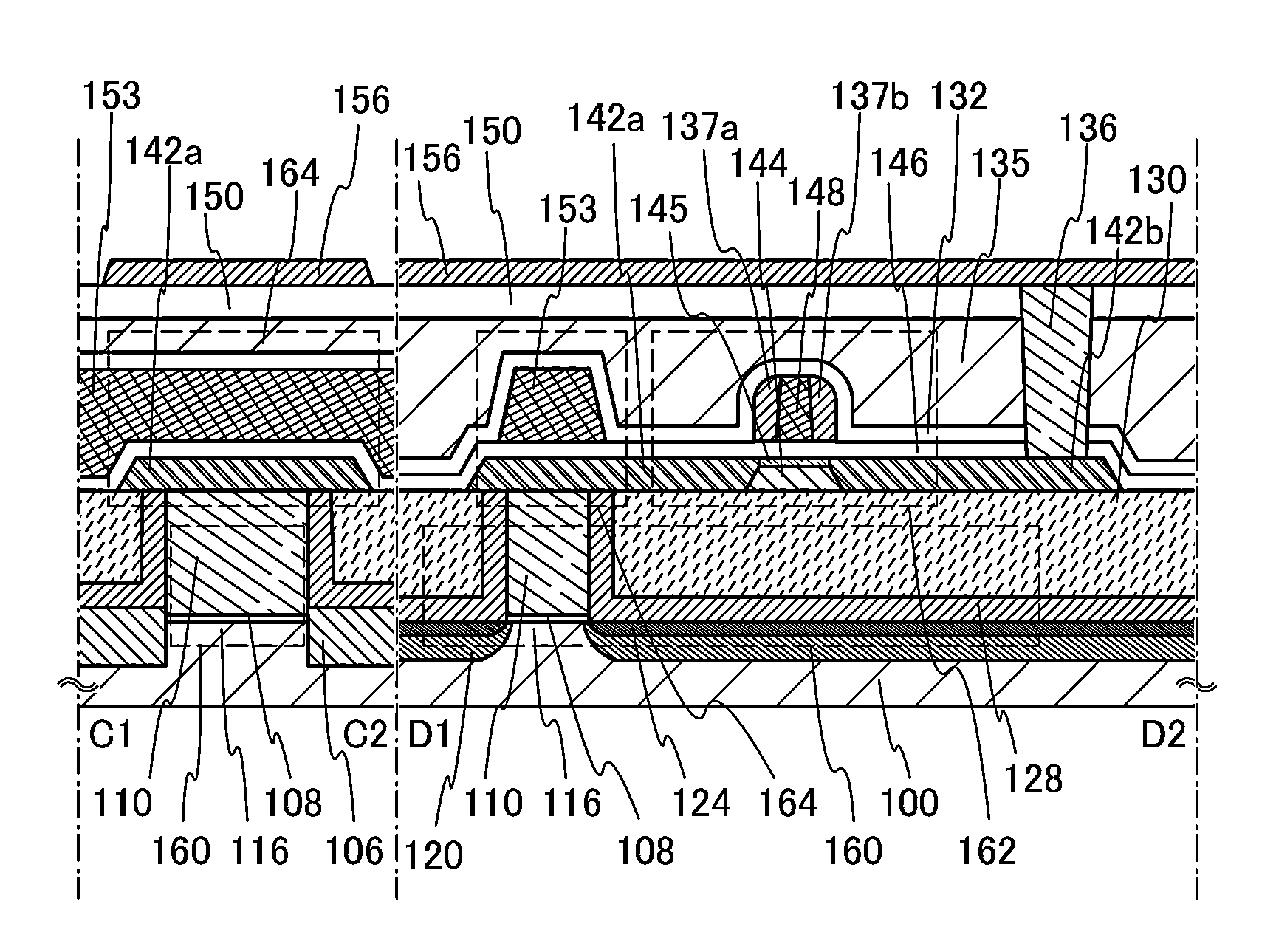

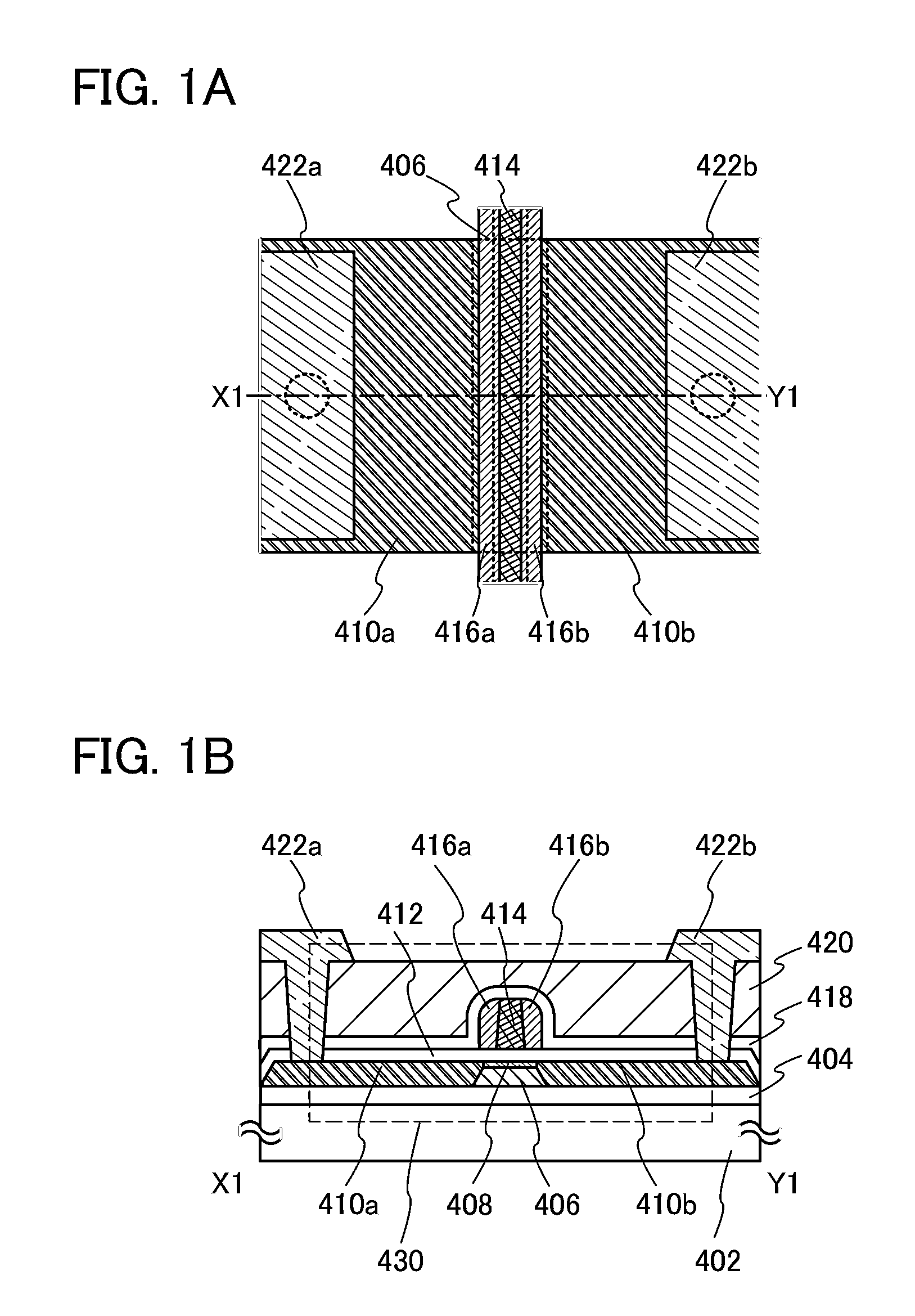

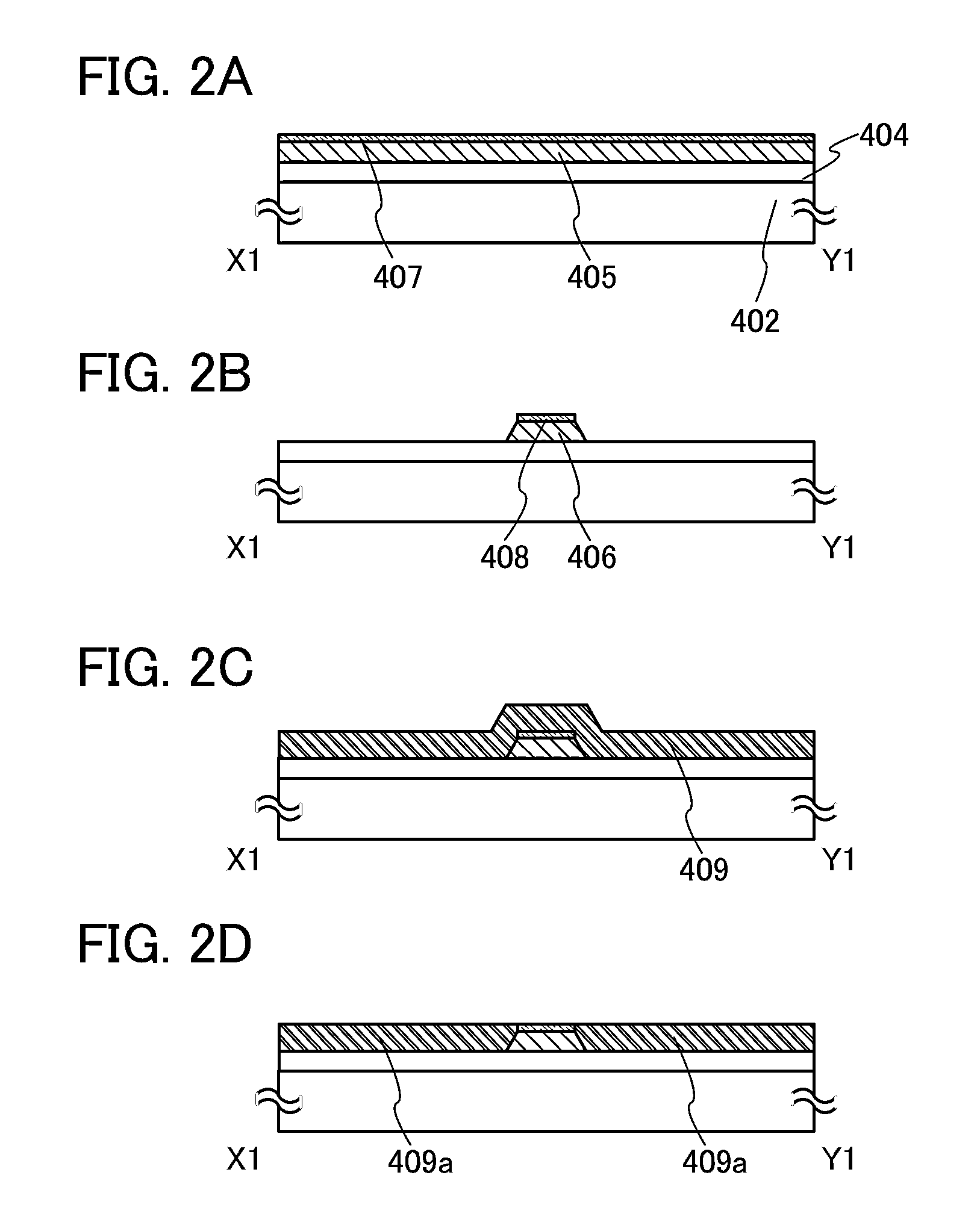

Semiconductor device and method for manufacturing semiconductor device

ActiveUS20140001468A1Improve featuresStable characteristicsTransistorSemiconductor/solid-state device manufacturingSemiconductorLow resistance

In a top-gate transistor in which an oxide semiconductor film, a gate insulating film, a gate electrode layer, and a silicon nitride film are stacked in this order and the oxide semiconductor film includes a channel formation region, nitrogen is added to regions of part of the oxide semiconductor film and the regions become low-resistance regions by forming a silicon nitride film over and in contact with the oxide semiconductor film. A source and drain electrode layers are in contact with the low-resistance regions. A region of the oxide semiconductor film, which does not contact the silicon nitride film (that is, a region overlapping with the gate insulating film and the gate electrode layer) becomes the channel formation region.

Owner:SEMICON ENERGY LAB CO LTD

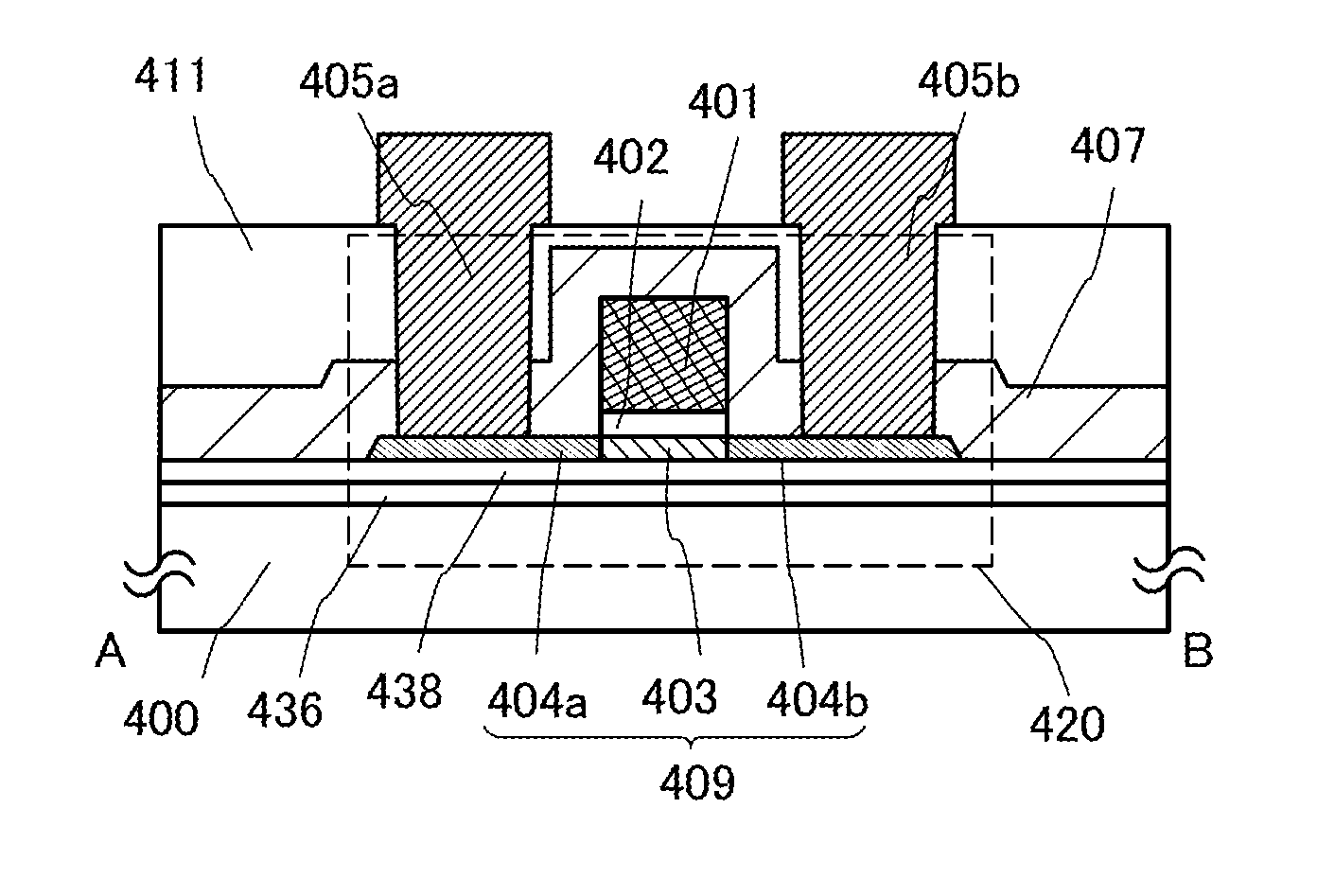

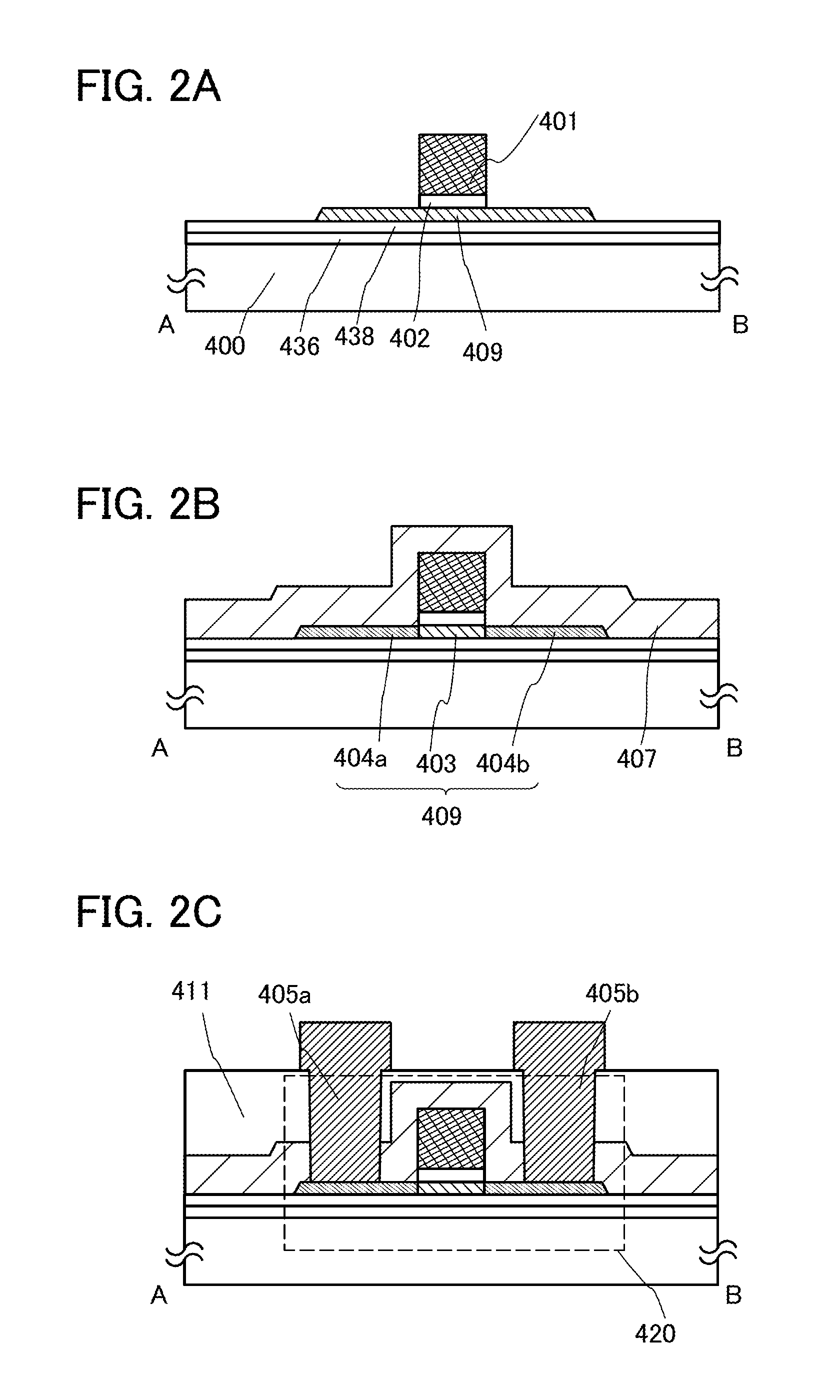

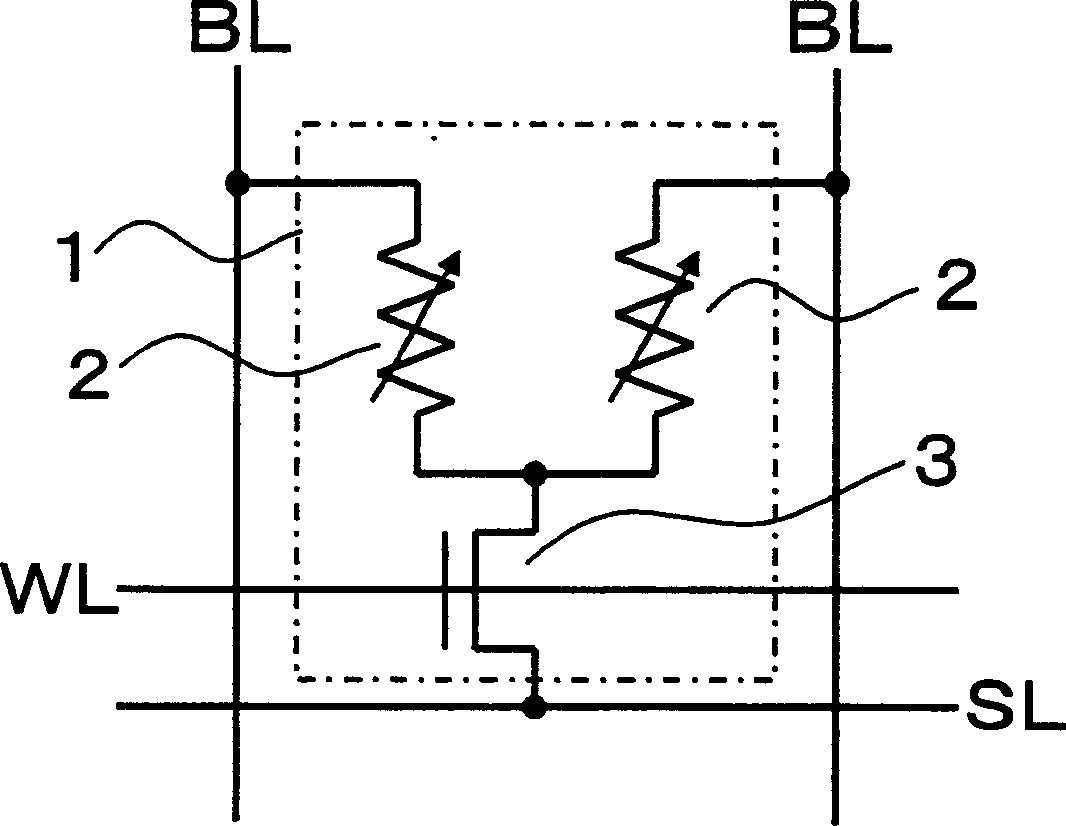

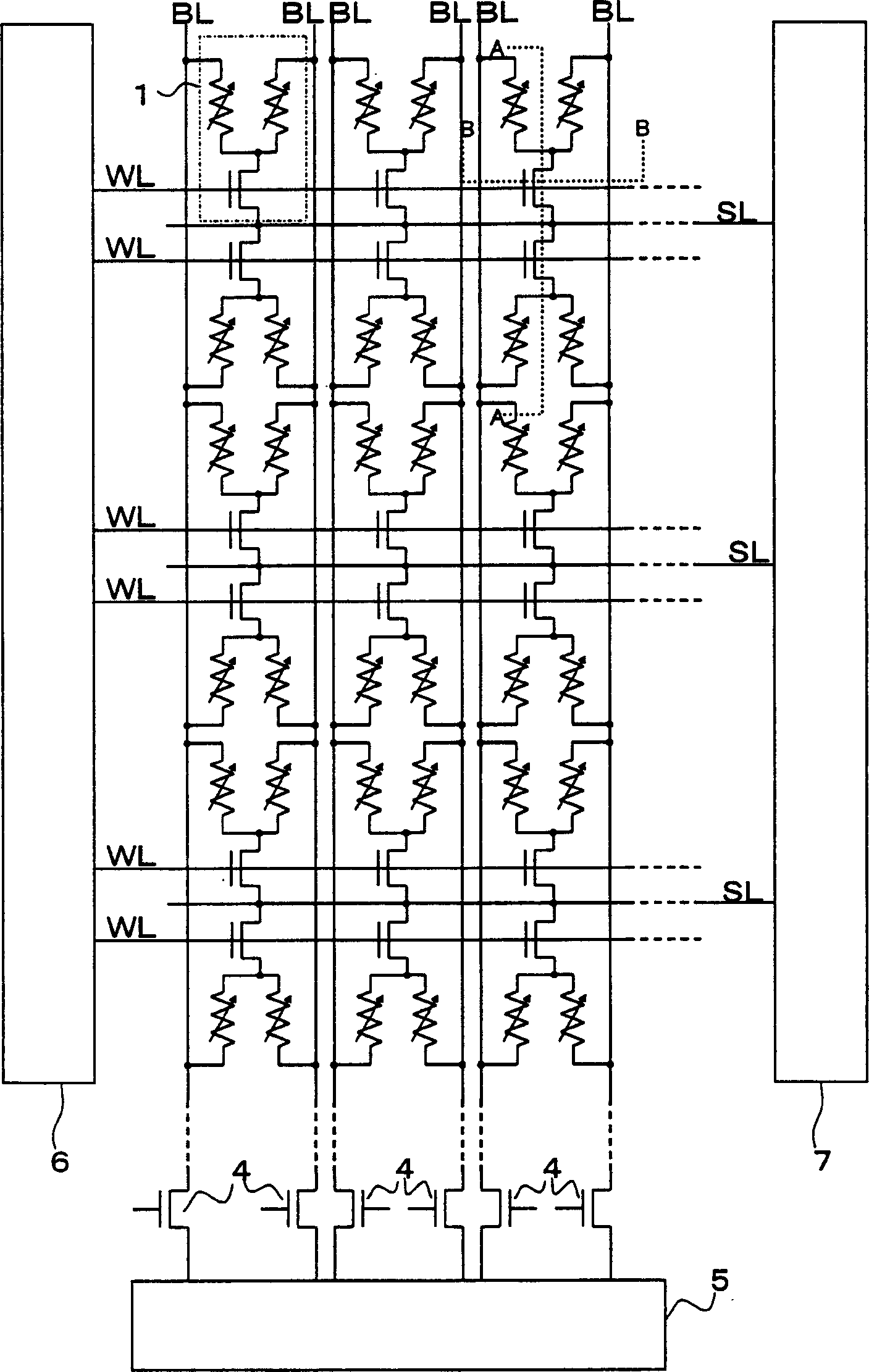

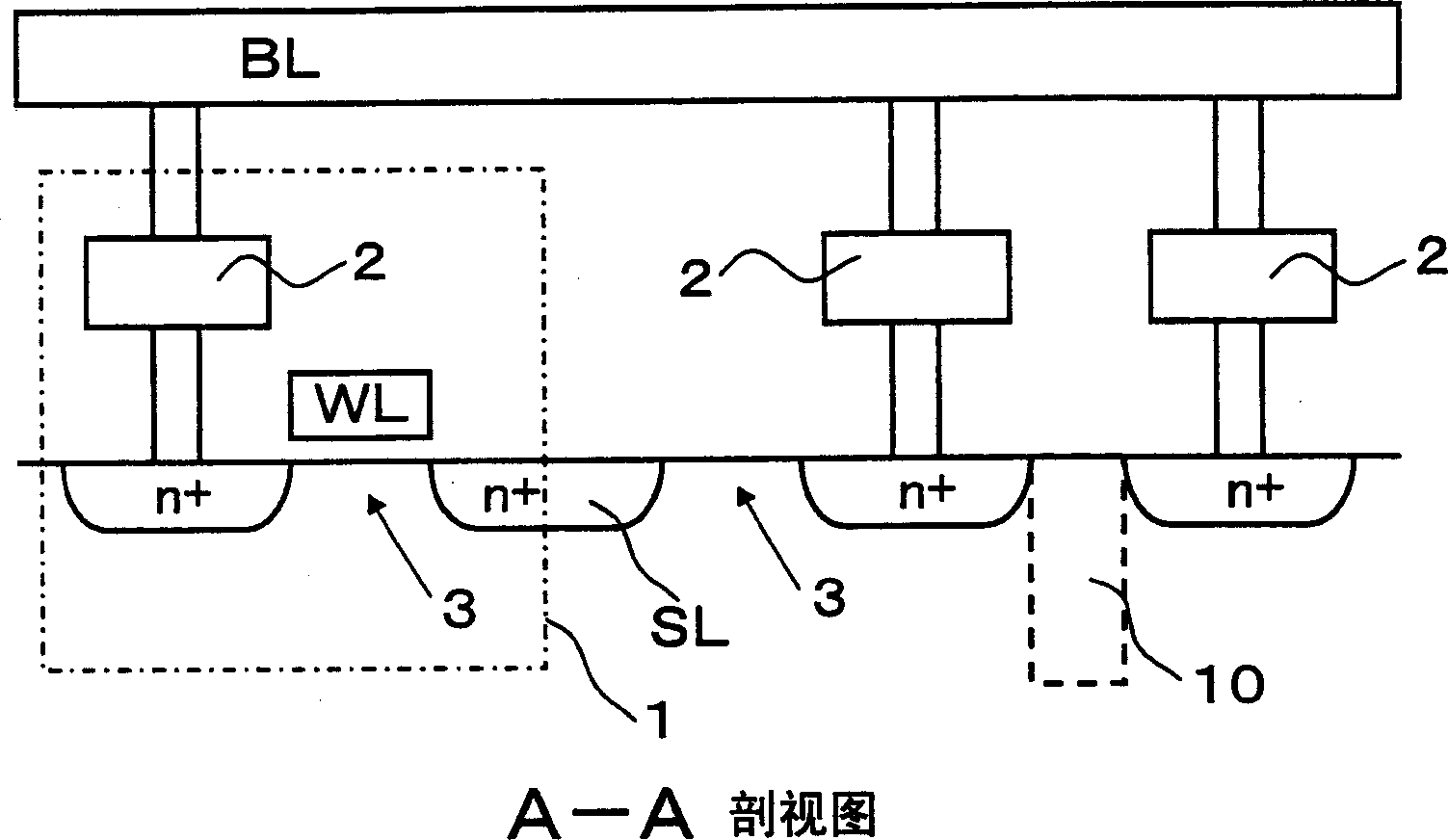

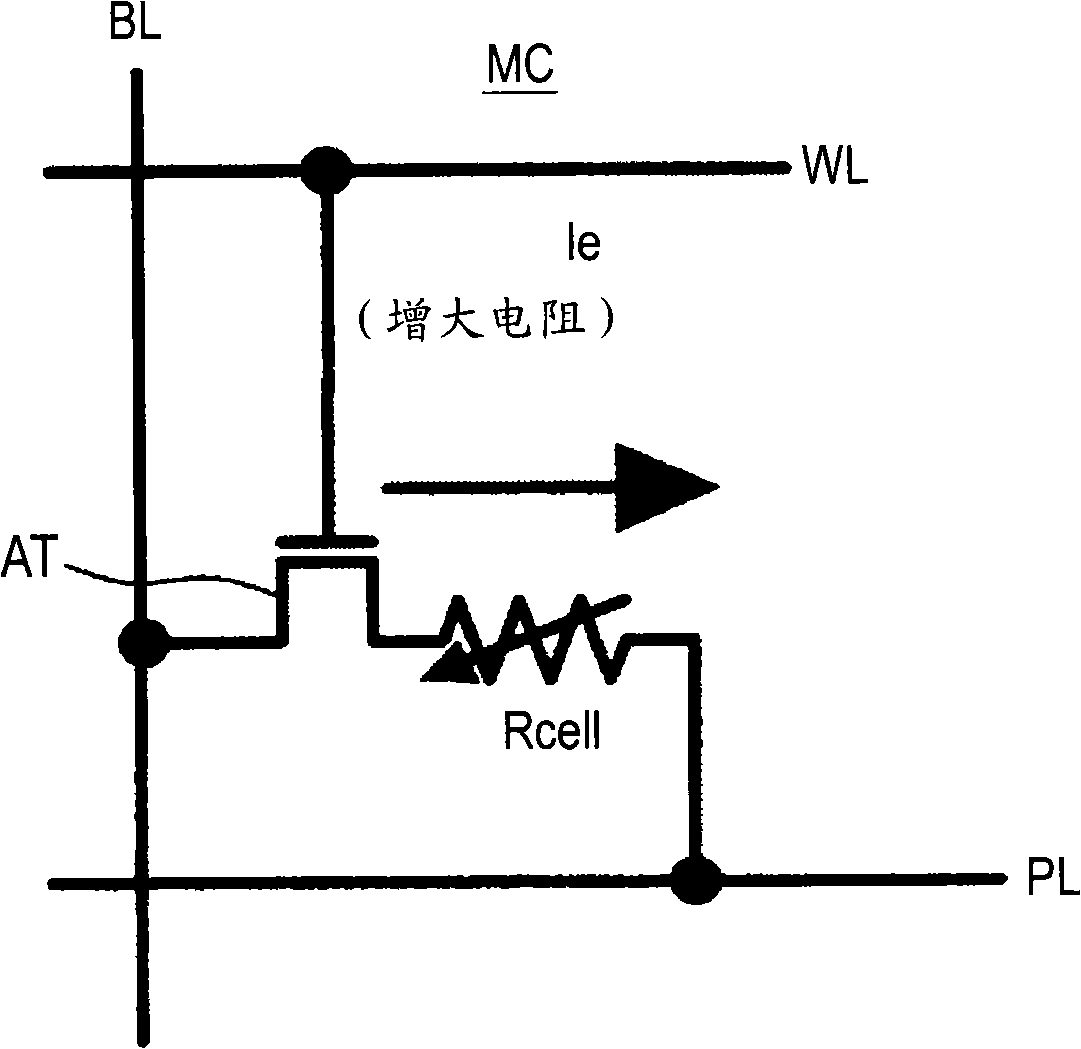

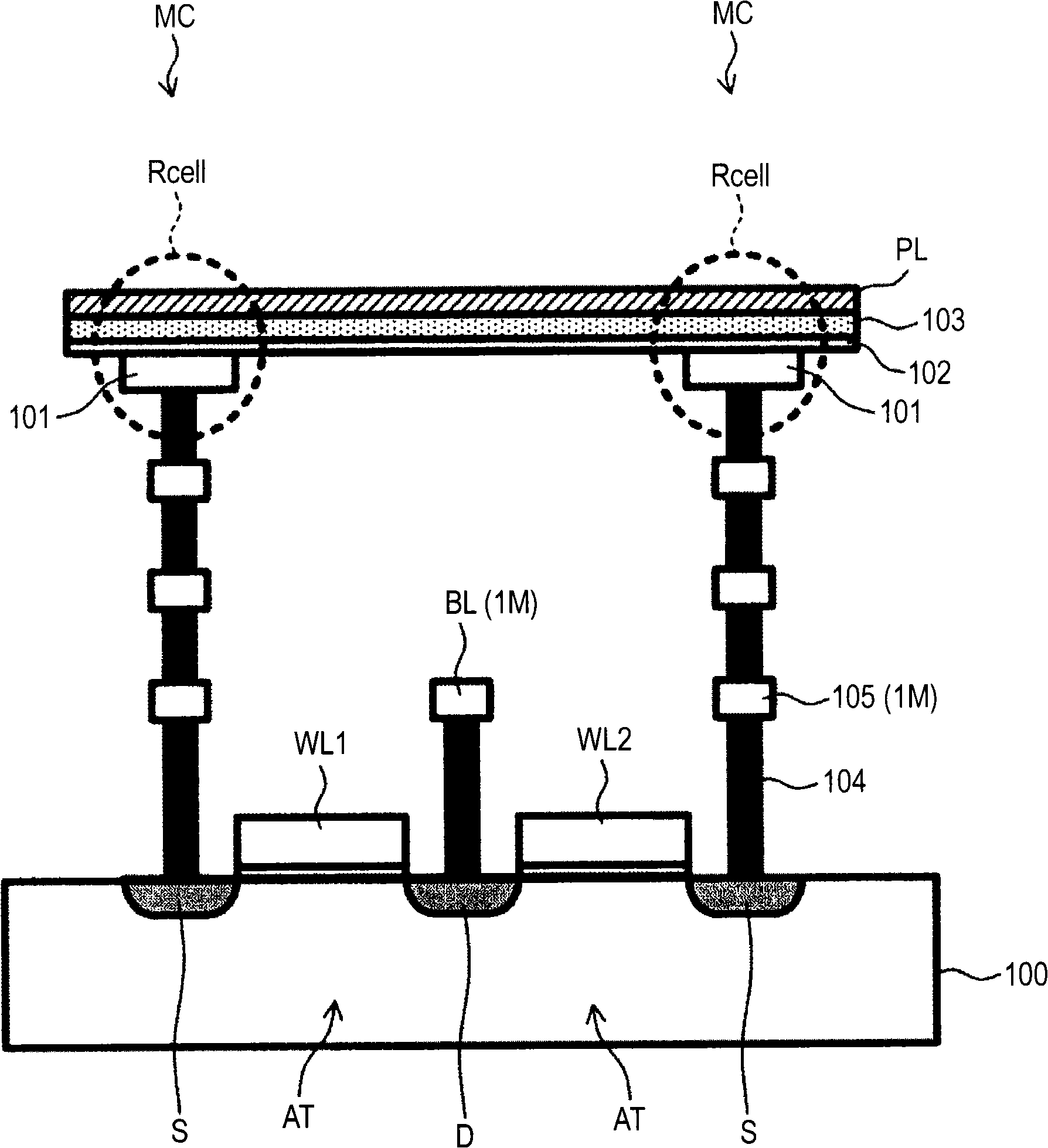

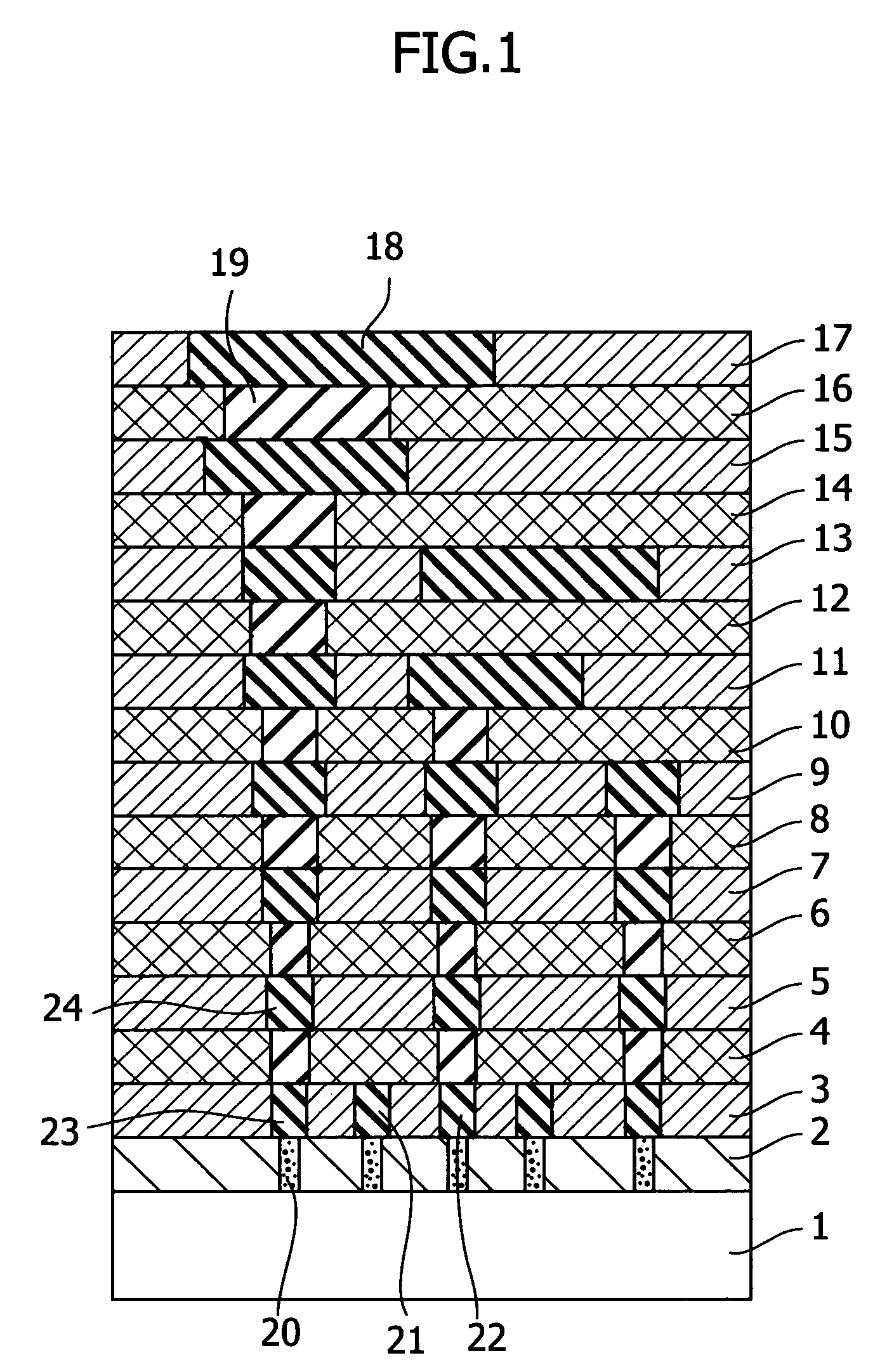

Nonvolatile memory cell and non-volatile semiconductor memory device

ActiveCN1505043ALower on-state resistanceRead operation speed upMagnetic-field-controlled resistorsSolid-state devicesMOSFETElectrical resistance and conductance

It is an object of the present invention to make it possible to decrease the on-state resistance of a selection transistor of a memory cell without increasing the whole area of a memory cell array and accelerate and stabilize the reading operation of data stored in the memory cell. Therefore, a plurality of variable resistive elements capable of storing information in accordance with a change of electrical resistances is included, one ends of the variable resistive elements are connected each other, and an electrode of a selection element constituted by a MOSFET or diode element for selecting the variable resistive elements in common is connected with one end of each of the variable resistive elements to constitute a memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

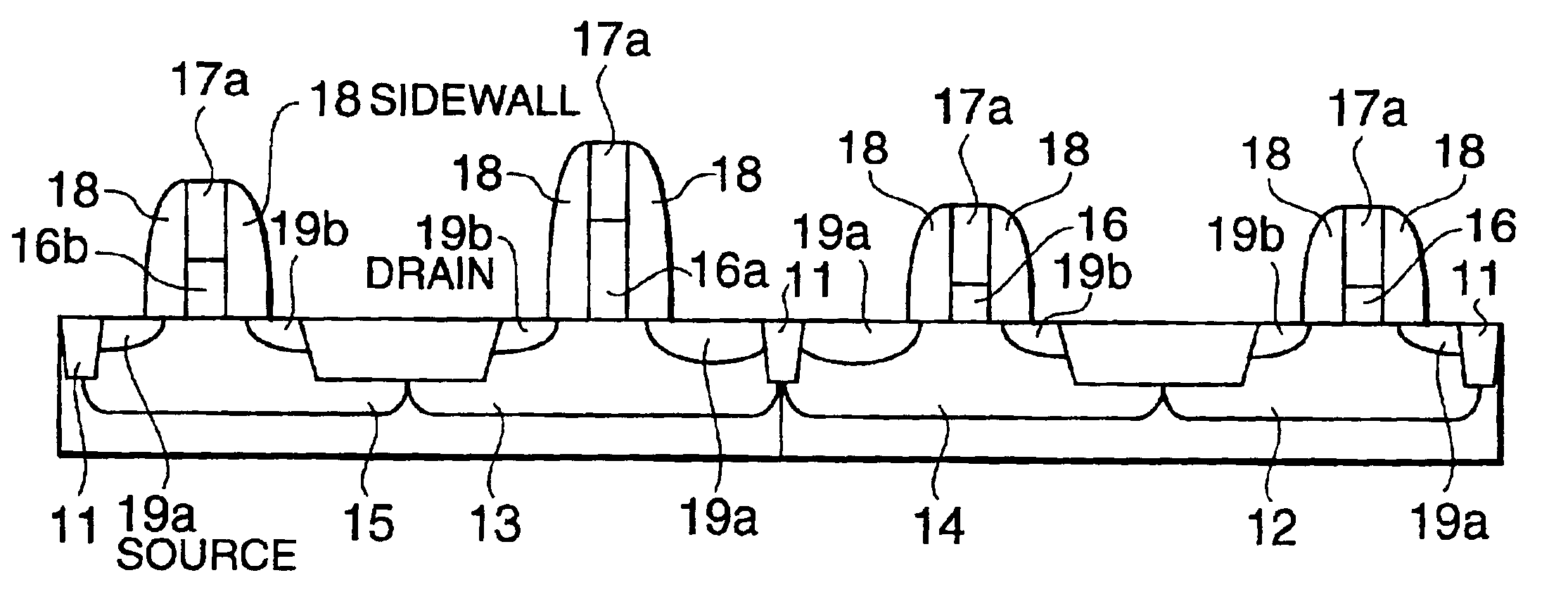

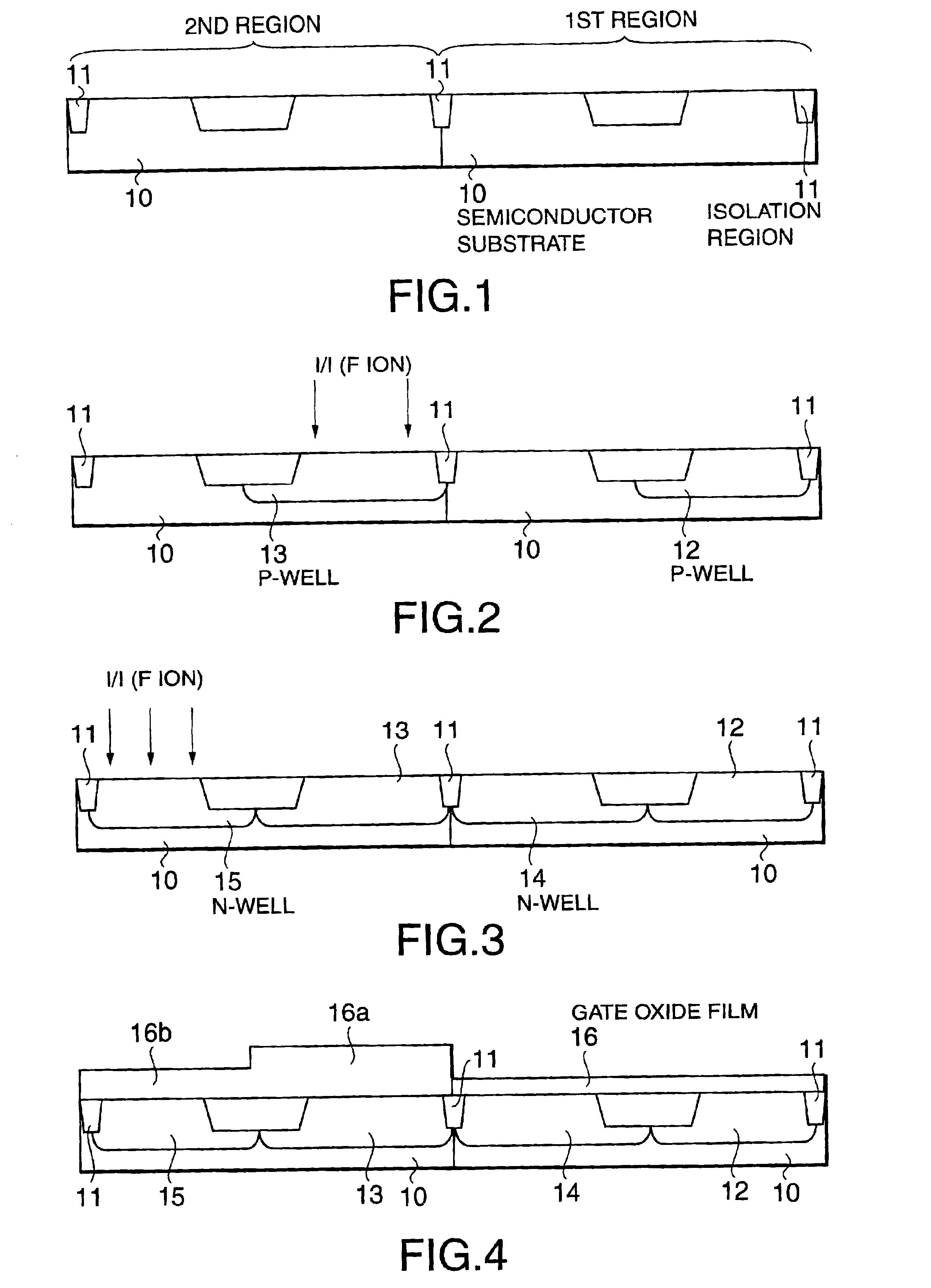

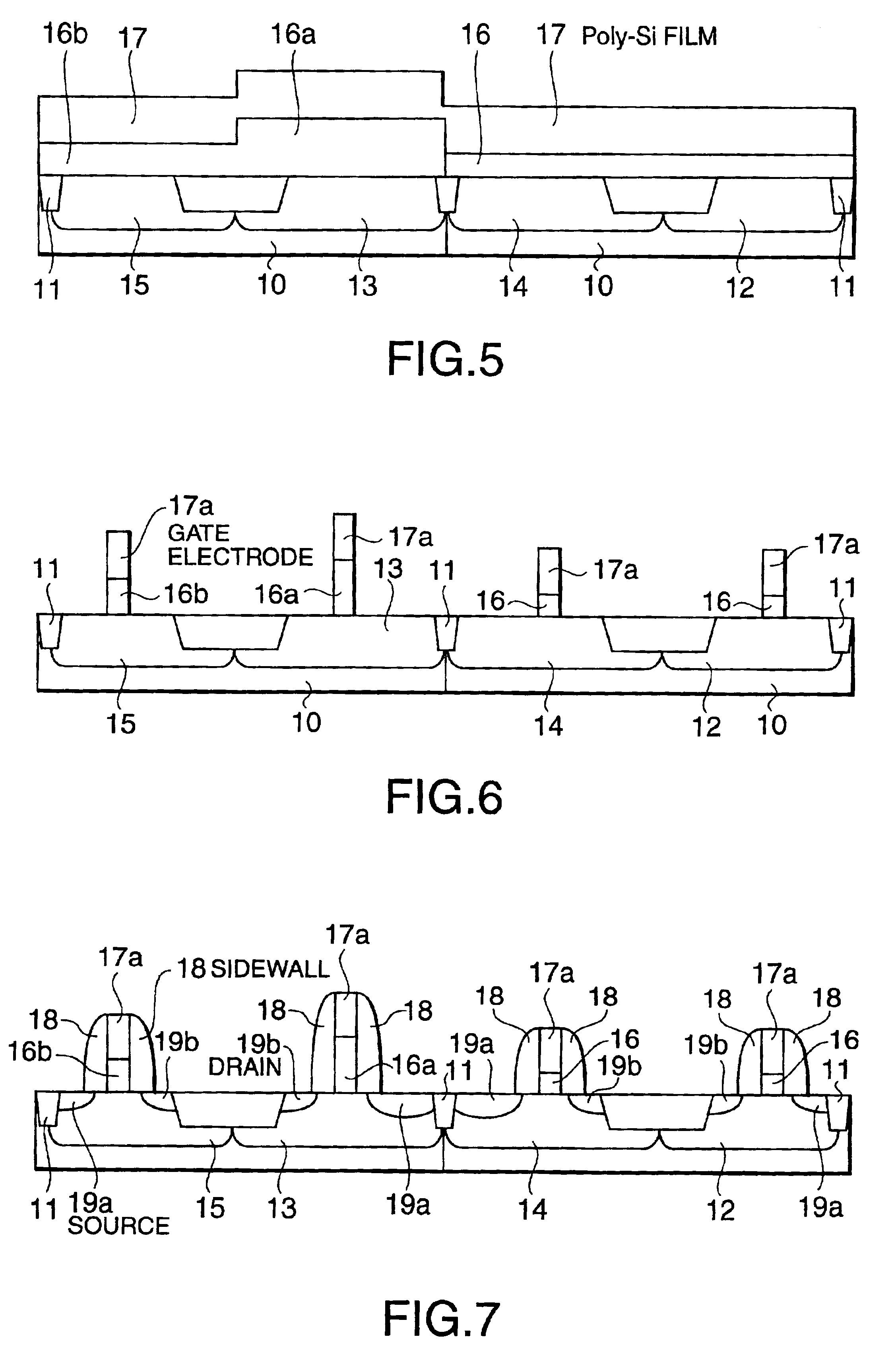

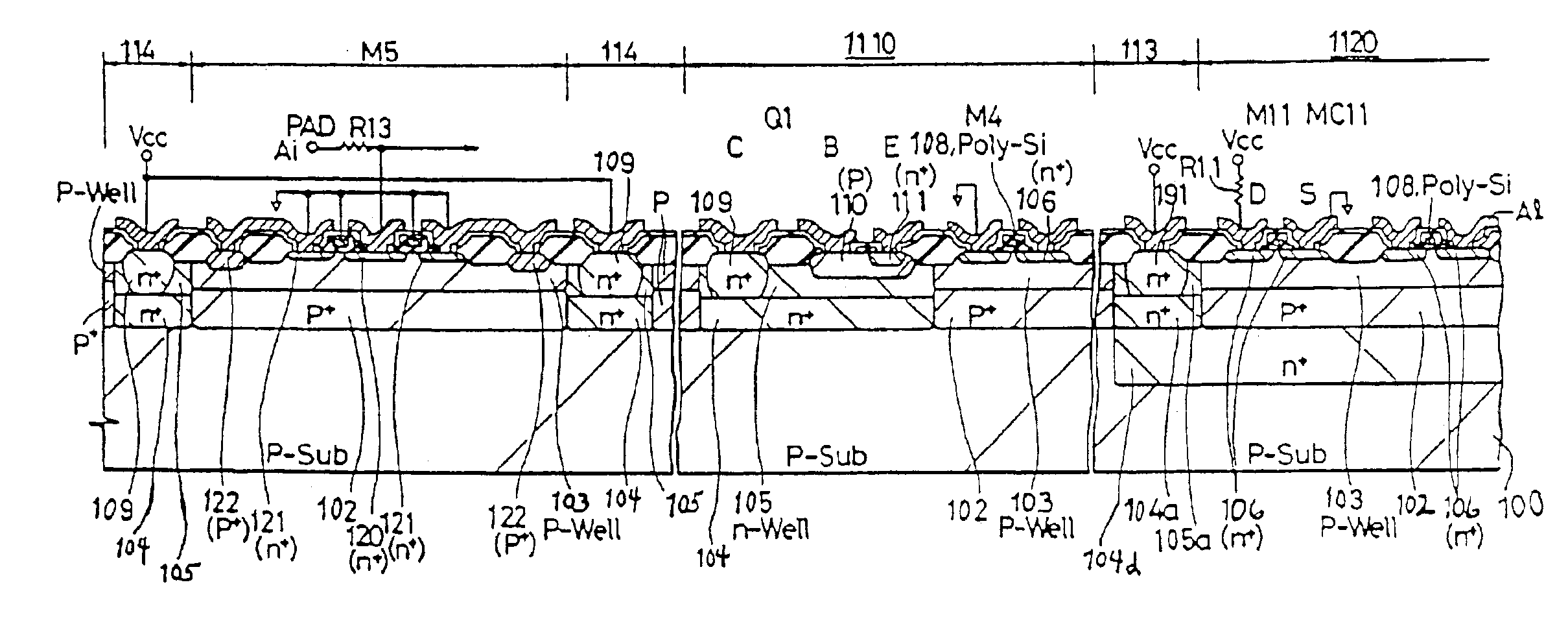

Fabrication of low power CMOS device with high reliability

InactiveUS6853037B2Low consumption powerHigh speed operationTransistorSemiconductor/solid-state device detailsIonMOSFET

A semiconductor device includes a relatively lower threshold level MOSFET and relatively higher threshold level MOSFETs of n- and p-types. The higher threshold level MOSFETs have gate oxide films which is thicker than that of the lower threshold level MOSFET and, in addition, the gate oxide film of the higher threshold level MOSFET of n-type is thicker than that of the higher threshold level MOSFET of p-type. To fabricate the semiconductor device, implantation treatments of fluorine ions are carried out before the gate oxide treatment. Specifically, as for the higher threshold level MOSFETs of n- and p-types, implantation treatments of fluorine ions are independently carried out with unique implantation conditions.

Owner:RENESAS ELECTRONICS CORP

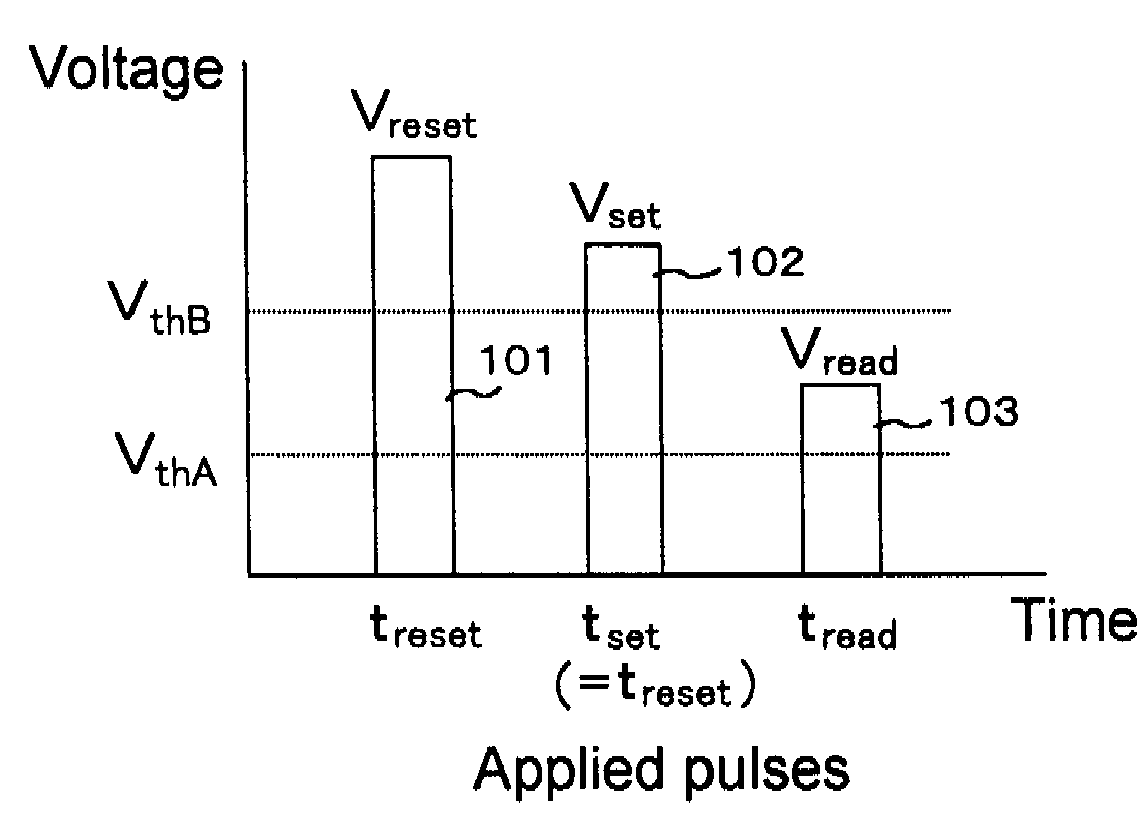

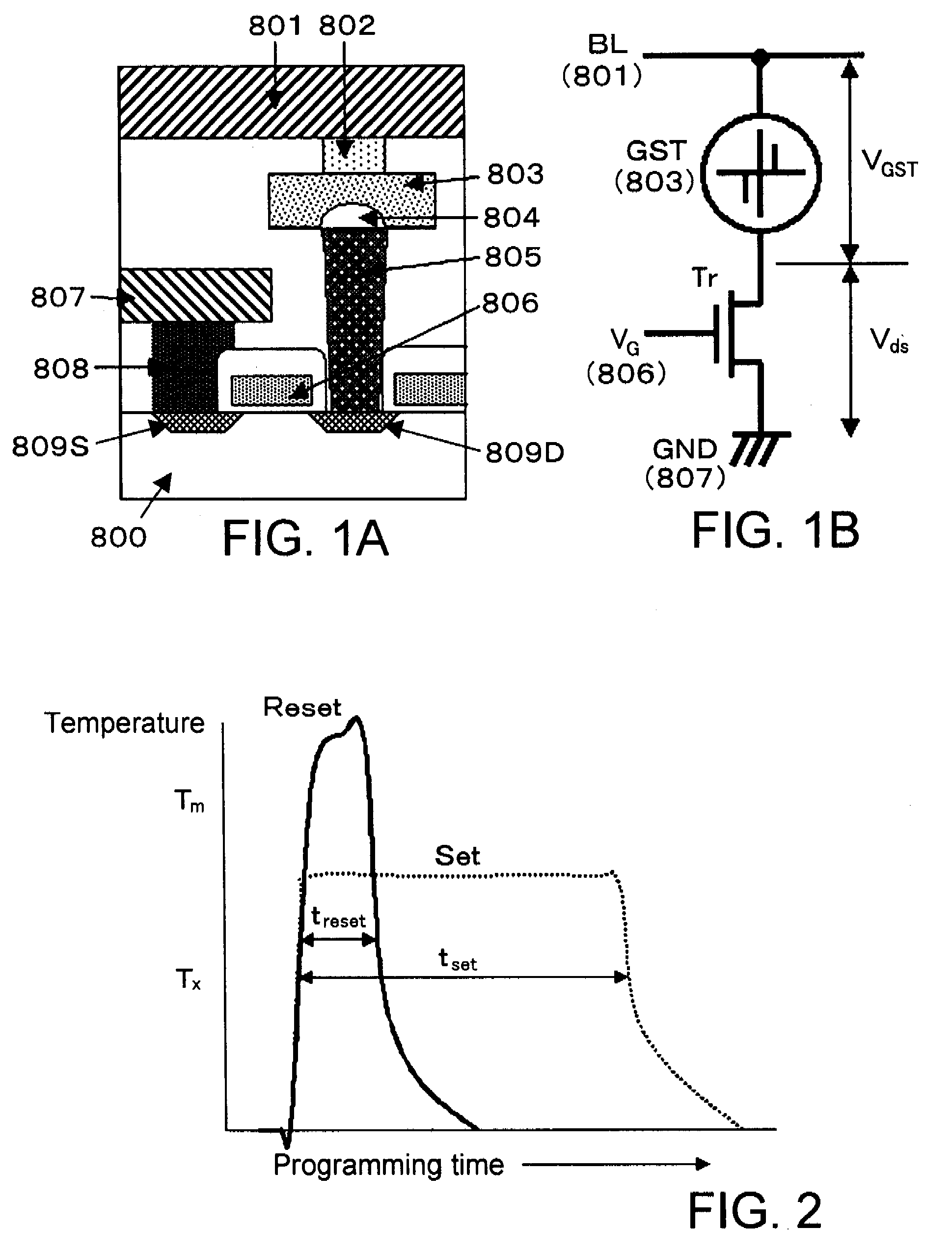

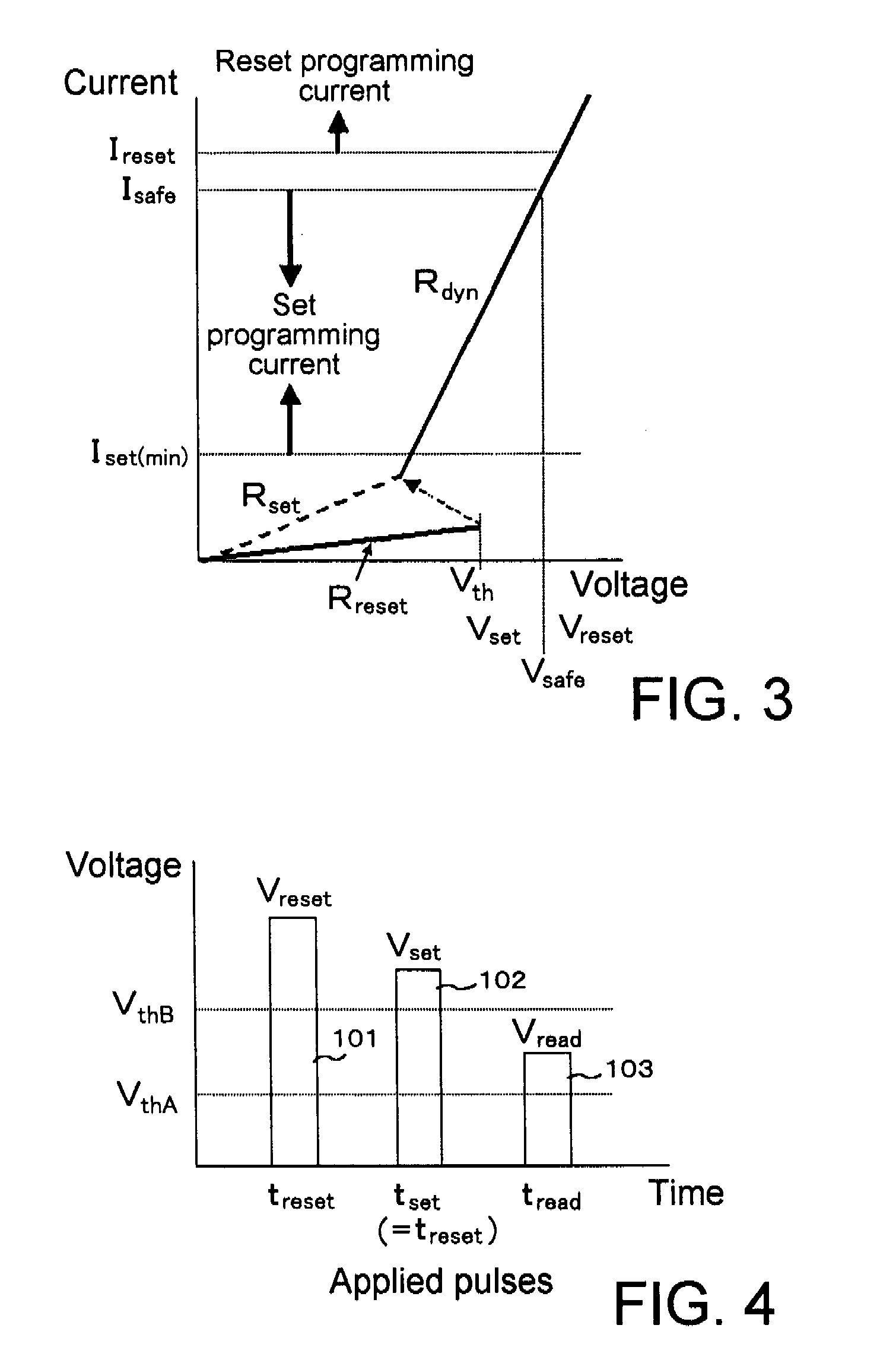

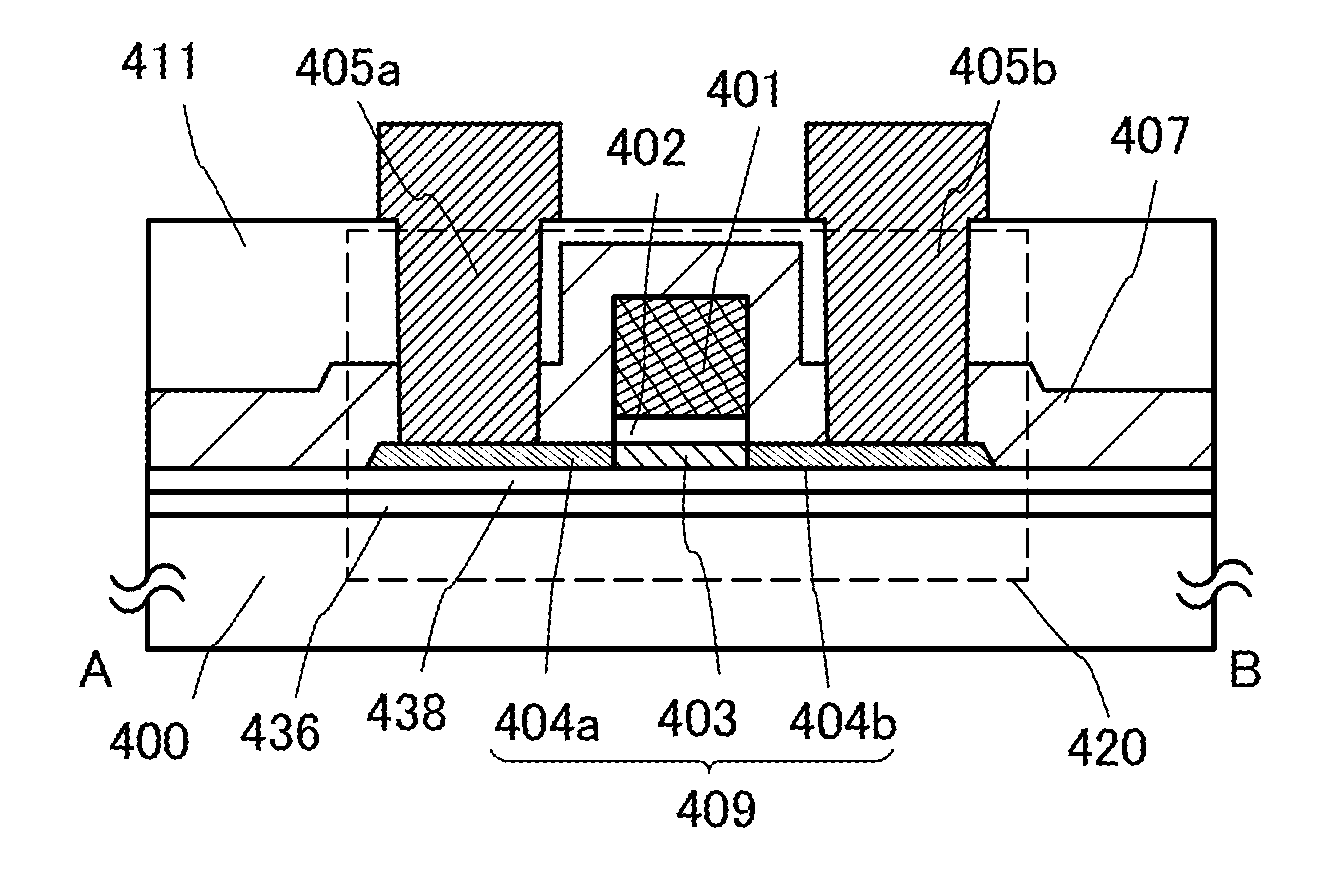

Method for programming phase-change memory and method for reading date from the same

InactiveUS20080212363A1High-speed operationRun at high speedRead-only memoriesDigital storageVoltageEngineering

When a phase-change element that can transition between a reset state (amorphous state) and a set state (crystalline state) is to be caused to transition to the reset state, a first pulse having a first voltage is applied to the phase-change element. The first voltage is higher than the threshold voltage in the reset state, and can cause current to flow that corresponds to an amount of generated heat required for placing the element in the reset state. When the phase-change element is to be caused to transition to the set state, a second pulse having a second voltage and the same time width as the first pulse is applied to the phase-change element. The second voltage that is higher than the threshold voltage but lower than the first voltage, and can cause only a current to flow that does not attain the necessary amount of generated heat.

Owner:LONGITUDE SEMICON S A R L

Semiconductor device and method for manufacturing semiconductor device

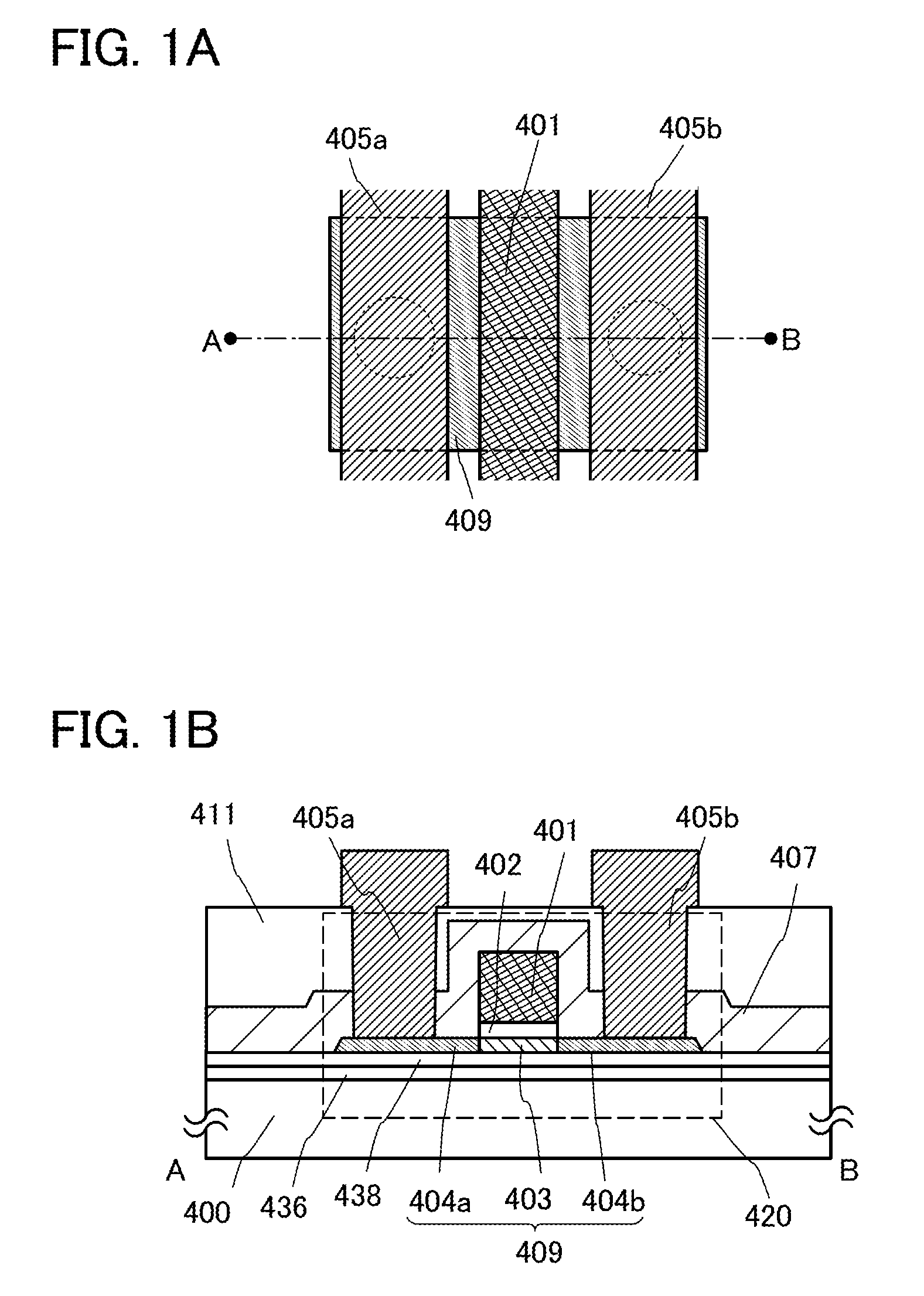

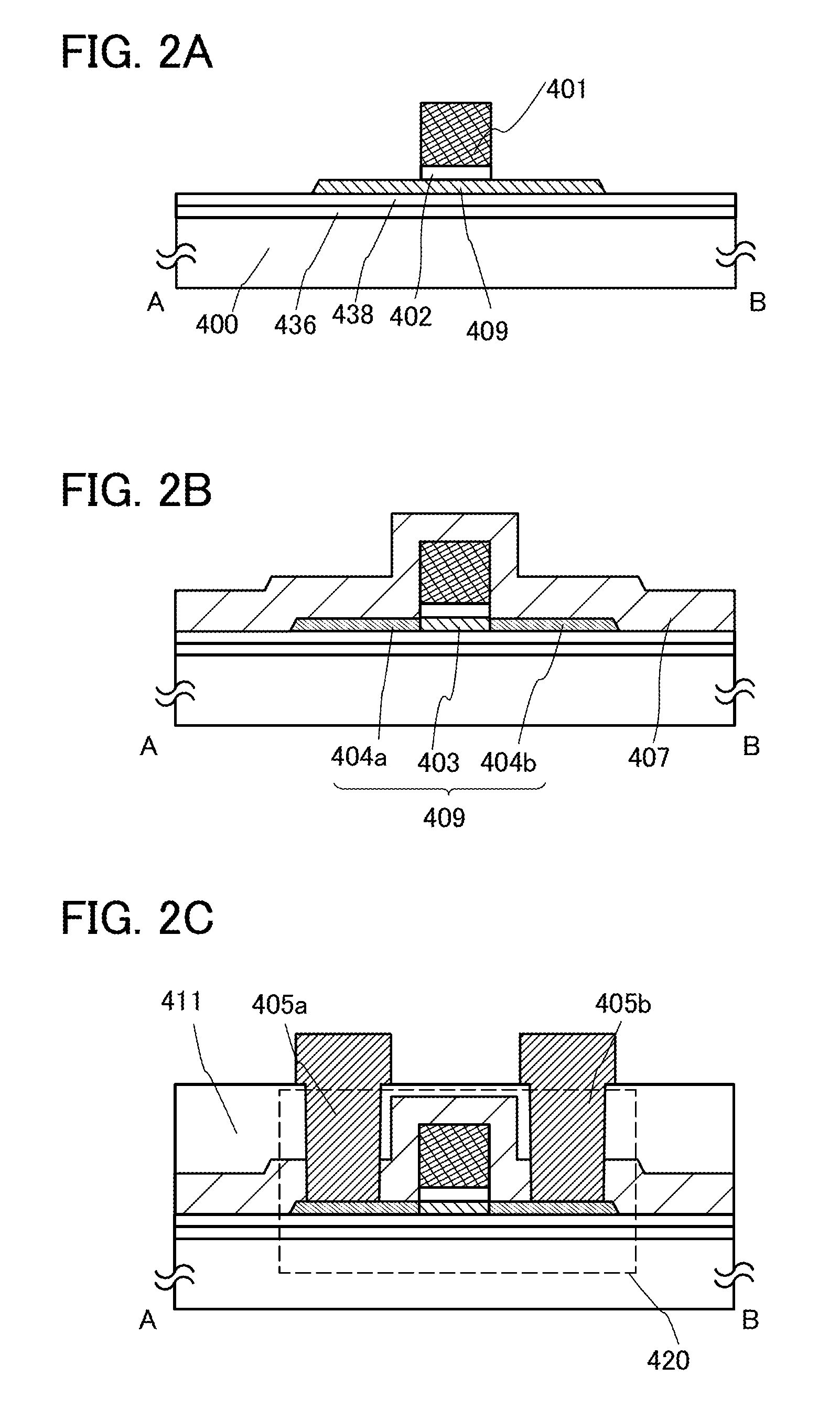

ActiveUS9472682B2Characteristics high-speedHigh-speed operationTransistorSemiconductor/solid-state device manufacturingDevice materialNitrogen

In a top-gate transistor in which an oxide semiconductor film, a gate insulating film, a gate electrode layer, and a silicon nitride film are stacked in this order and the oxide semiconductor film includes a channel formation region, nitrogen is added to regions of part of the oxide semiconductor film and the regions become low-resistance regions by forming a silicon nitride film over and in contact with the oxide semiconductor film. A source and drain electrode layers are in contact with the low-resistance regions. A region of the oxide semiconductor film, which does not contact the silicon nitride film (that is, a region overlapping with the gate insulating film and the gate electrode layer) becomes the channel formation region.

Owner:SEMICON ENERGY LAB CO LTD

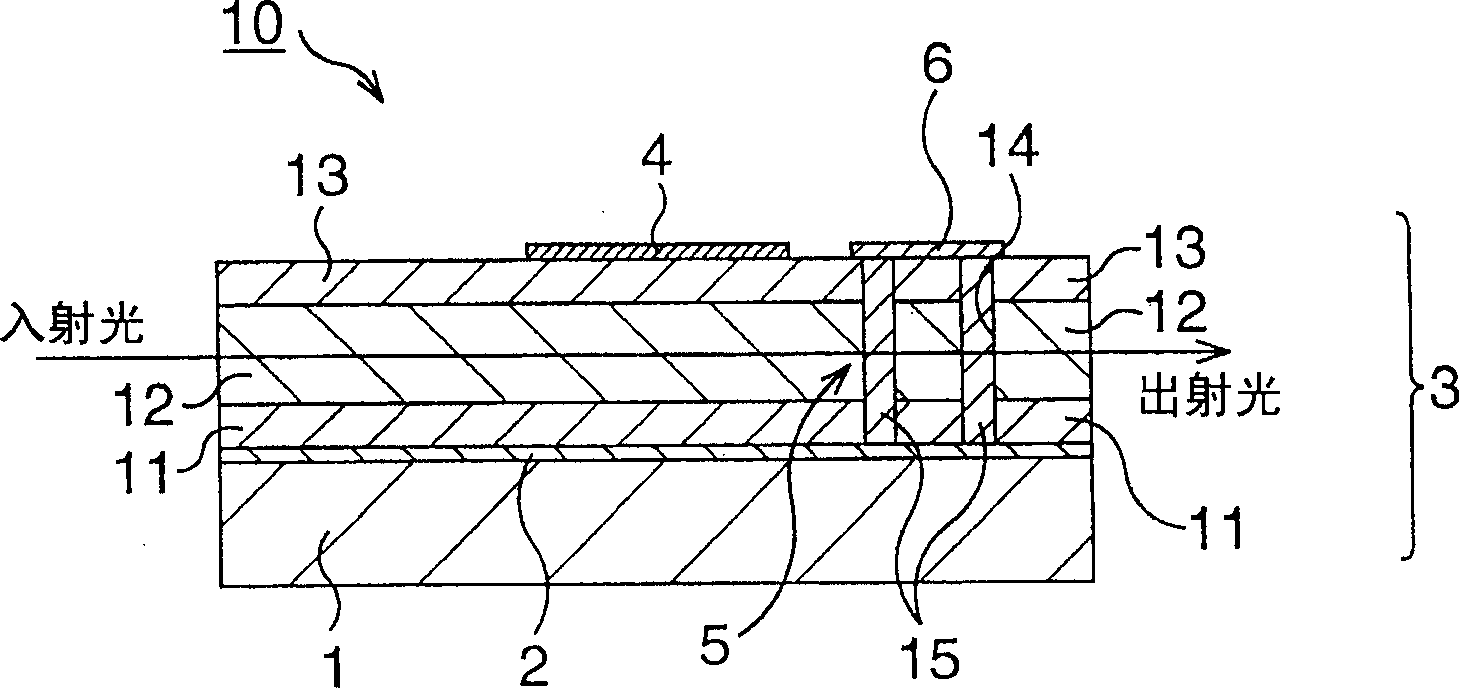

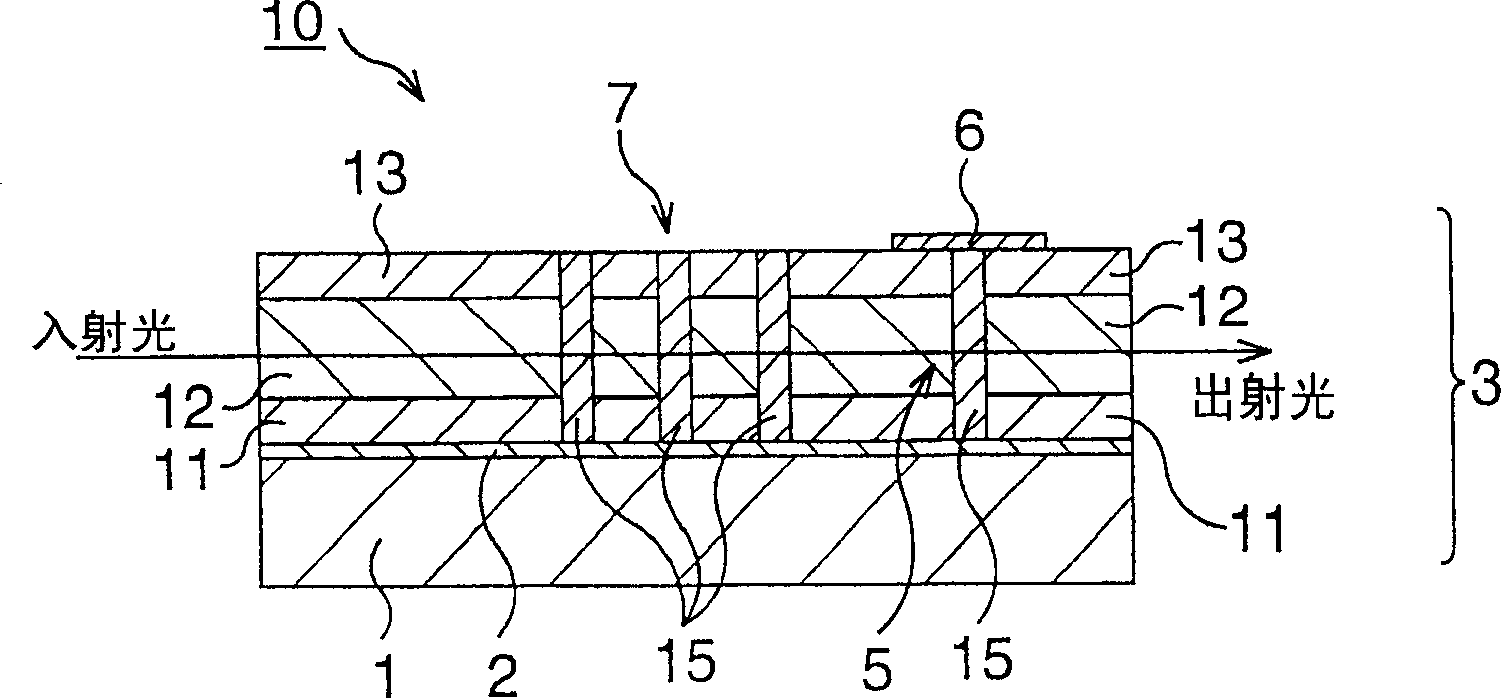

Thin-film transistor

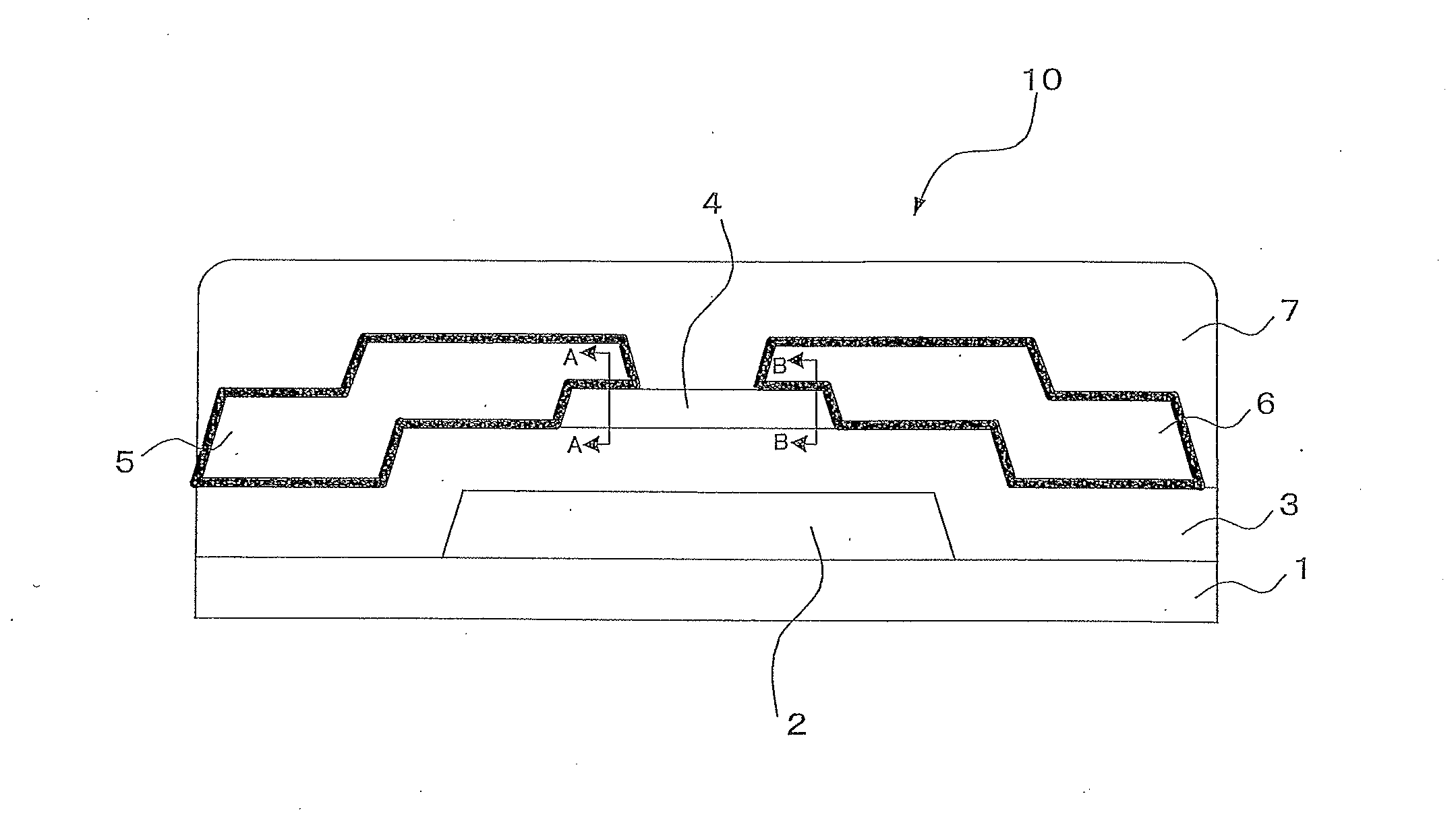

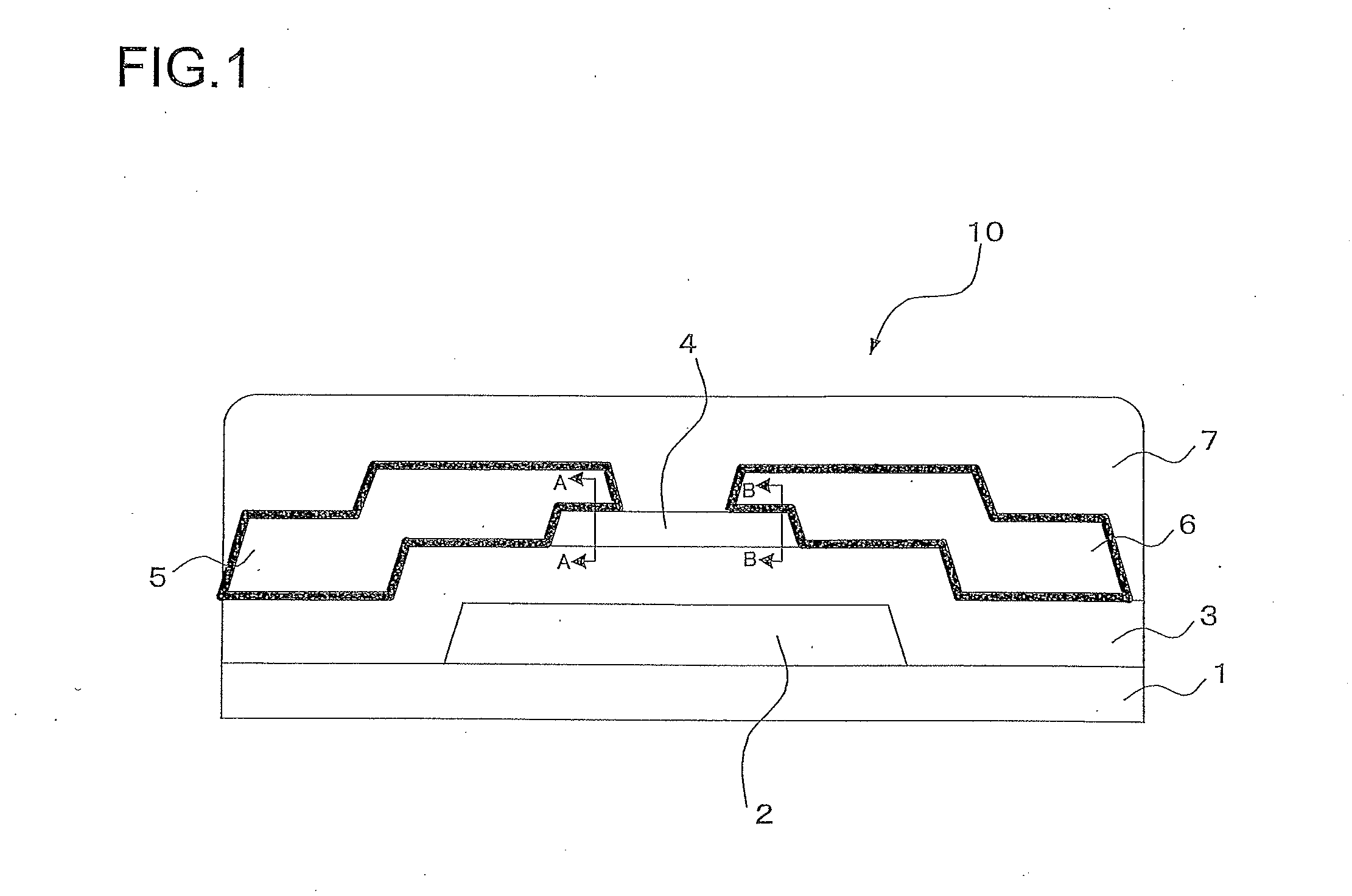

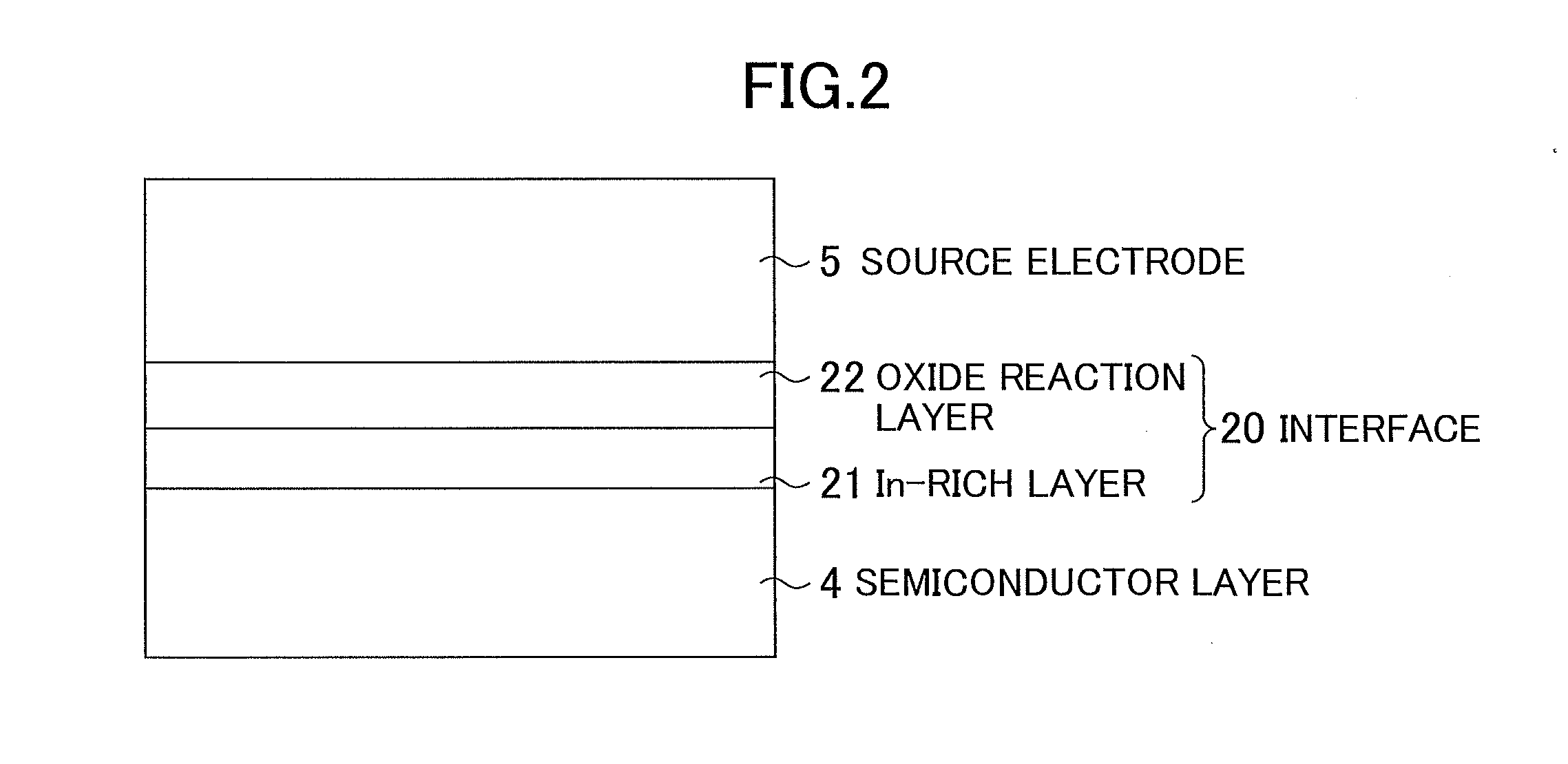

InactiveUS20130112972A1Improve adhesionHigh-speed operationTransistorOxide semiconductorElectrode fabrication

Making it possible to improve adhesion between the semiconductor layer and the electrodes, realize high-speed operation of the thin-film transistor by enhancing ohmic contact between these members, reliably prevent oxidation of the electrode surfaces, and realize an electrode fabrication process with few processing steps. The thin-film transistor 10 of the present invention includes a semiconductor layer 4 composed of oxide semiconductor, a source electrode 5 and a drain electrode 6 that are layers composed mainly of copper, and oxide reaction layers 22 provided between the semiconductor layer 4 and each of the source electrode 5 and drain electrode 6, and high-conductance layers 21 provided between the oxide reaction layers 22 and semiconductor layer 4.

Owner:ADVANCED INTERCONNECT MATERIAL

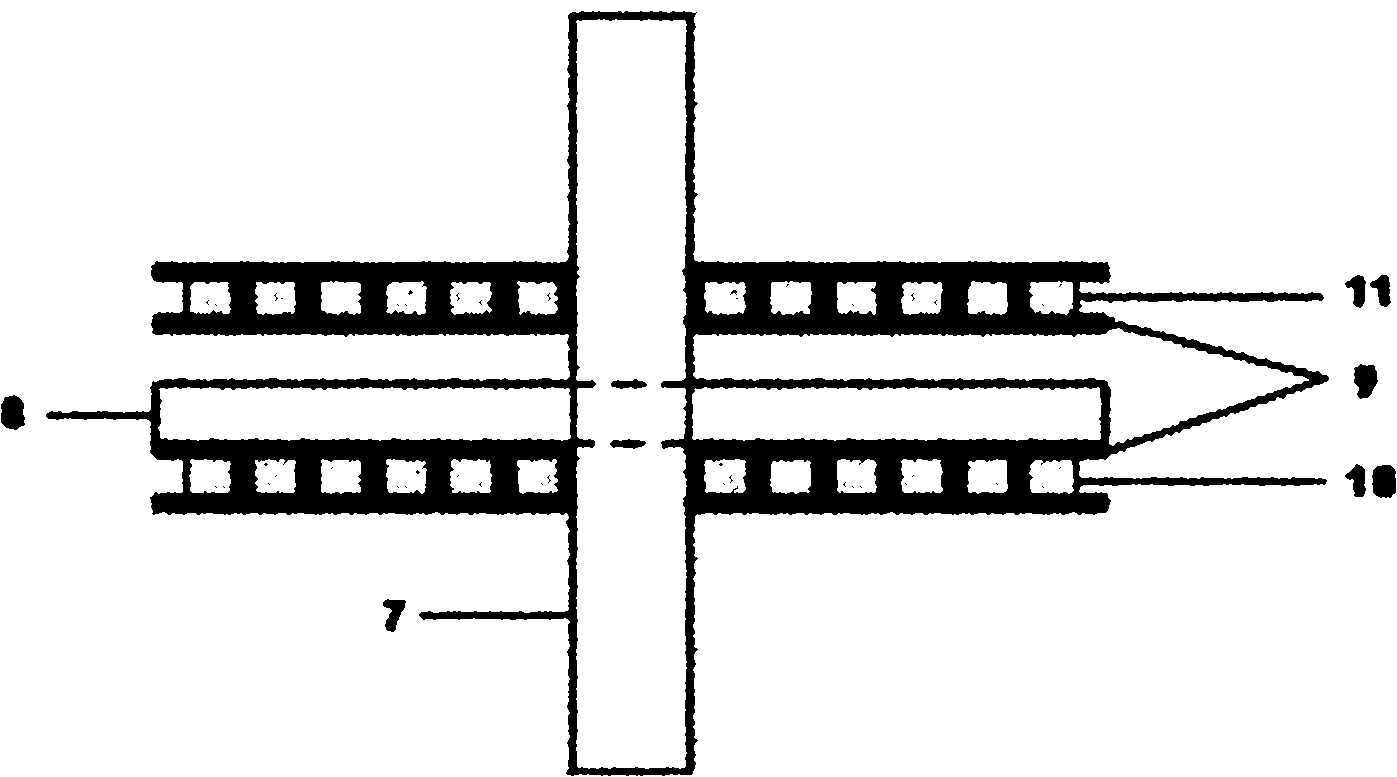

Variable-length bendable fully-flexible mechanical arm structure

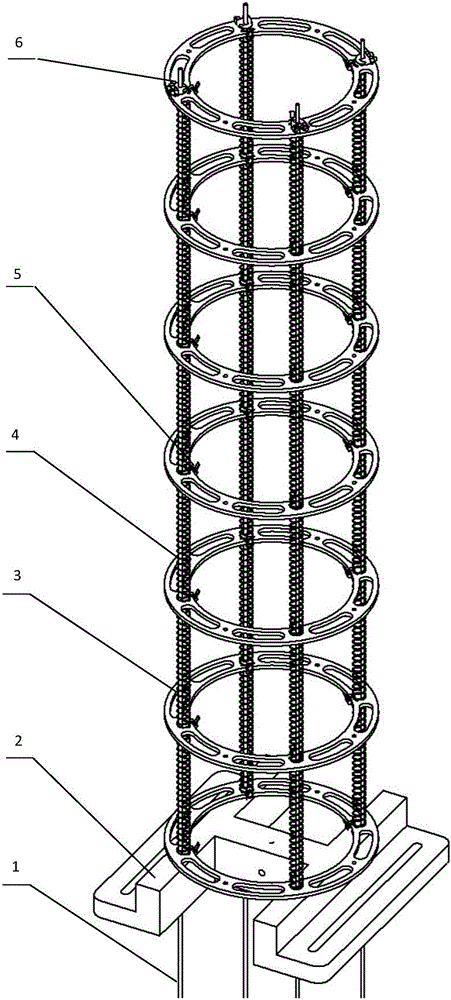

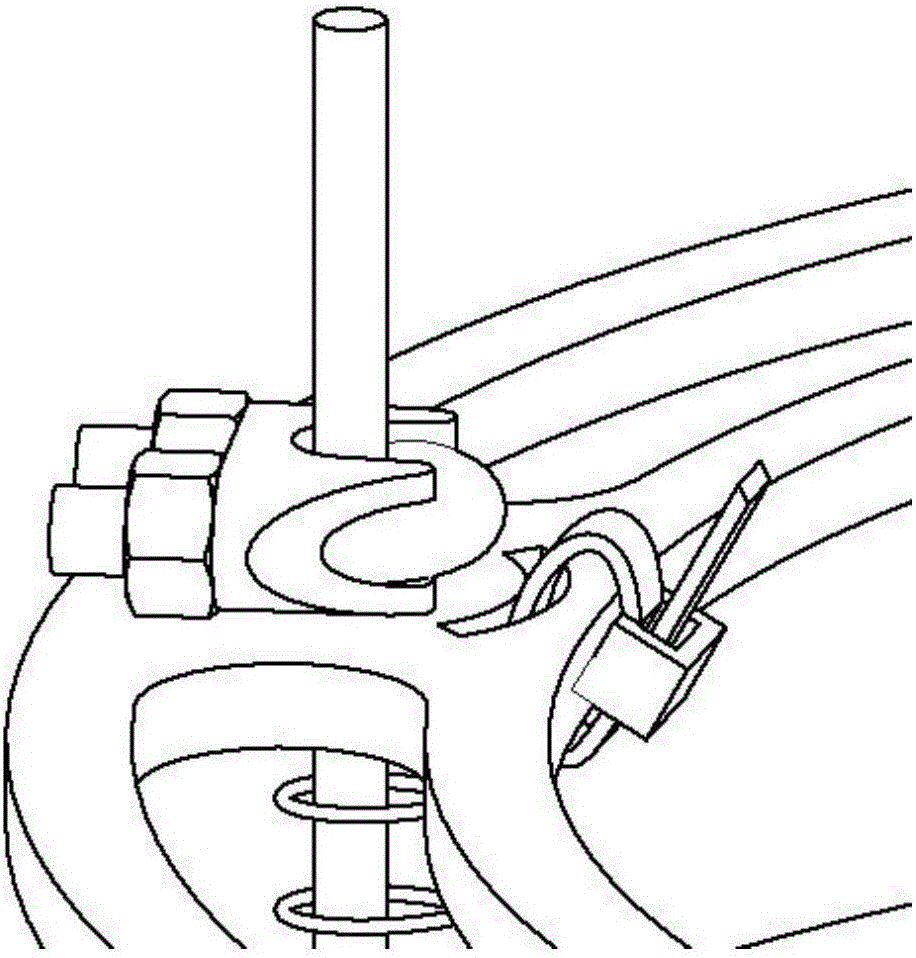

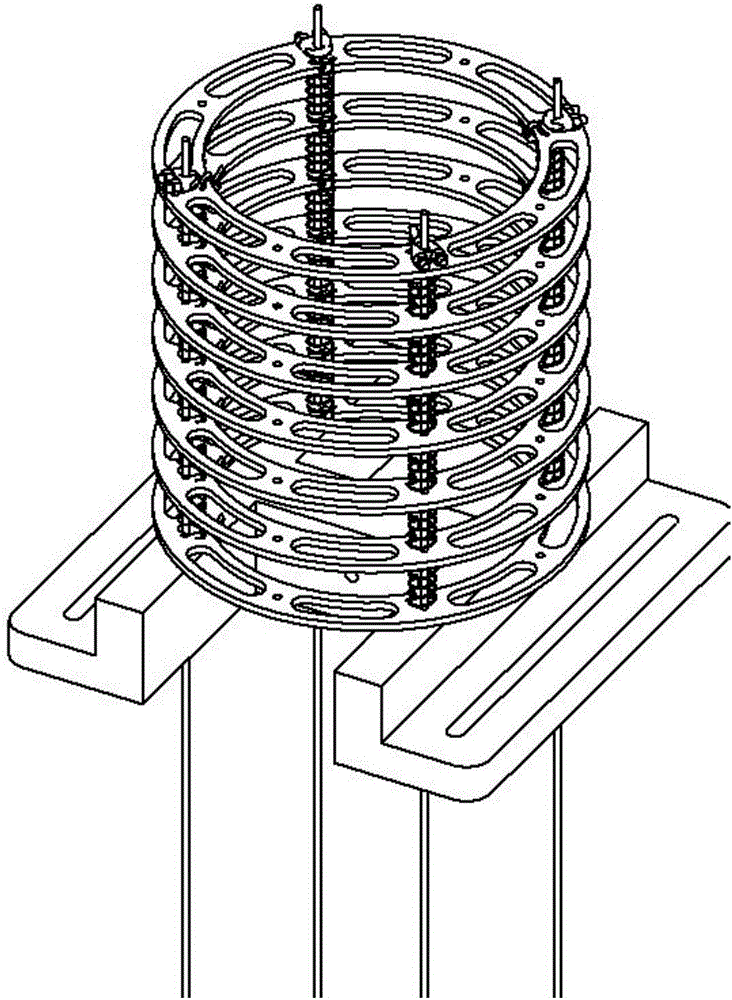

ActiveCN106002988AReduce energy consumptionHigh speed operationProgramme-controlled manipulatorAttitude controlEngineering

The invention discloses a variable-length bendable fully-flexible mechanical arm structure. The structure is a fully-flexible mechanical arm device having a posture controlled by elastic rods, capable of telescoping, and having a tail-end position capable of achieving any point in 360 degrees. The flexible mechanical arm device is composed of the elastic rods, a base, springs, metal section sheets, binding belts and U-shaped buckles. The four elastic rods are driven through slide tables of servo motors, thus posture control for the flexible mechanical arm and position control for a free end at the top are realized. The structure is reliable in stability and complete in function, and the tail-end position is capable of achieving any position in an outer envelope surface.

Owner:BEIJING UNIV OF TECH

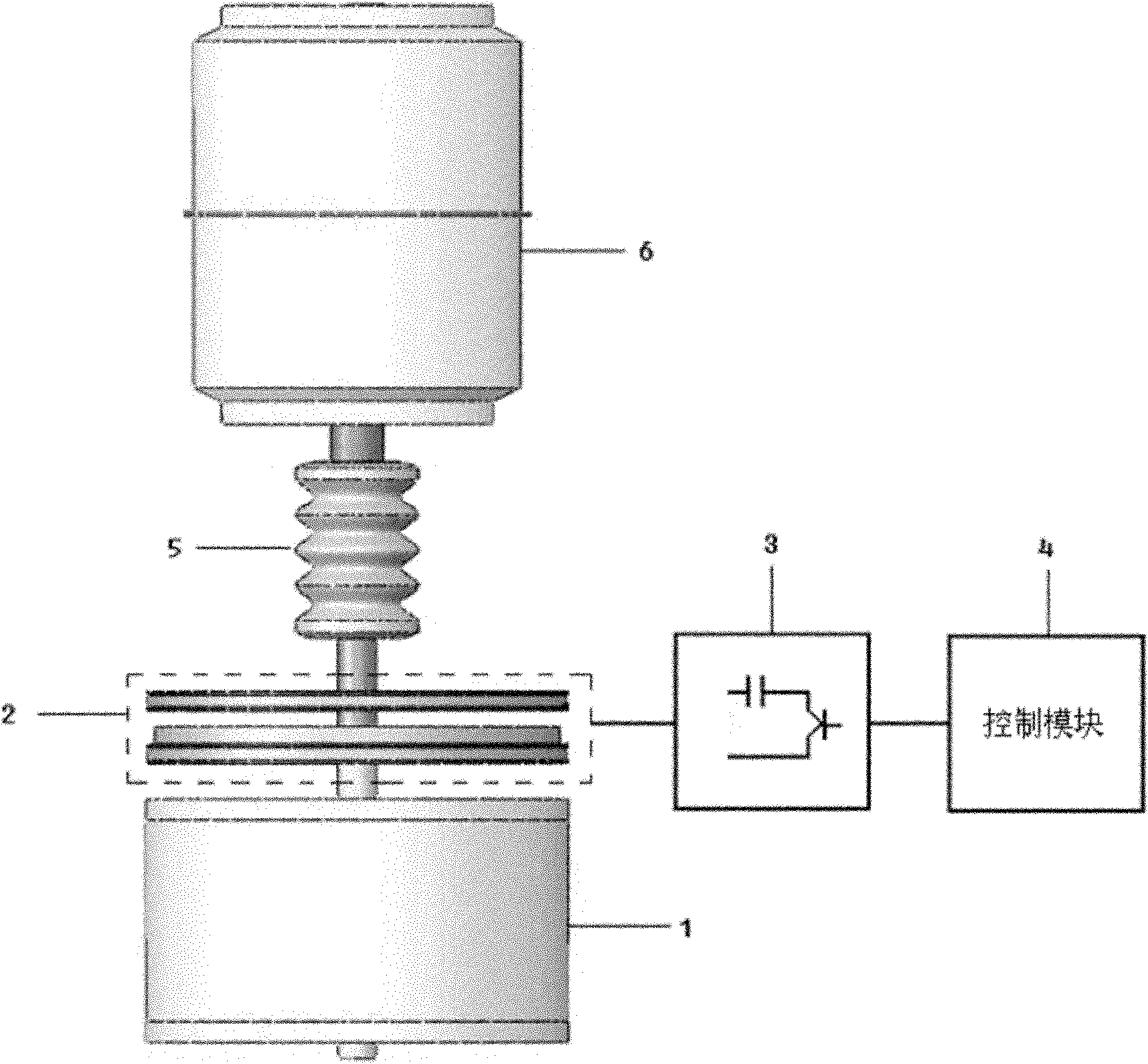

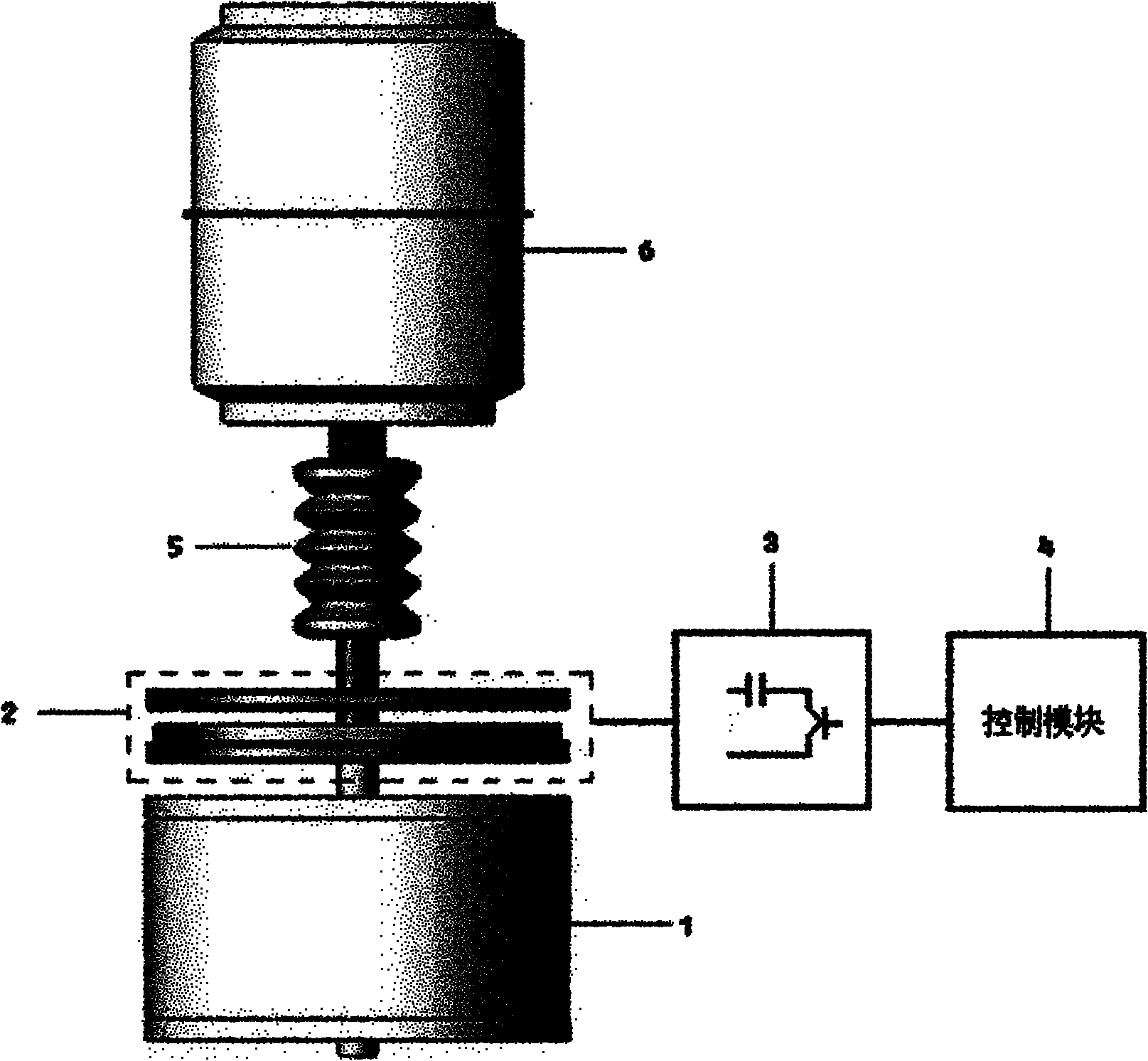

Anti-hopping vacuum contactor of high-speed frame-type repulsion mechanism

InactiveCN102110546AMeet basic needsHigh speed operationHigh-tension/heavy-dress switchesAir-break switchesElectric power transmissionElectric discharge

The invention discloses an anti-hopping vacuum contactor of a high-speed frame-type repulsion mechanism, which belongs to the technical fields of electric engineering and machinery. In the invention, the high-speed frame-type repulsion mechanism is matched with a permanent magnet mechanism to manufacture an operation part of a high-speed contactor, and the operation part is used for driving a vacuum arc extinguish chamber to form a high-speed vacuum contactor. By the high-speed frame-type repulsion mechanism used by the contactor, an opening coil and a closing coil are arranged in a pure iron frame to ensure that the coils cannot be damaged in the high-speed movement process. Due to the adoption of the permanent magnet mechanism, the position of the vacuum contactor can be kept, and electric energy can be saved. In the repulsion mechanism, electric discharge stimulation to the closing coil is used at the final stage of the opening operation, so that collision hopping caused by a high-speed opening action in short stroke can be effectively prevented. In the invention, a high-efficient, reliable and energy-saving contactor device is provided for a switch used in occasions in which high-speed operation is required, such as a power transmission occasion, a system protection occasion and the like, and the vacuum contactor has a simple structure and is easy to maintain.

Owner:DALIAN UNIV OF TECH

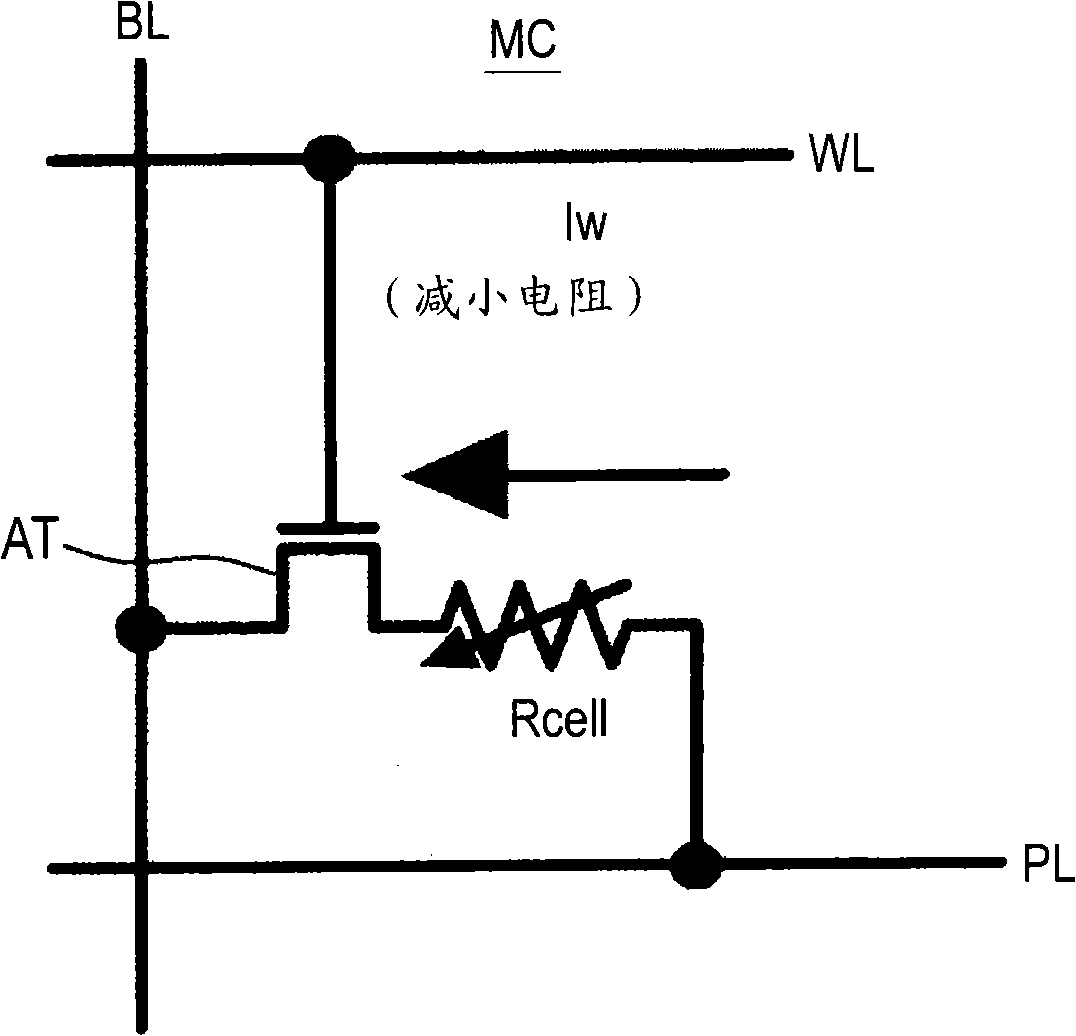

Variable resistance memory device

InactiveCN101789262ASmall sizeHigh speed operationRead-only memoriesDigital storageCommon lineStorage cell

A variable resistance memory device includes: a first common line; a second common line; plural memory cells each formed by serially connecting a memory element, resistance of which changes according to applied voltage, and an access transistor between the second common line and the first common line; a common line pass transistor connected between the first common line and a supply node for predetermined voltage; and a driving circuit that controls voltage of the second common line, the predetermined voltage, and voltage of a control node of the common line pass transistor and drives the memory cells. According to the invention, the variable resistance memory device can control the size of the drive circuit and make the high-speed operation possible.

Owner:SONY GRP CORP

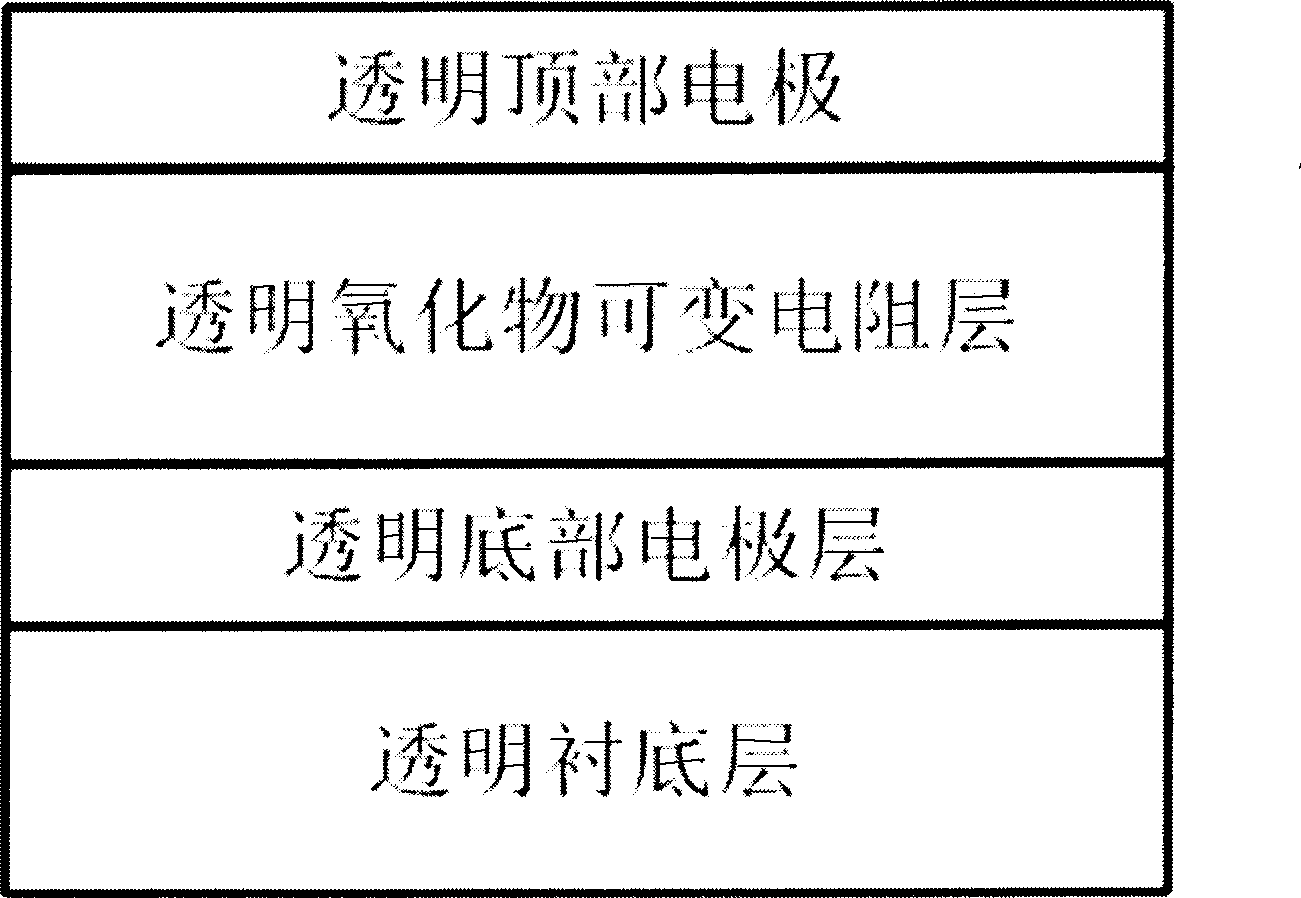

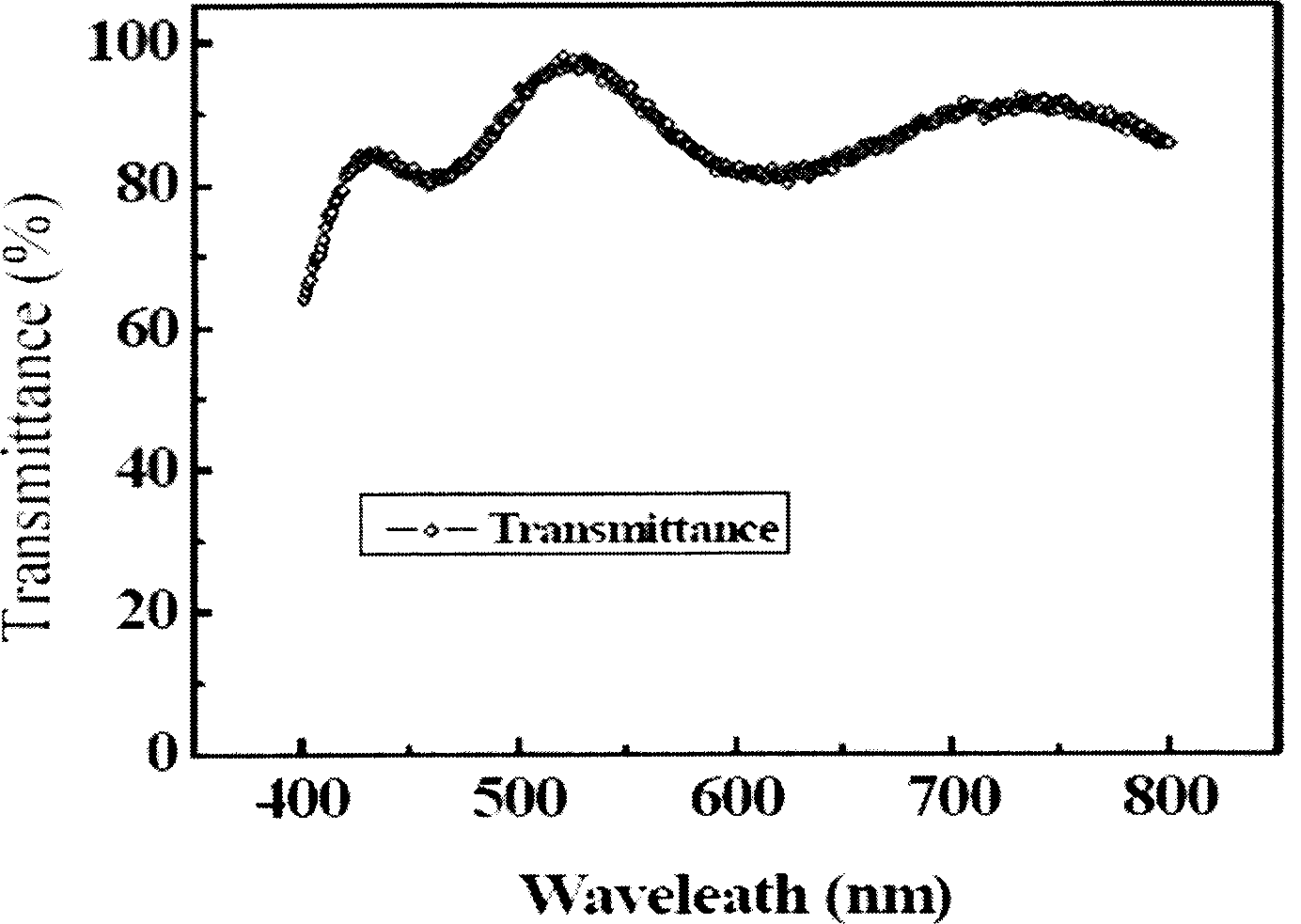

Transparent resistor type non-volatile memory

InactiveCN101478031AExcellent optical propertiesStable electrical characteristicsSolid-state devicesDigital storageElectrical resistance and conductanceRandom access memory

The invention discloses a completely transparent nonvolatile memory, which comprises a transparent substrate, a transparent bottom electrode layer formed on the substrate, a transparent record medium layer formed on the bottom electrode, and a transparent top electrode layer formed on the transparent record medium layer, wherein, the transparent substrate is an insulator; and the transparent record medium layer has the properties of variable resistors. The transparent memory not only has the characteristics of RRAM (resistance random access memory) but also has good light transmittance. Accordingly, the transparent memory can be widely used in the field of photoelectrical display, photoelectrical storage and other transparent electronic product field to provide effective path for the integration of optical products and memories.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

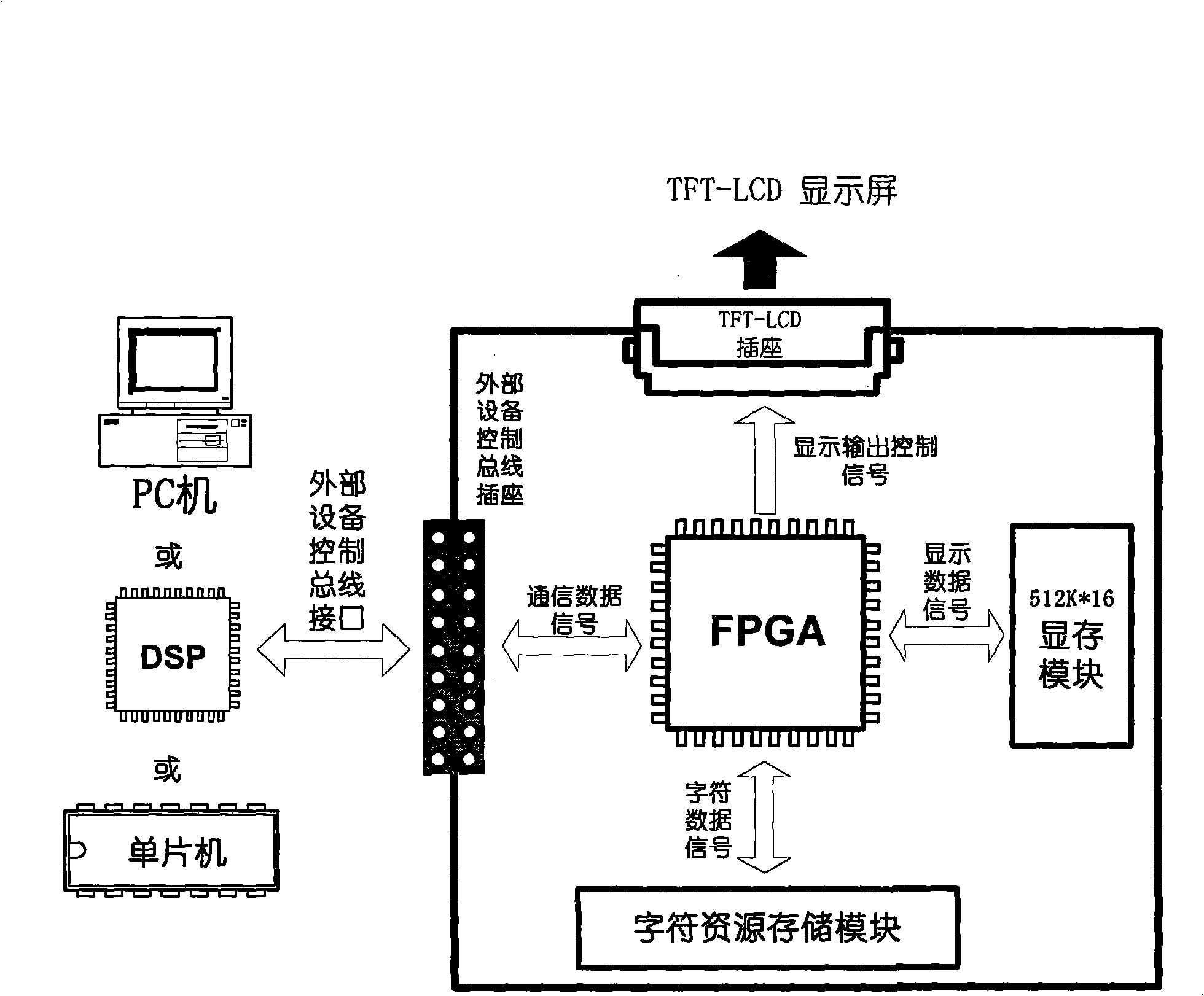

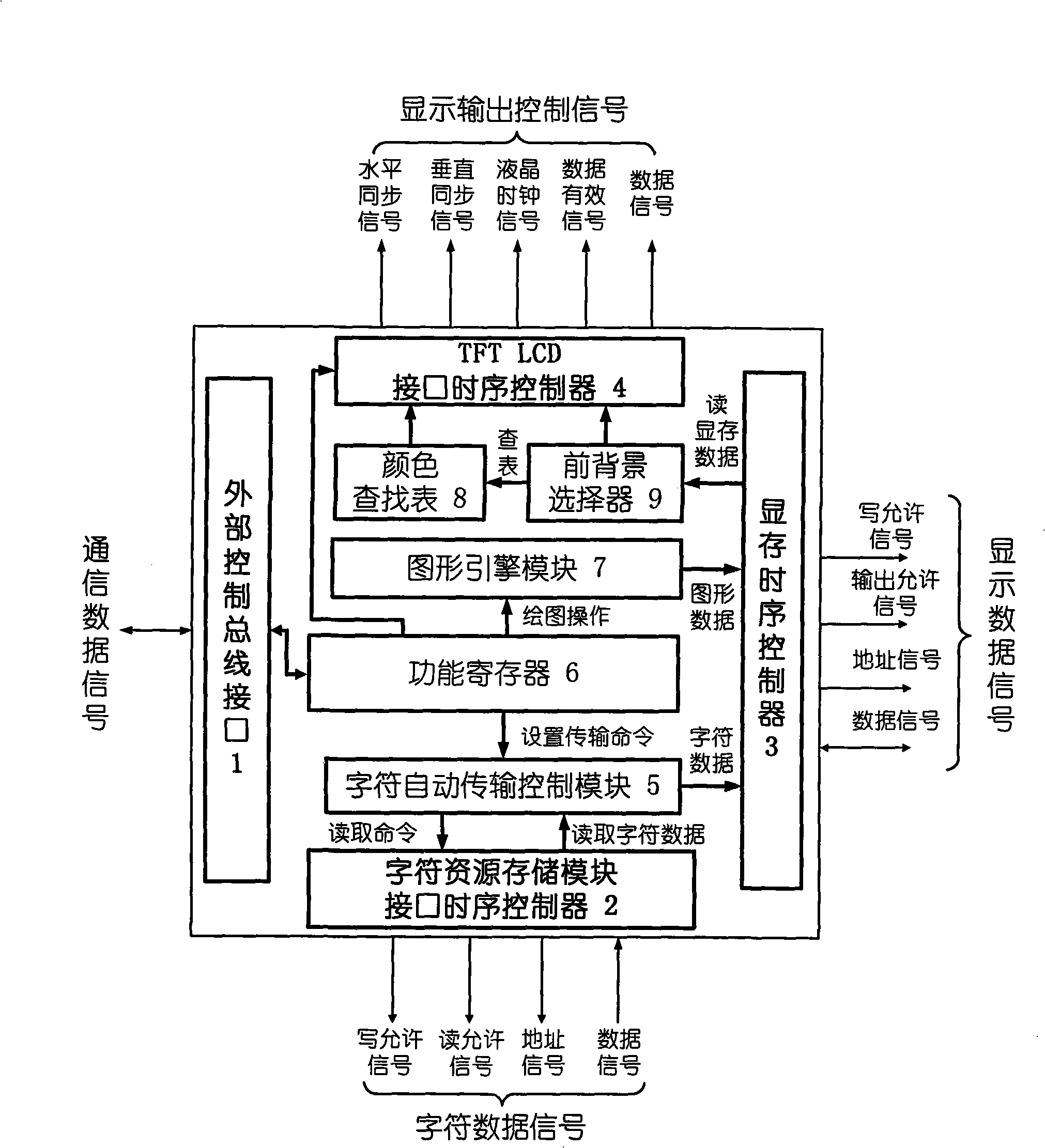

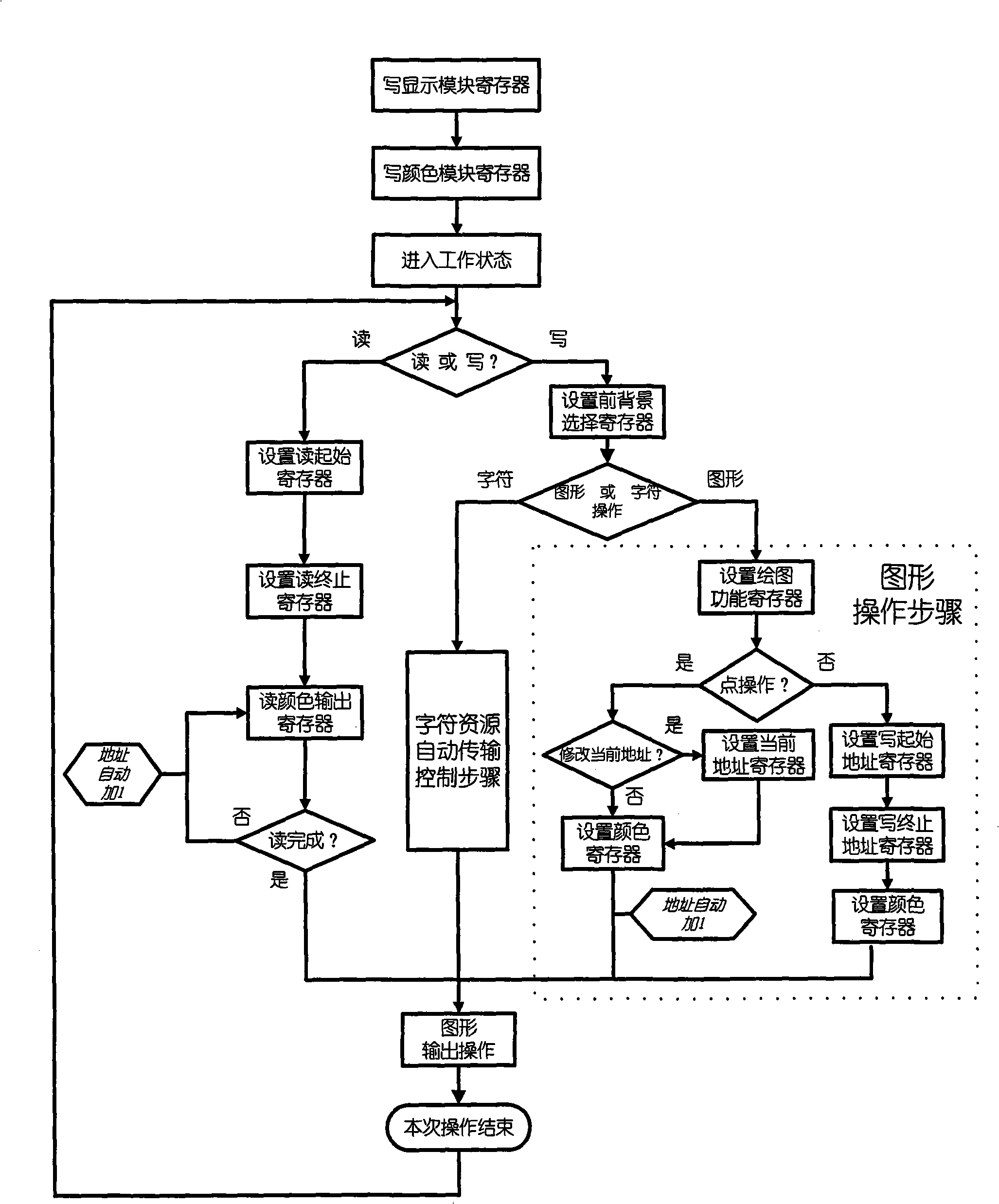

LCD graphical display controller and control method

InactiveCN101315756ARealize the graphics output functionHigh speed operationStatic indicating devicesGraphical displayControl bus

The invention discloses a liquid crystal graphical display controller and a control method. The controller comprises an FPGA module, a video memory module, a storage module for character resources, an external device control bus hut and a TFT-LCD socket, and is characterized in that: the FPGA module includes bidirectional communication data connection between an external bus extended interface and the external device control bus hut, thus realizing the interaction with an external control device; a display output control signal of the FPGA module is connected with the TFT-LCD socket to realize the control of the TFT-LCD display; a display data signal of the FPGA module is both-way connected with the video memory module to realize read-write operation for the displayed content; and a character data signal of the FPGA module is both-way connected with the storage module for character resources to realize the read control of the storage module for character resources.

Owner:XI AN JIAOTONG UNIV

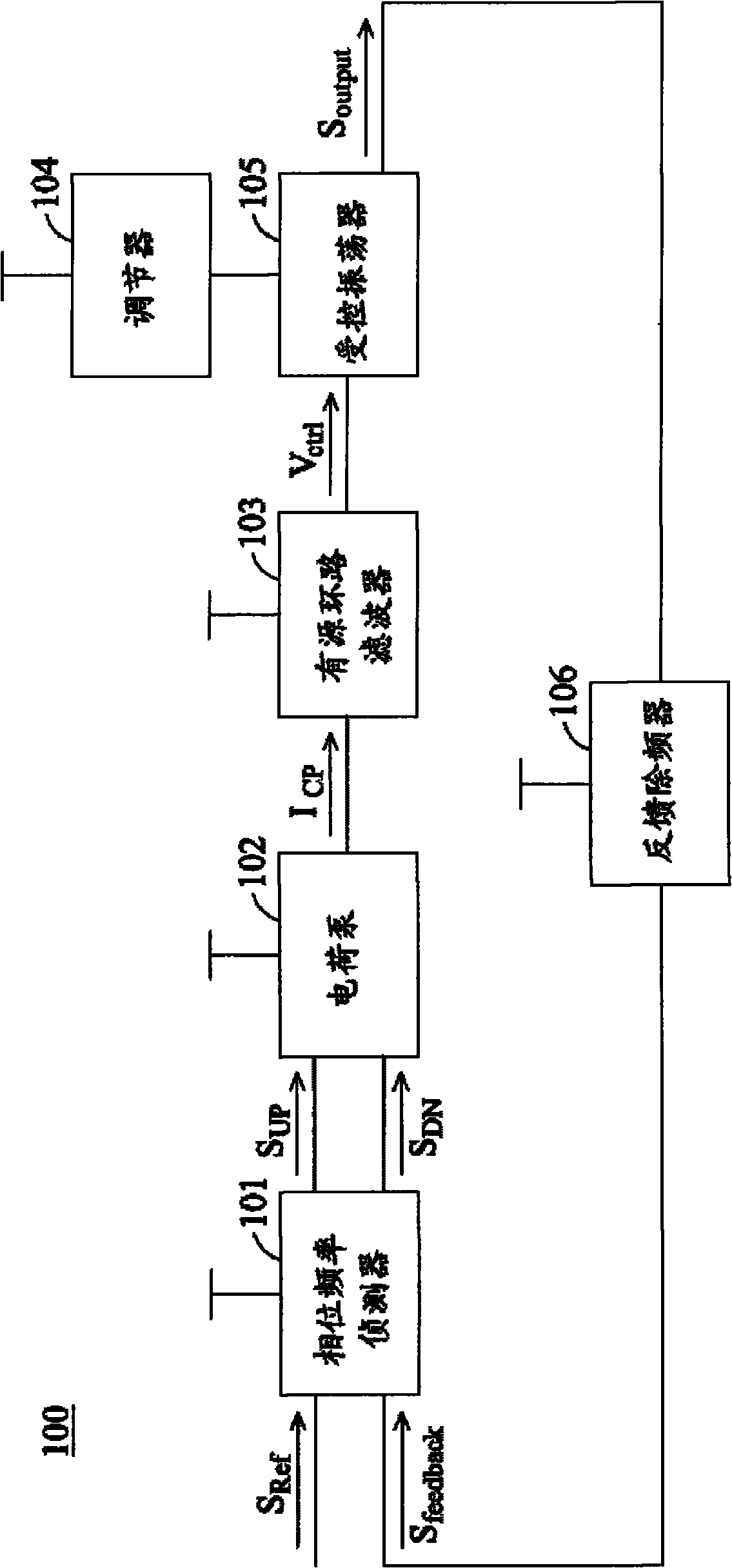

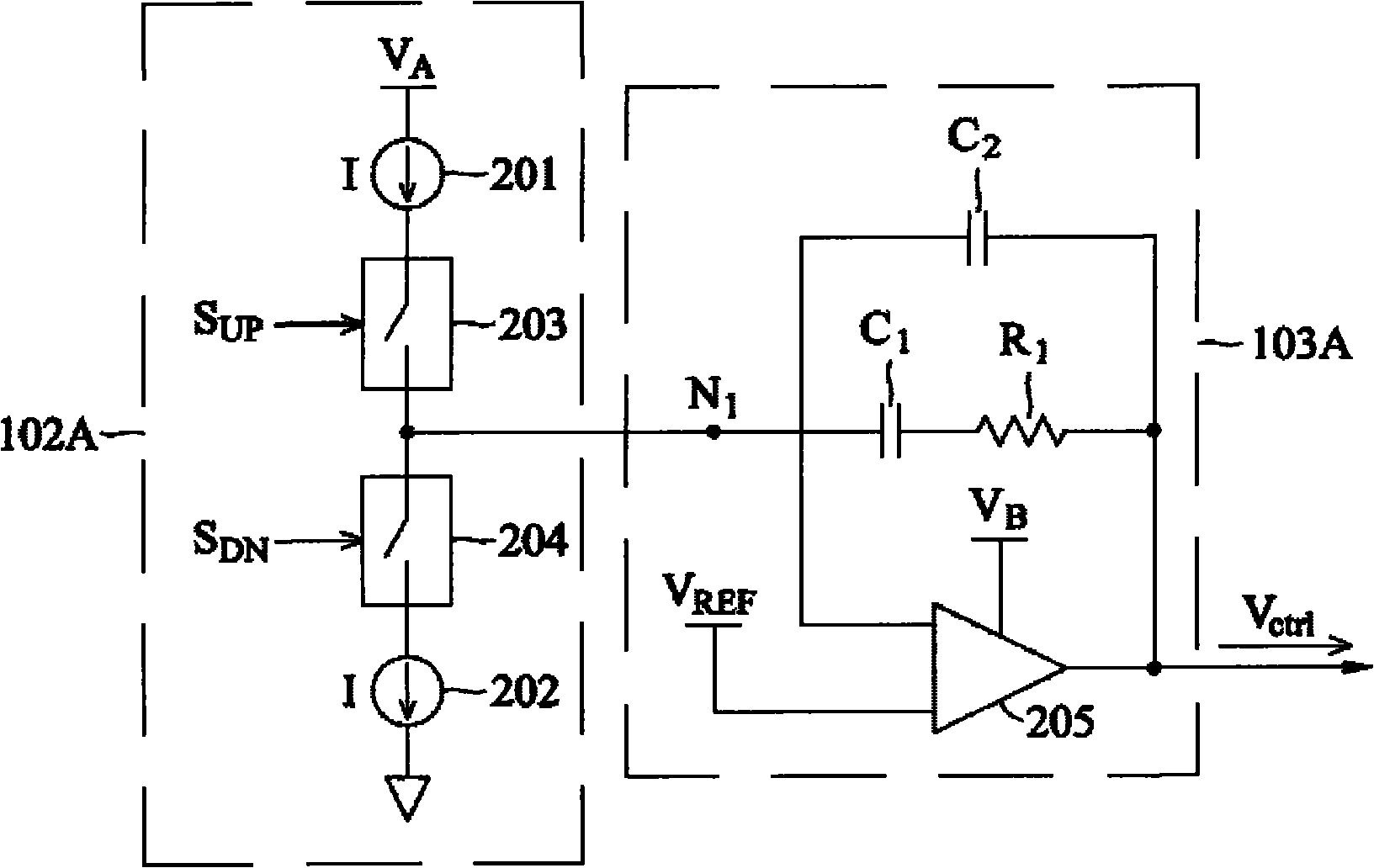

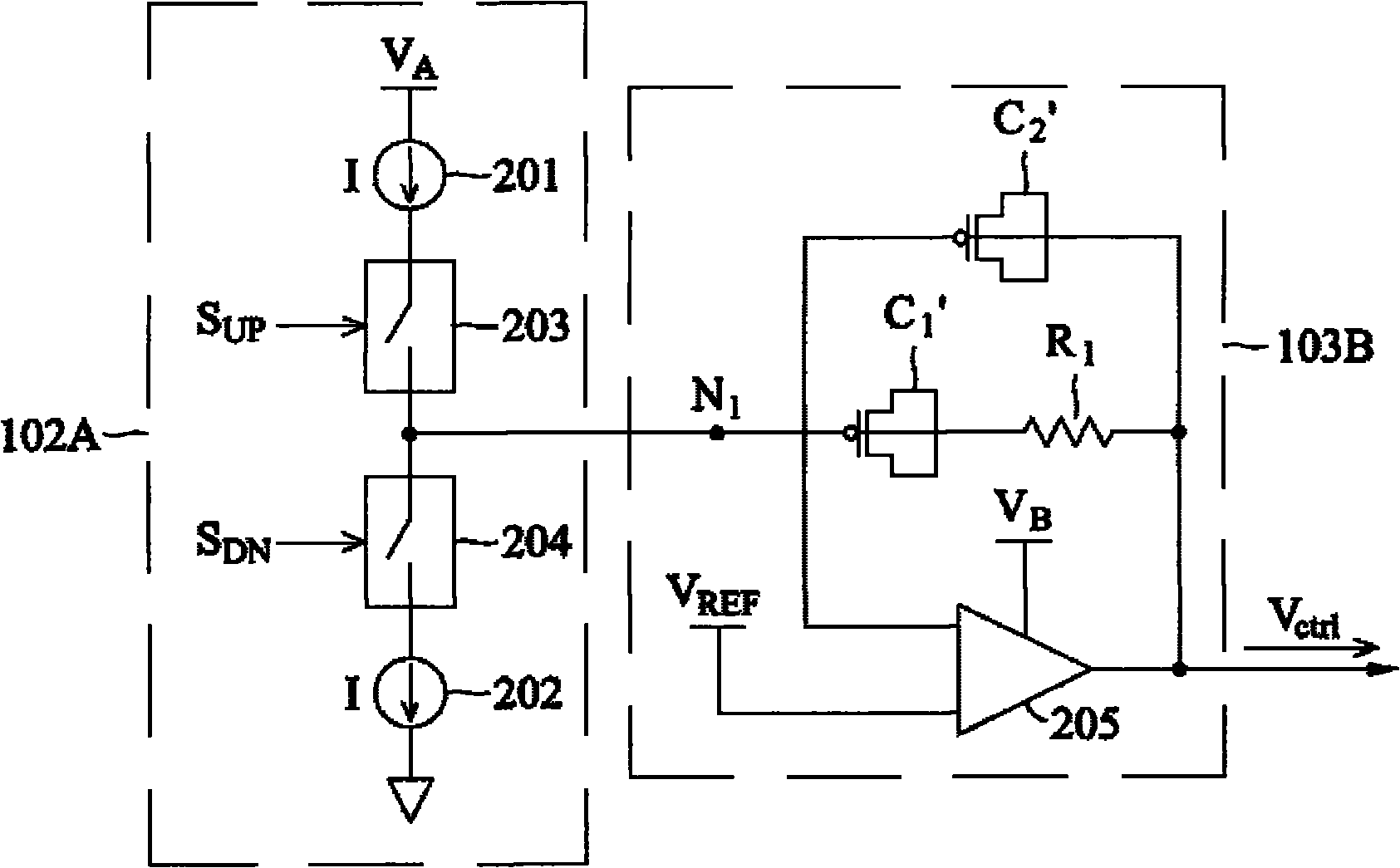

Phase lock loop circuits

Owner:MEDIATEK INC

Semiconductor device and method for manufacturing semiconductor device

ActiveUS20130092940A1Run at high speedReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesResistEngineering

To provide a miniaturized transistor having high electric characteristics. A conductive film to be a source electrode layer and a drain electrode layer is formed to cover an oxide semiconductor layer and a channel protection layer, and then a region of the conductive film, which overlaps with the oxide semiconductor layer and the channel protection layer, is removed by chemical mechanical polishing treatment. Precise processing can be performed accurately because an etching step using a resist mask is not performed in the step of removing part of the conductive film to be the source electrode layer and the drain electrode layer. With the channel protection layer, damage to the oxide semiconductor layer or a reduction in film thickness due to the chemical mechanical polishing treatment on the conductive film can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

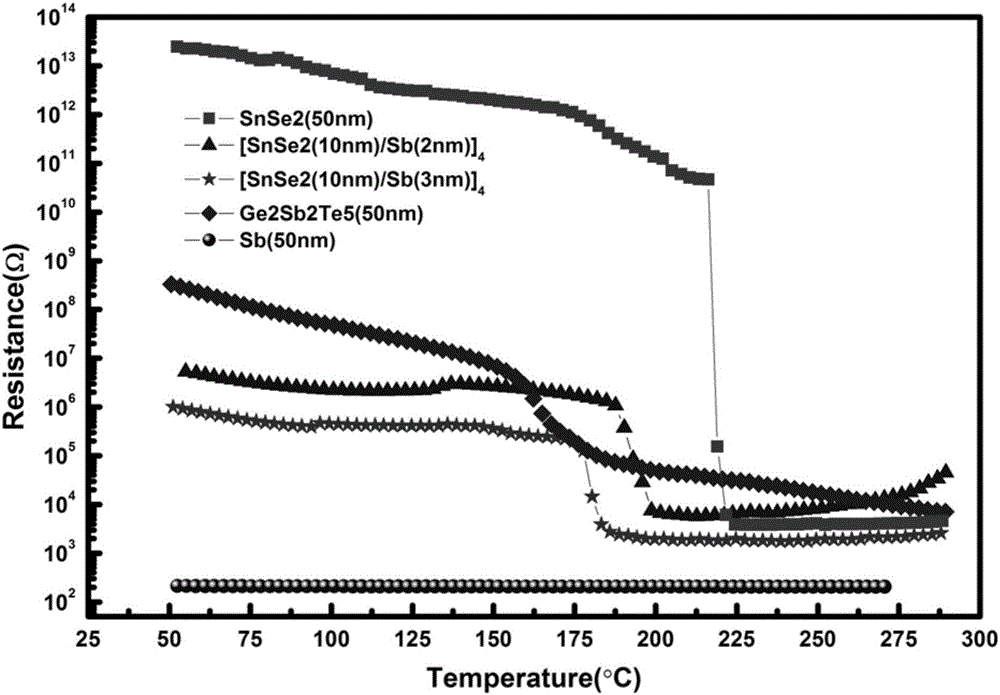

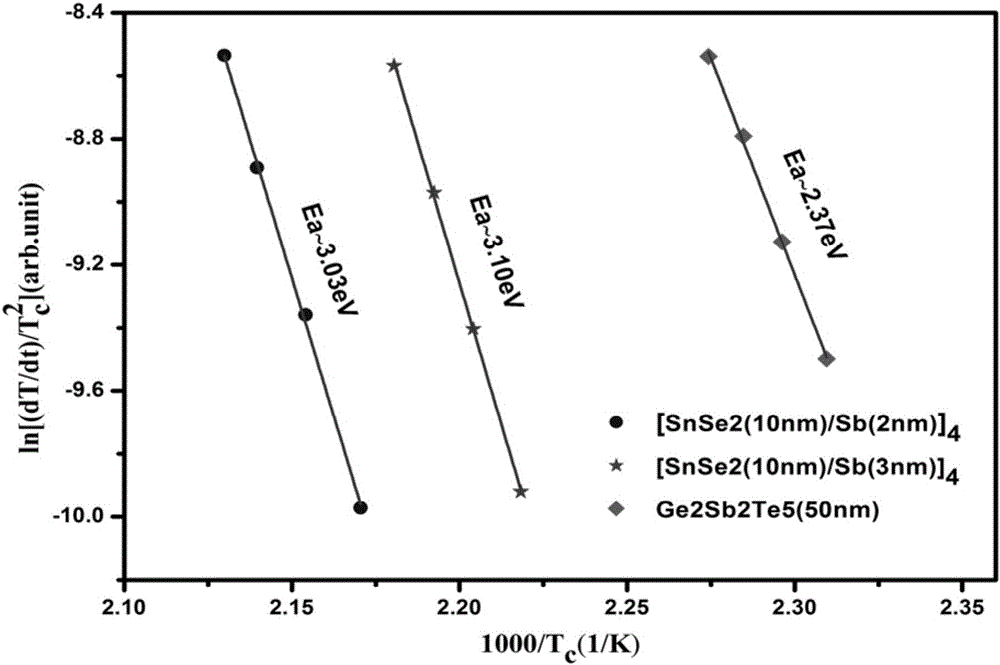

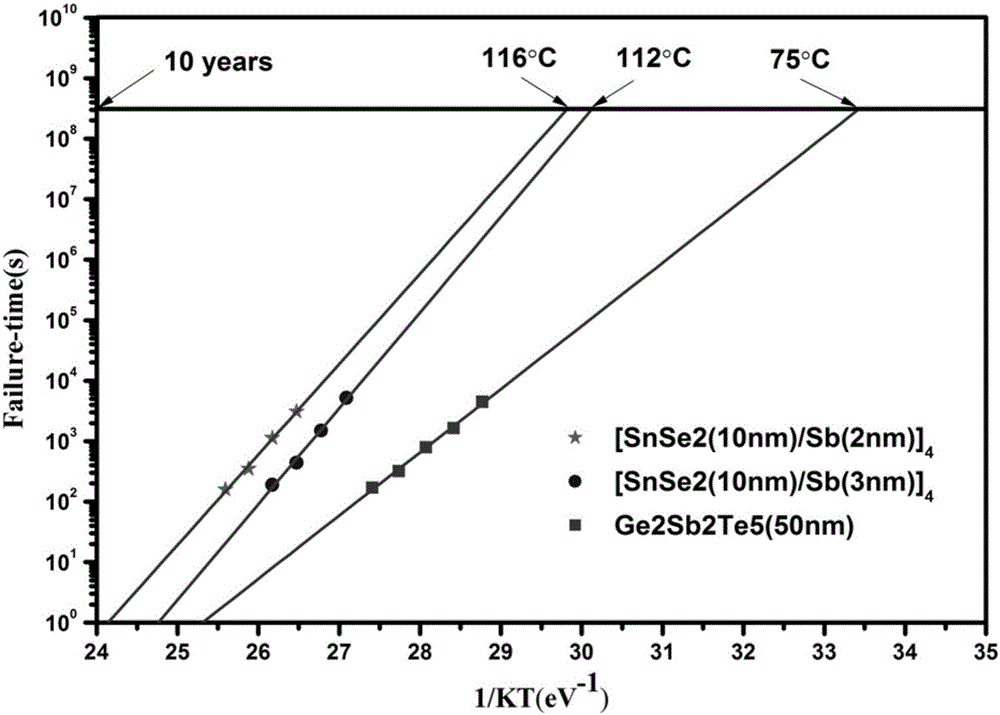

Class superlattice tin-selenium/antimony nanometer phase transition film, and preparation and application thereof

InactiveCN105762277AImprove thermal stabilityFast phase changeElectrical apparatusHeat stabilityTotal thickness

The invention relates to a class superlattice tin-selenium / antimony nanometer phase transition film, comprising a SnSe2 material and a simple substance Sb material which are alternatively superposed to form a class superlattice structure. The structure general formula of the phase transition film is [SnSe2(a) / Sb(b)]x; the total thickness of the class superlattice phase transition film is 40-60 nm, wherein a is the thickness of the SnSe2 material in each layer of phase transition film, and is in the range of 8-12 nm; b is the thickness of the simple substance Sb material in each layer of phase transition film, and is in the range of 1.5-3 nm; x is the periodicity of the class superlattice phase transition film structure, and is 4 or 5. The phase transition film is obtained through a magnetron sputtering mode, and is applied to a PCRAM device. Compared with the prior art, the phase transition film has the advantages of great heat stability, fast phase transition speed, small volume change, low power consumption and excellent comprehensive performance.

Owner:TONGJI UNIV

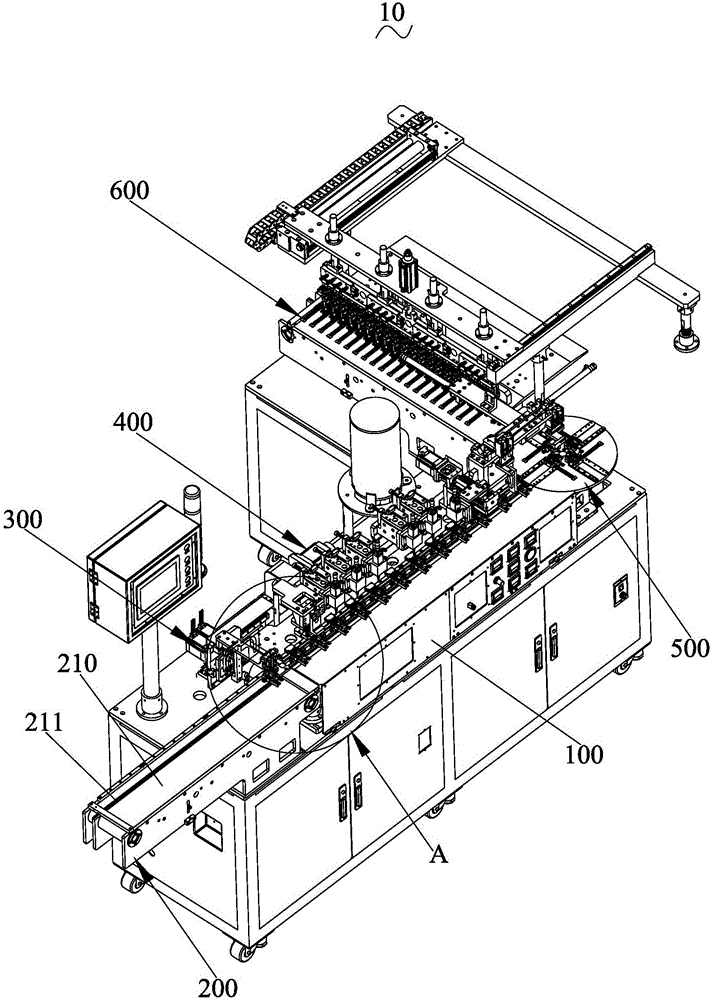

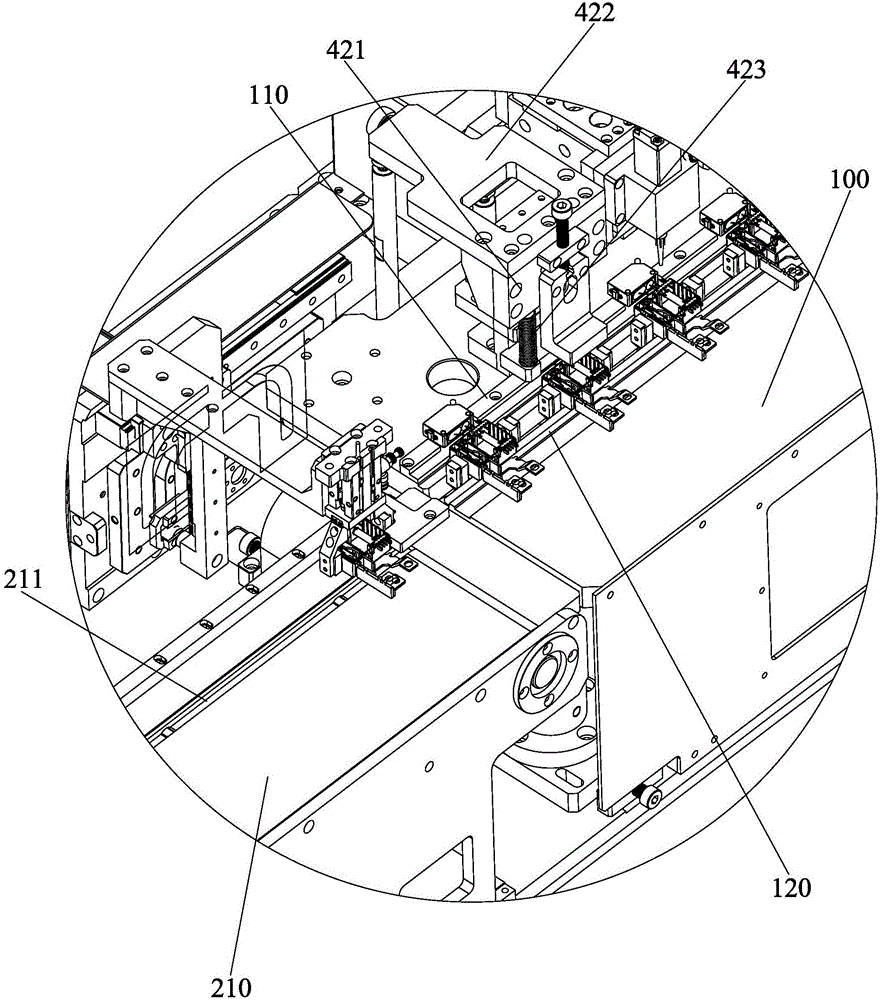

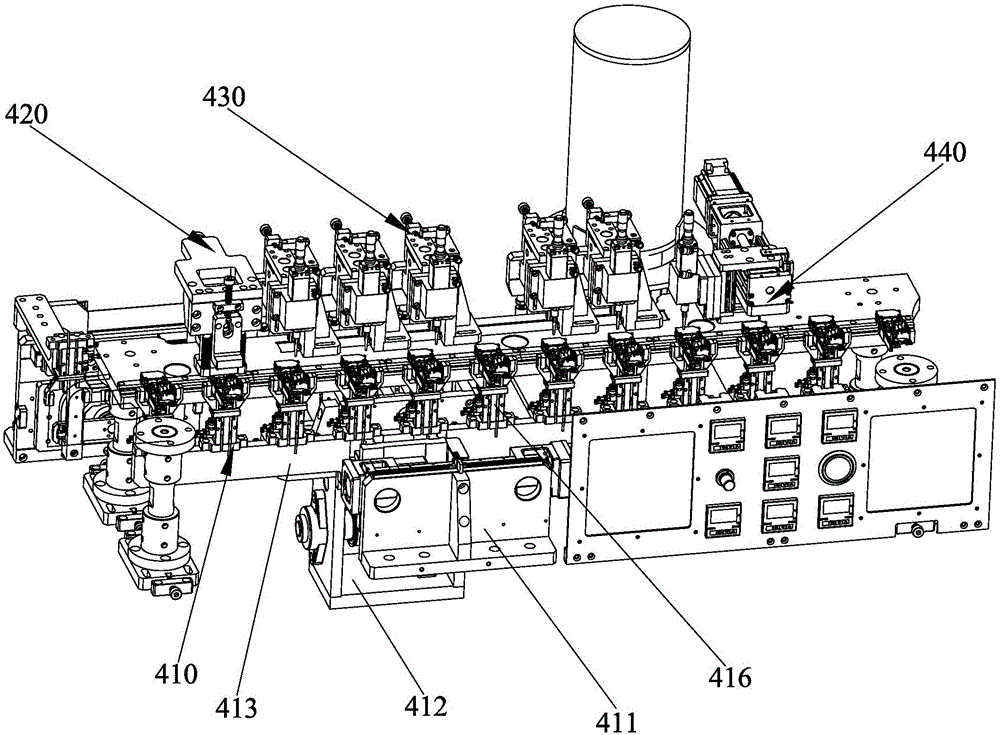

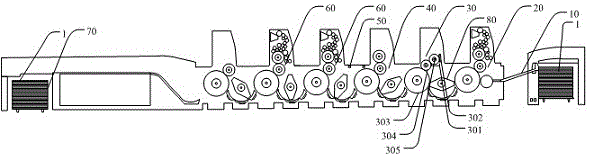

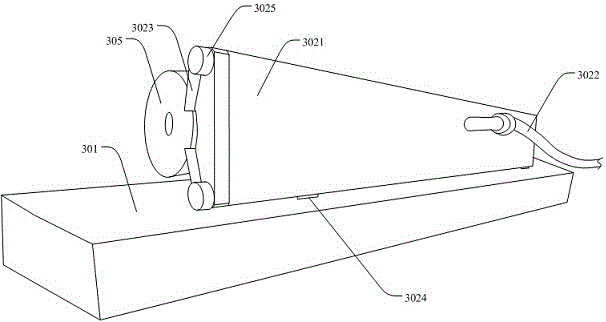

Relay glue dispenser

InactiveCN106311560AIncrease productivityImprove reliabilityLiquid surface applicatorsCoatingsEngineeringCam

The invention discloses a relay glue dispenser. The relay glue dispenser comprises a working base station, a relay conveying device, a relay feeding device, a relay glue dispensing device, a relay steering device and a relay discharging device, wherein the relay conveying device, the relay feeding device, the relay glue dispensing device, the relay steering device and the relay discharging device are sequentially arranged on the working base station. By arranging the relay conveying device, the relay feeding device, the relay glue dispensing device, the relay steering device and the relay discharging device, automatic glue dispensing processing of relays is achieved, and the processing quality is guaranteed while the production efficiency is improved. According to the relay glue dispenser, by adoption of a cam-link transmission structure, synchronous movement for multi-station glue dispensing is achieved, and the production efficiency is greatly improved. In addition, the number of components constituting the cam-link mechanism is small, the structure is simple, and various expected movement rules can be achieved for driven components only by reasonably designing the contour curve of a cam; and design is easy, high-speed operation can be achieved, the structure is compact, the reliability is high, and thus the relay glue dispenser is higher in creativeness.

Owner:HUIZHOU JINYUAN PRECISION AUTOMATION EQUIP

High speed dynamic frequency divider

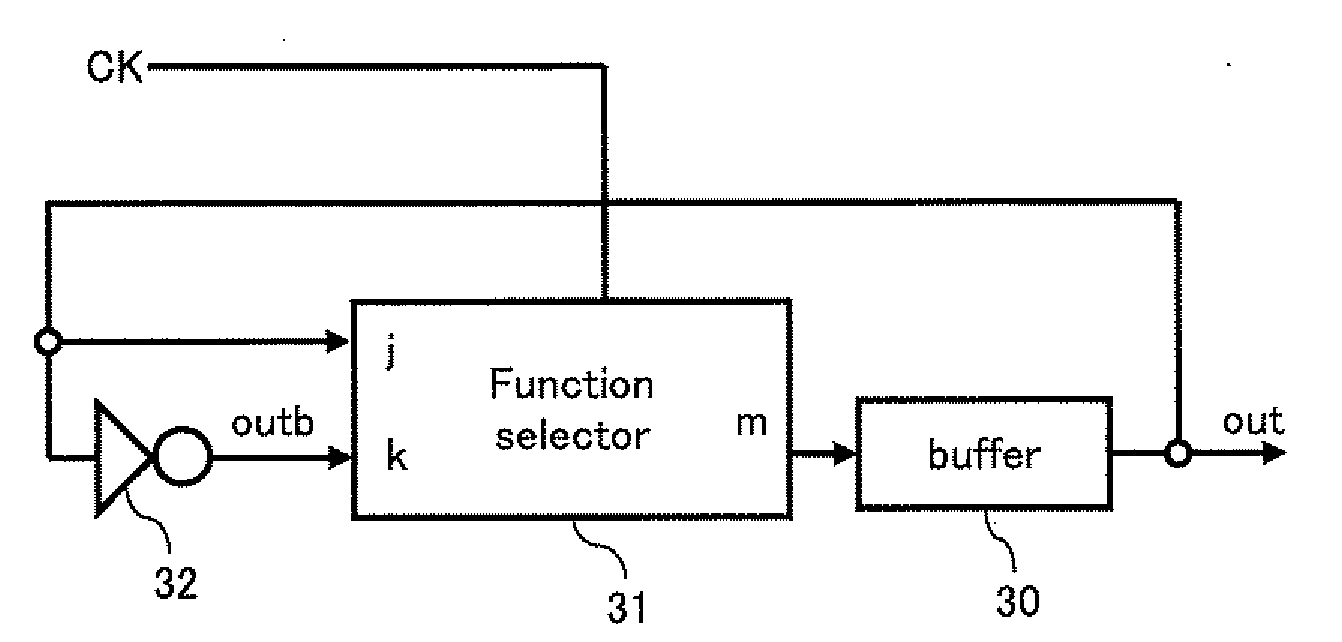

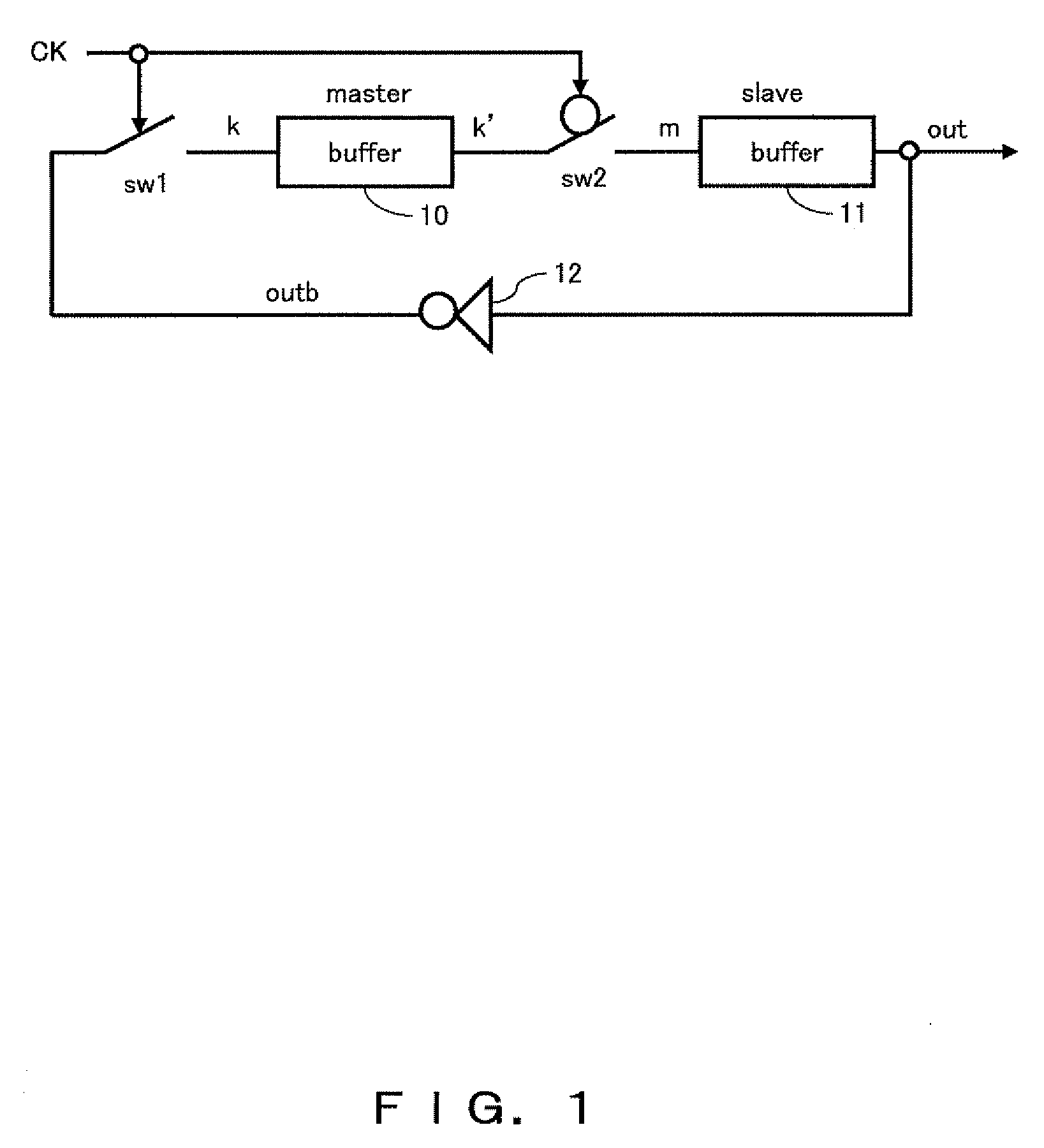

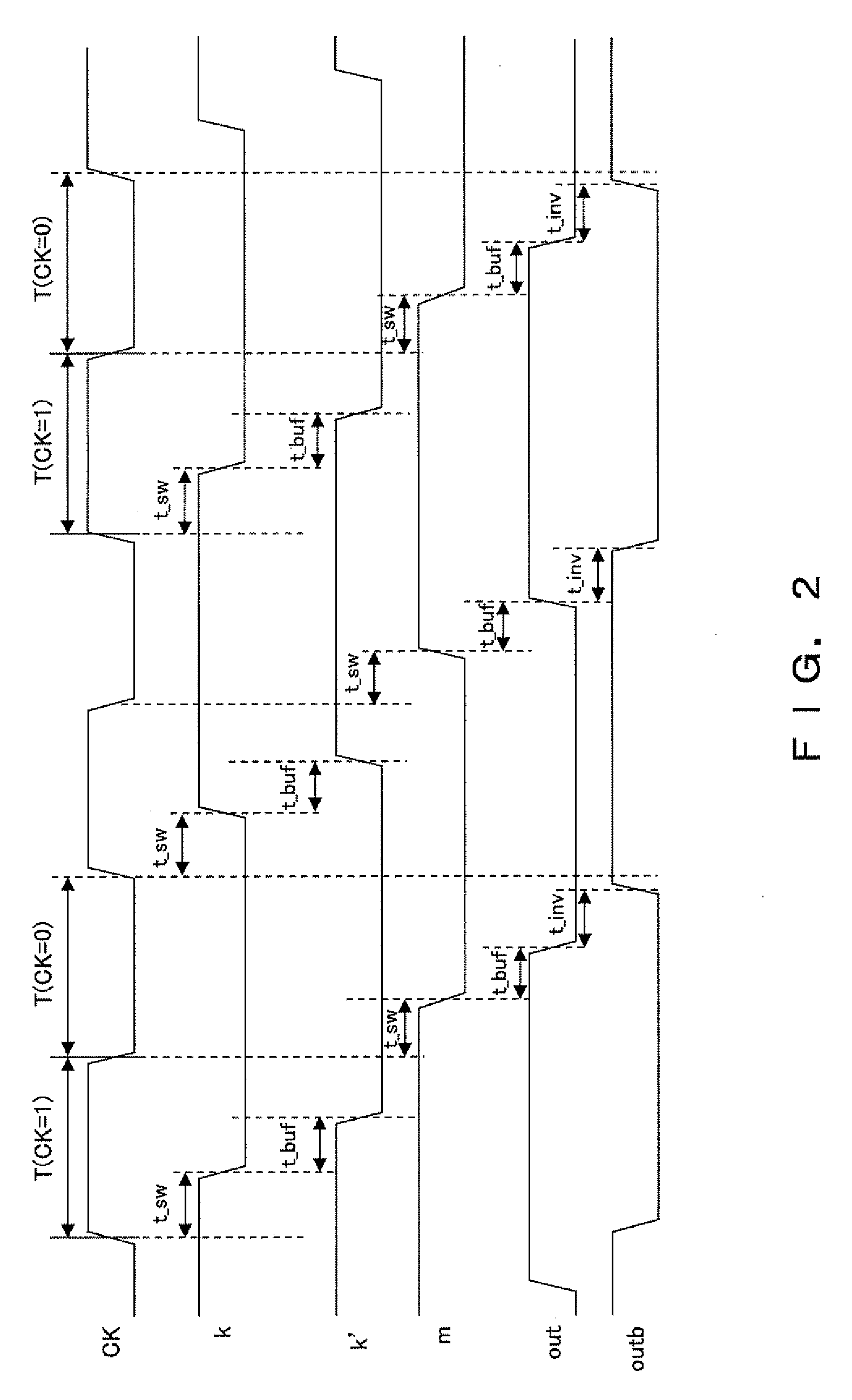

InactiveUS20070257714A1High speed operationApplicability in cmos configurationContinuously circulated pulse countersCounting chain synchronous pulse countersEmbedded systemFeature selector

The frequency divider includes the buffer 30, the function selector 31 and the inverter 32. The output of the function selector 31 is input to the buffer 30. The output of the buffer 30 is fed back to the function selector 31 by two paths. One path includes the inverter 32 and the other does not. The function selector 31 selects one of the paths in synchronous with input clock CK. At one timing the output of the buffer 30 is flipped by the inverter 32. At the next timing the output of the buffer 30 is held the same by the function selector 31 selecting the path not including the inverter 32.

Owner:FUJITSU LTD

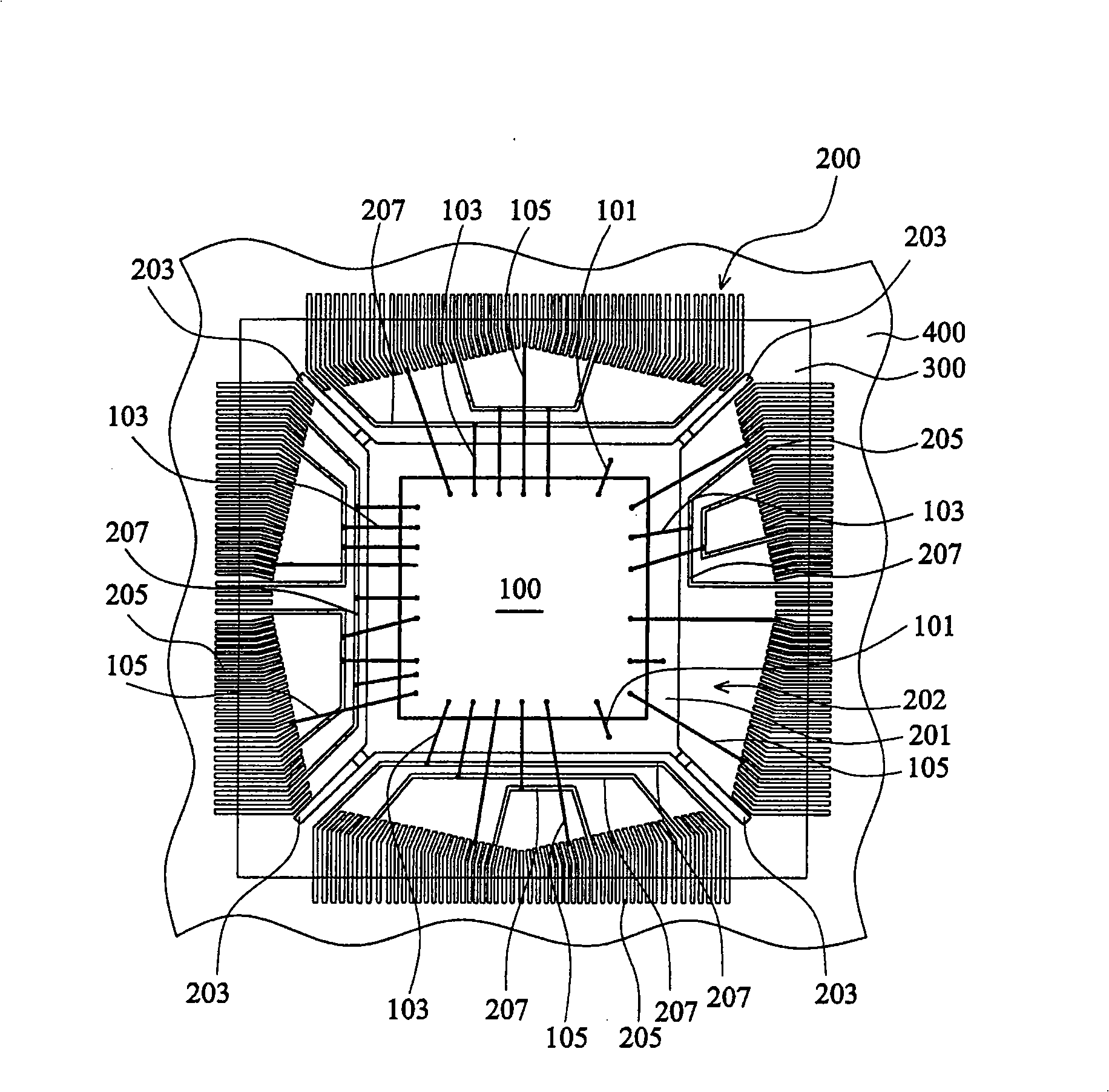

Electronic package an electronic device

ActiveCN101350318AReduce inductanceLower the resistance valueSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceElectric power system

The invention discloses an electronic package and an electronic device. The electronic package comprises a die pad, a die, a plurality of leads, a common electrode bar layer, and a molding compound. The die is attached onto the pad. The plurality of leads surrounds the die pad and spaced therefrom to define a ring gap therebetween. The common electrode bar layer is in the ring gap and substantially coplanar to the die pad, in which at least one of the plurality of leads extends to the common electrode bar layer. The molding compound partially encapsulates the die pad and the common electrode bar layer, such that the bottom surfaces of the die pad and the common electrode bar layerare exposed. The invention is capable of reducing inductance and resistance of the circuit, obtaining greater integrity of electric power, improving IR drop problem of the core electric power, and is helpful to high-speed operation and device performance improvement.

Owner:MEDIATEK INC

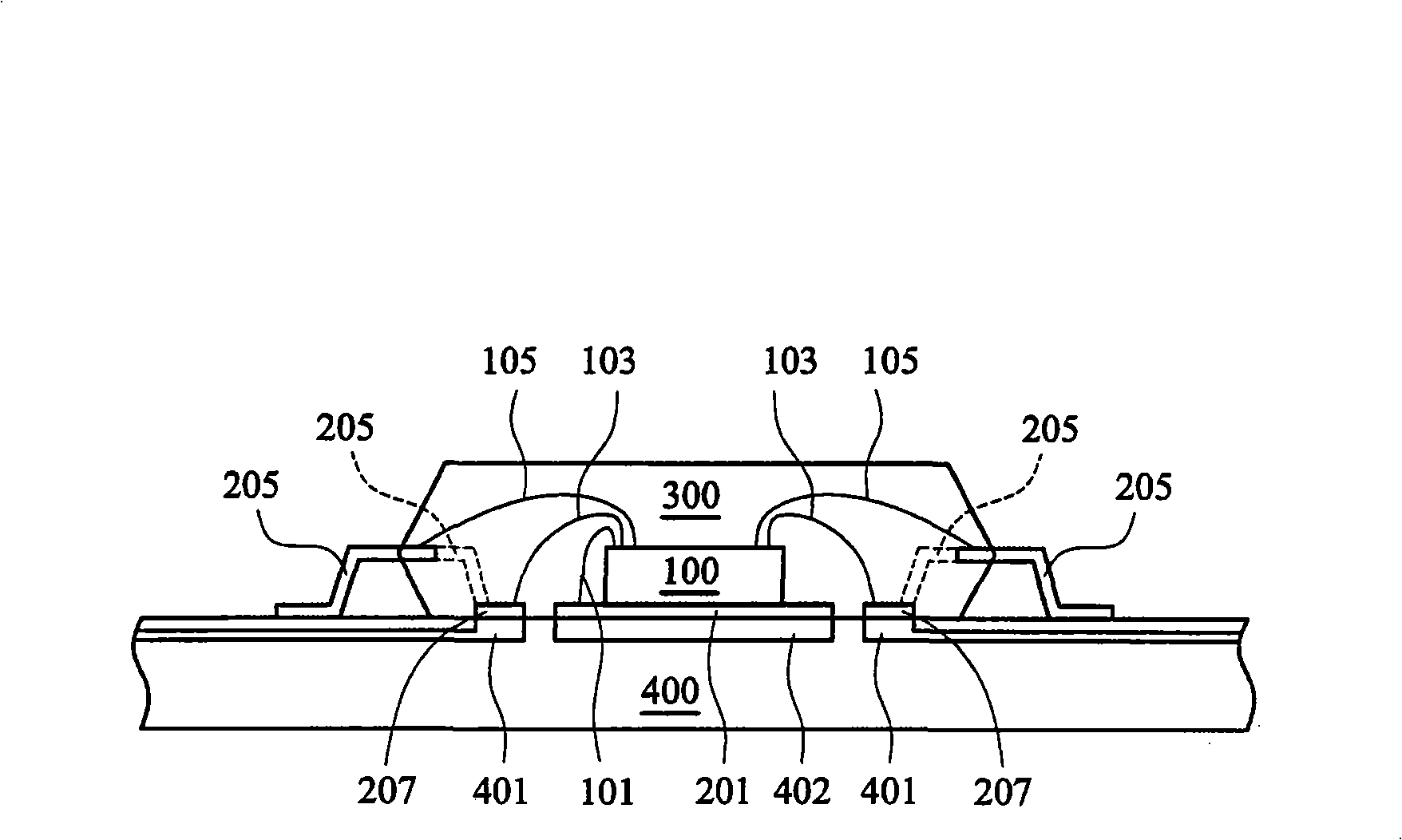

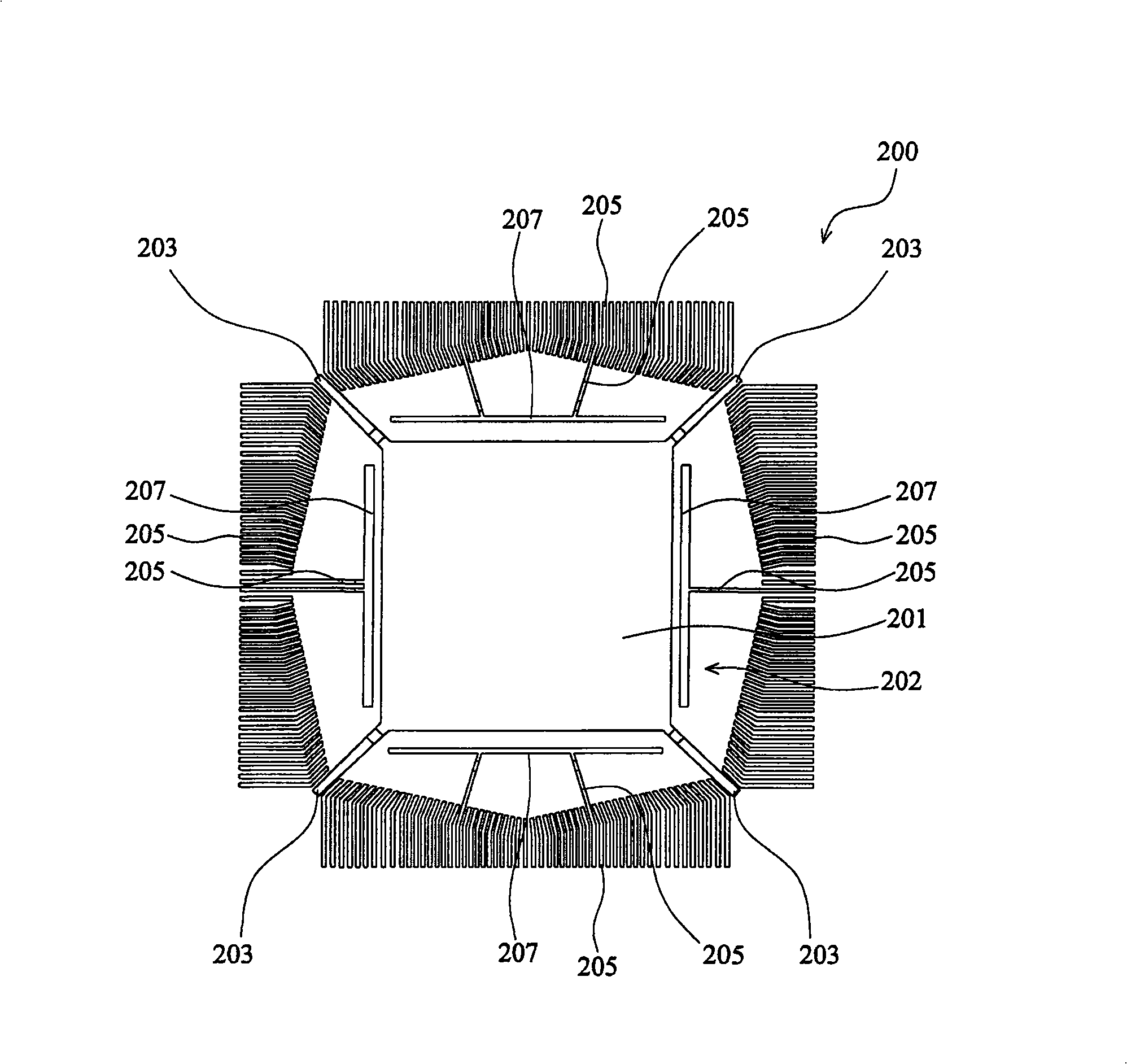

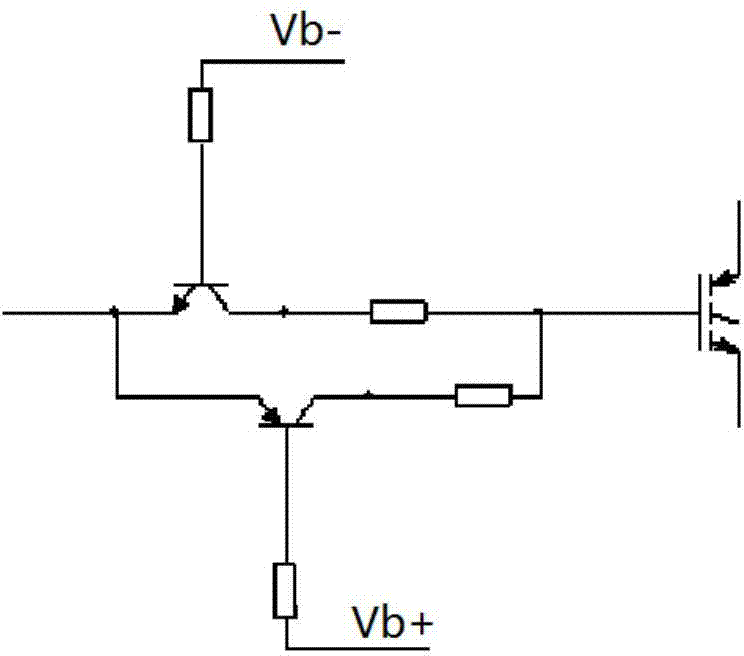

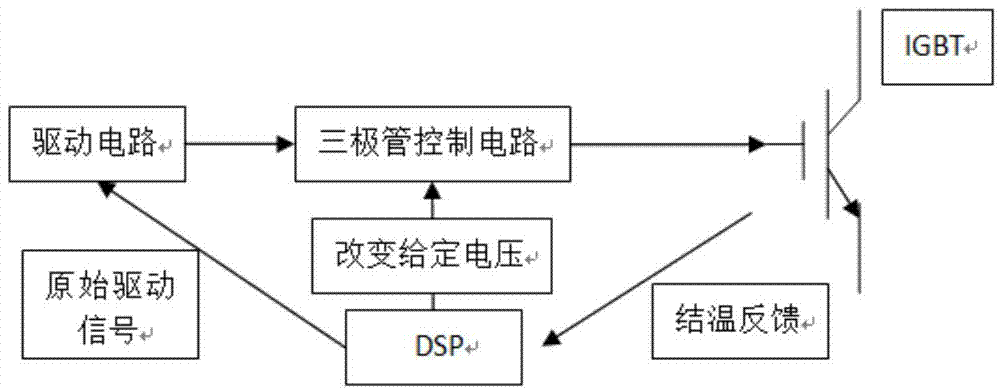

Power module heat management device and method based on self-adaptive adjustment of driving circuit

ActiveCN104765300AImprove dynamic performanceAvoid shockProgramme controlComputer controlTime delaysPeak current

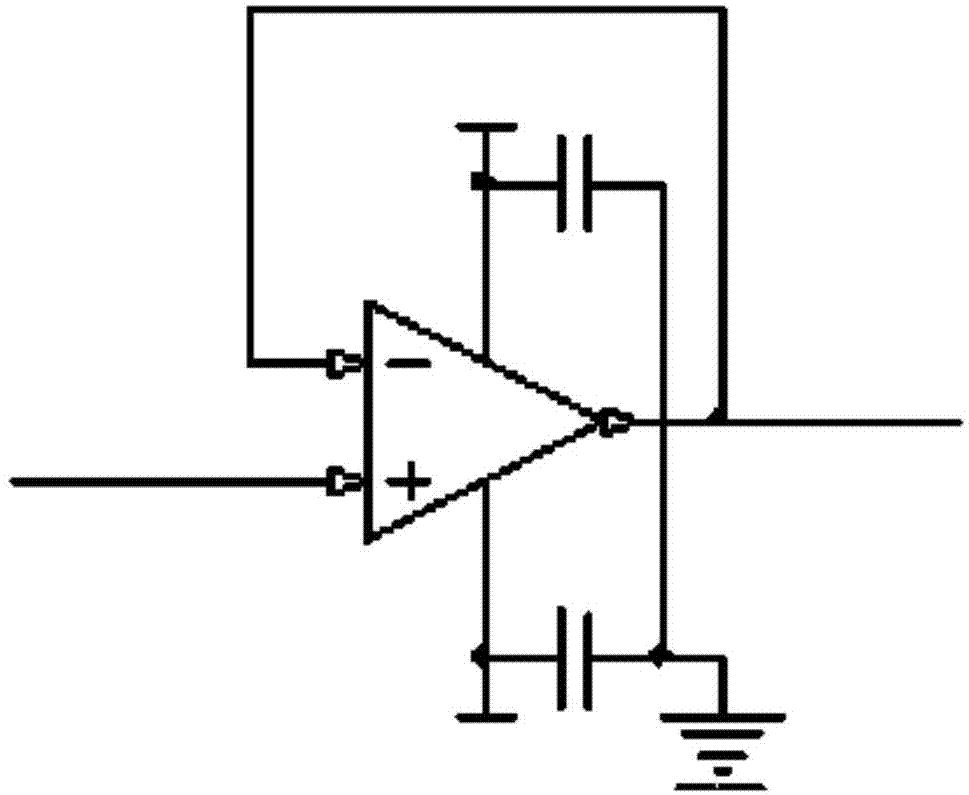

The invention discloses a power module heat management device based on self-adaptive adjustment of a driving circuit. The power module heat management device based on the self-adaptive adjustment of the driving circuit comprises a DSP analog voltage output circuit arranged between the driving circuit and an IGBT grid, and an IGBT grid charging and discharging control loop, wherein the IGBT grid charging and discharging control loop is used for providing a charging and discharging loop for a stray capacitor of the IGBT grid, and the DSP analog voltage output circuit is used for generating the control voltage of the IGBT grid charging and discharging control loop. According to the power module heat management device based on the self-adaptive adjustment of the driving circuit, the base current of the IGBT grid charging and discharging control loop is adjusted by adjusting the output analog voltage of the DSP analog voltage output circuit, then the collector current of a triode is adjusted, and namely, the grid peak current of an IGBT is adjusted. According to the power module heat management device, the circuit is simple, and the problems of circuit impact and time delay which are caused by driving voltage switching are solved; an extra driving circuit is not needed by adjusting the given voltage of the triode in a control circuit.

Owner:CHONGQING UNIV

Semiconductor integrated circuit device

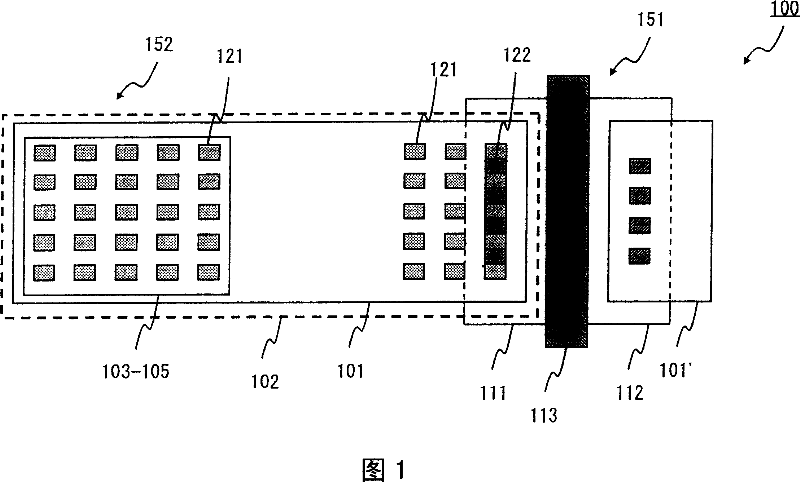

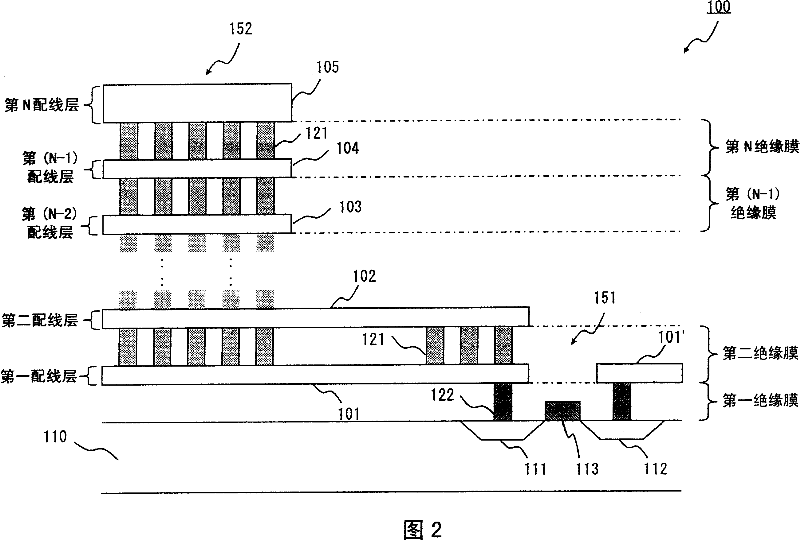

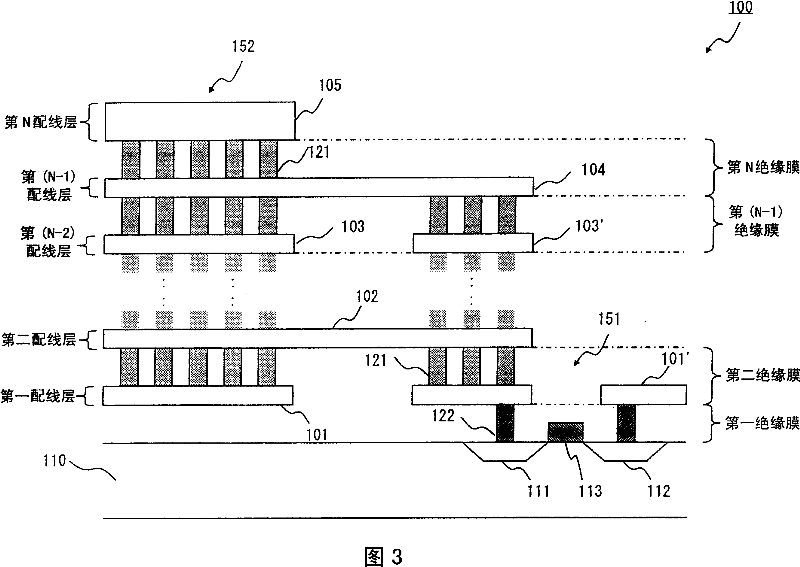

InactiveCN101038913AHigh speed operationImproved ESD withstand voltageTransistorSemiconductor/solid-state device detailsSemiconductorMetal

A semiconductor integrated circuit device according to an embodiment of the invention includes: a protective element formed on a semiconductor substrate; and a plurality of wiring layers composed of insulating layers including a layer that is a low dielectric-constant film, and metal lines, in which a metal line in a second wiring layer and a metal line in a first wiring layer among the plurality of wiring layers extend from the other region above the semiconductor substrate to a region electrically connected with the protective element.

Owner:NEC ELECTRONICS CORP

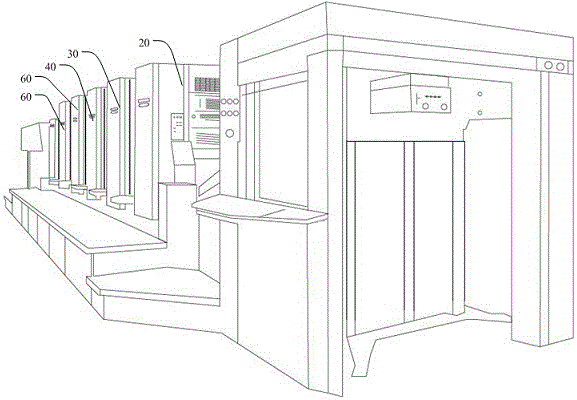

Combined printing device and printing method

InactiveCN106113925AUniform and thick printingFine and clear printingOther printing apparatusRotary letterpress machinesPrinting inkPulp and paper industry

The invention discloses a combined printing device and a printing method. The printing method comprises the steps that a paper conveying mechanism conveys paper to a first offset printing mechanism; the first offset printing mechanism prints paper through an offset printing technology, and the paper is conveyed to a flexible printing mechanism; the flexible printing mechanism prints the paper through a flexible printing technology, and the paper is conveyed to second offset printing mechanisms; a drying mechanism dries flexible printing ink in the paper conveying process; a plurality of second offset printing mechanisms sequentially print the paper through the offset printing technology; a paper collection mechanism carries out collection and stacking on the printed paper. Flexography color groups are combined on an offset printing machine, on the premise of meeting rapid printing, lines, characters and lattice points on single paper are clear, patterns on a printing undertint on-site area on the single paper are uniform and thick, high-speed stable printing is achieved, operation is carried out only according to the working procedure of an offset printing device, and the operation requirement is low.

Owner:SHENZHEN JINJIA GRP

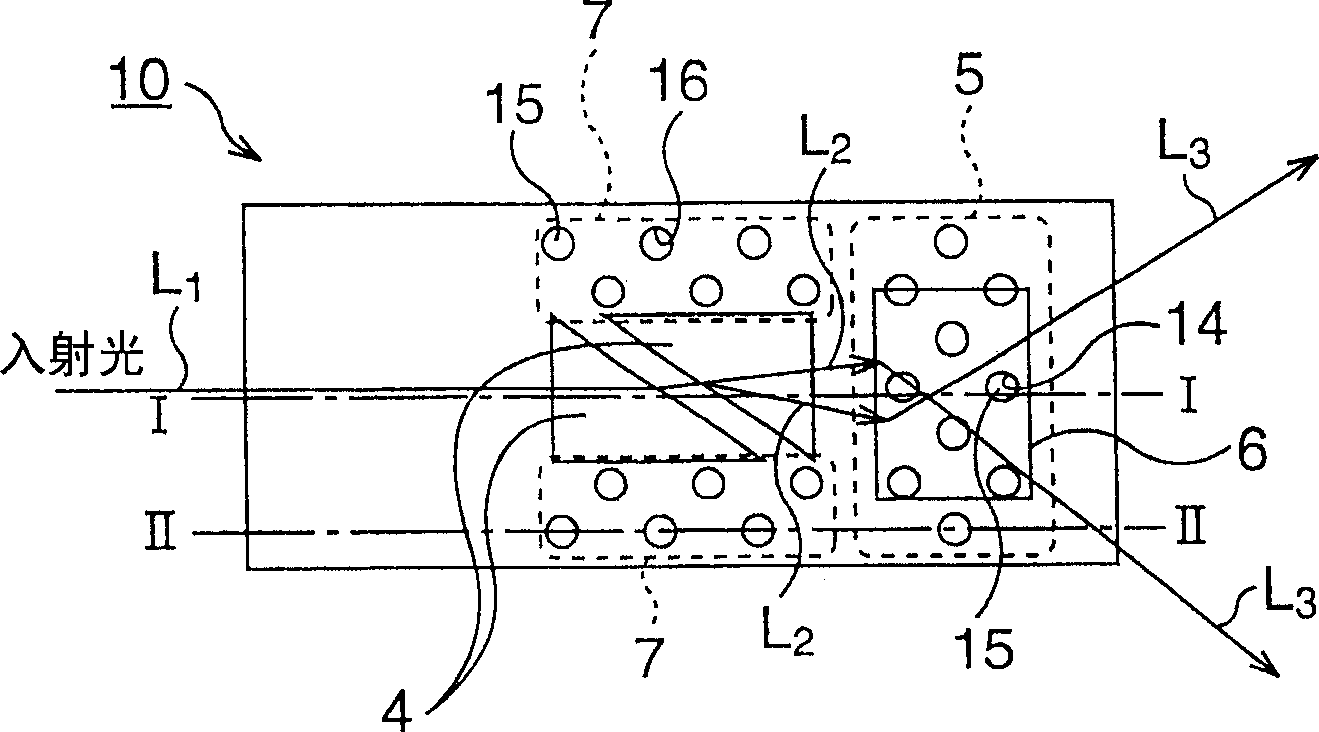

Optical deflection element and optical switch

InactiveCN1766683APrecise and high-speed controlSize reduction and integrationNanoopticsOptical waveguide light guideOptical propagationPhotonic crystal structure

A light deflection element is shaped to include: a prism electrode disposed on an optical waveguide; a first photonic crystal structure disposed in front of the prism electrode in a light propagation direction and at a position after light passes through the prism electrode; a control electrode via The optical waveguide on the first photonic crystal structure is arranged facing the opposite electrode layer; and the second photonic crystal structure is arranged on the side of the prism electrode parallel to the light propagation direction.

Owner:FUJITSU LTD

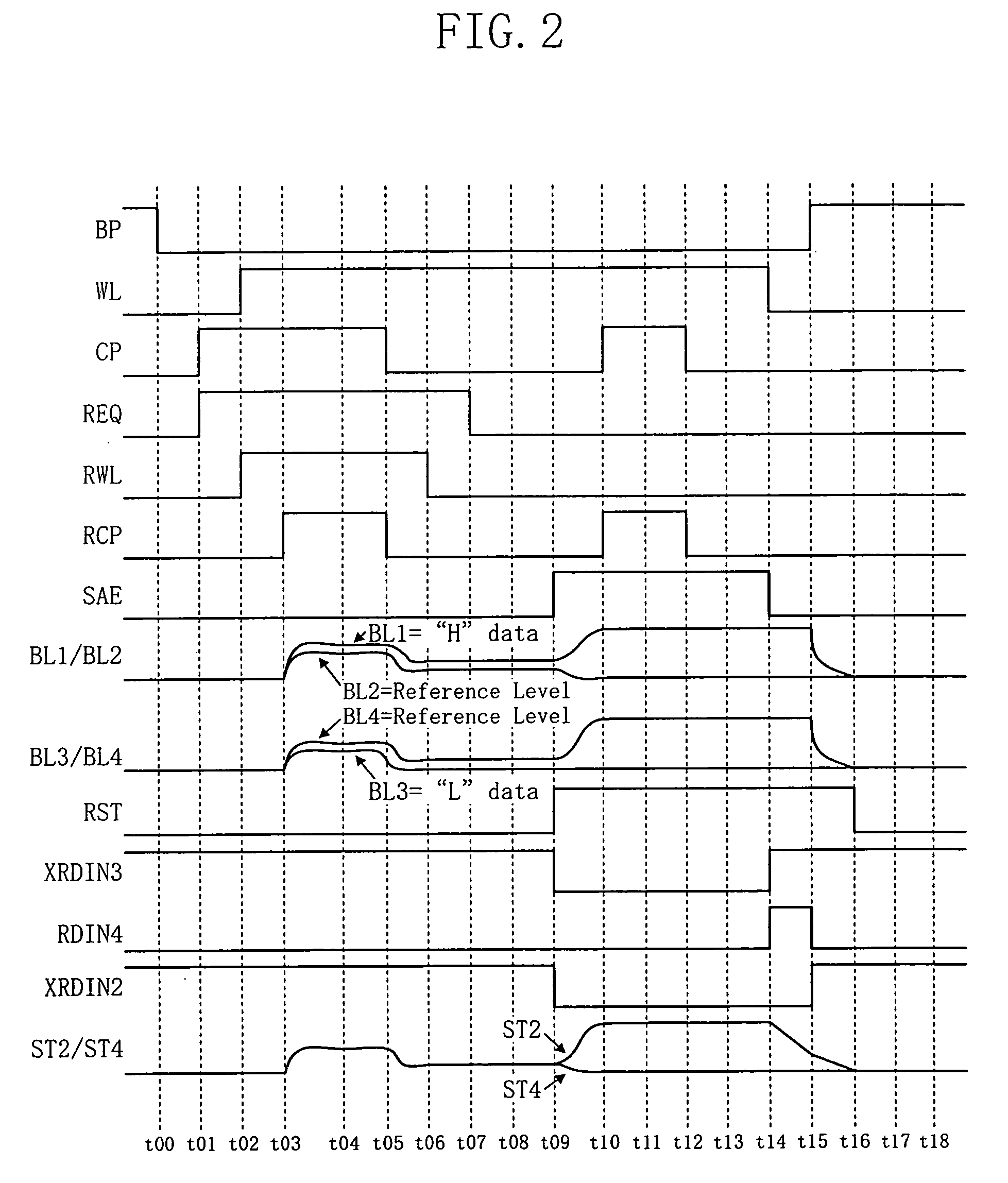

Ferroelectric memory and method for reading data from the ferroelectric memory

InactiveUS20050259461A1Improve reliabilityHigh speed operationSolid-state devicesDigital storageFerroelectric capacitorElectrical and Electronics engineering

A ferroelectric memory of the present invention comprises: a plurality of normal cells, each of which includes a first ferroelectric capacitor for holding data and a first transistor connected to a first electrode of the first ferroelectric capacitor; a first bit line connected to the first transistor; a first bit line precharge circuit which is a switch circuit provided between the first bit line and a ground; and a word line connected to a gate of the first transistor. The word line is deactivated to disconnect the first ferroelectric capacitor from the first bit line before the first bit line precharge circuit is driven to discharge a potential of the first bit line.

Owner:PANASONIC CORP

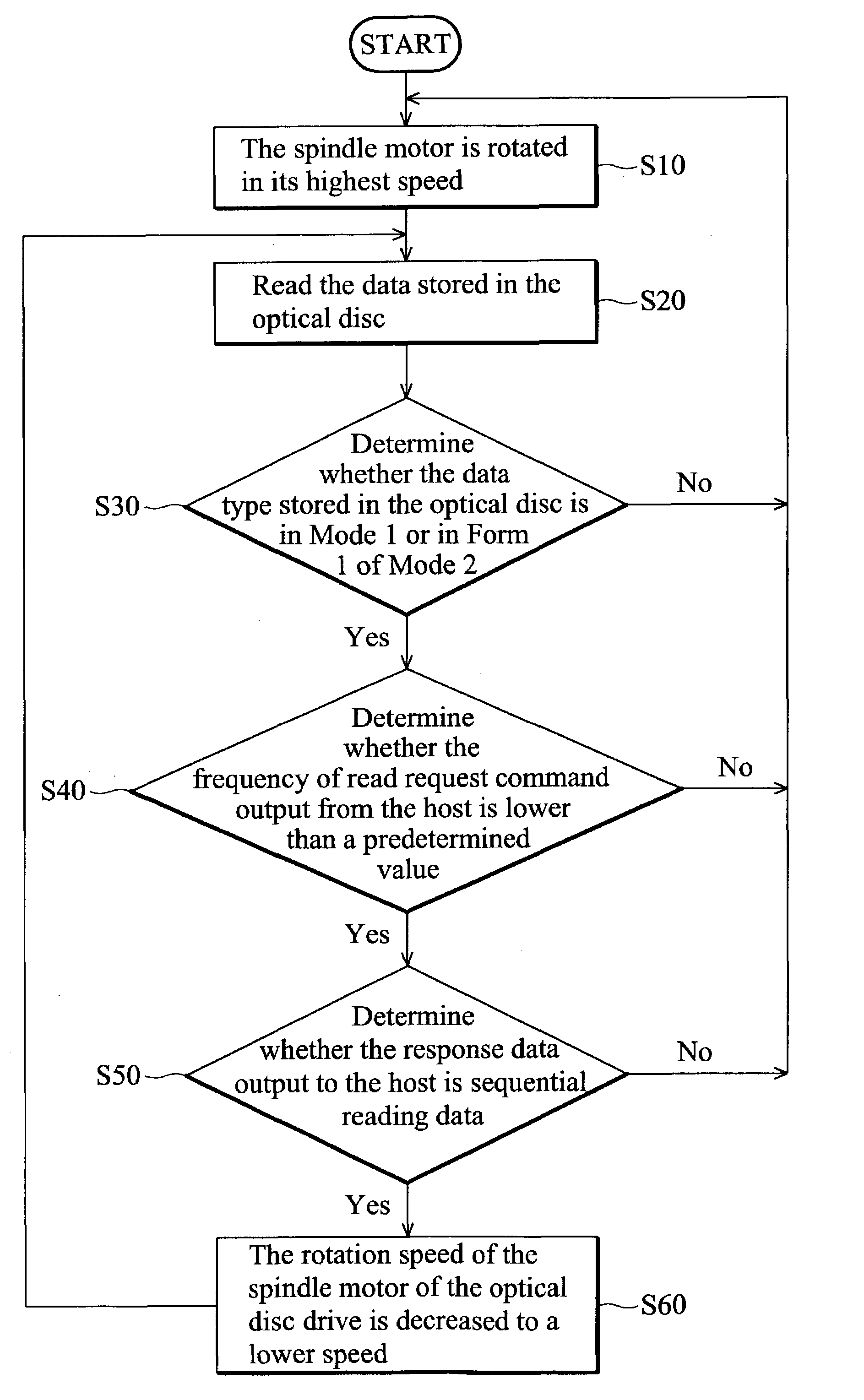

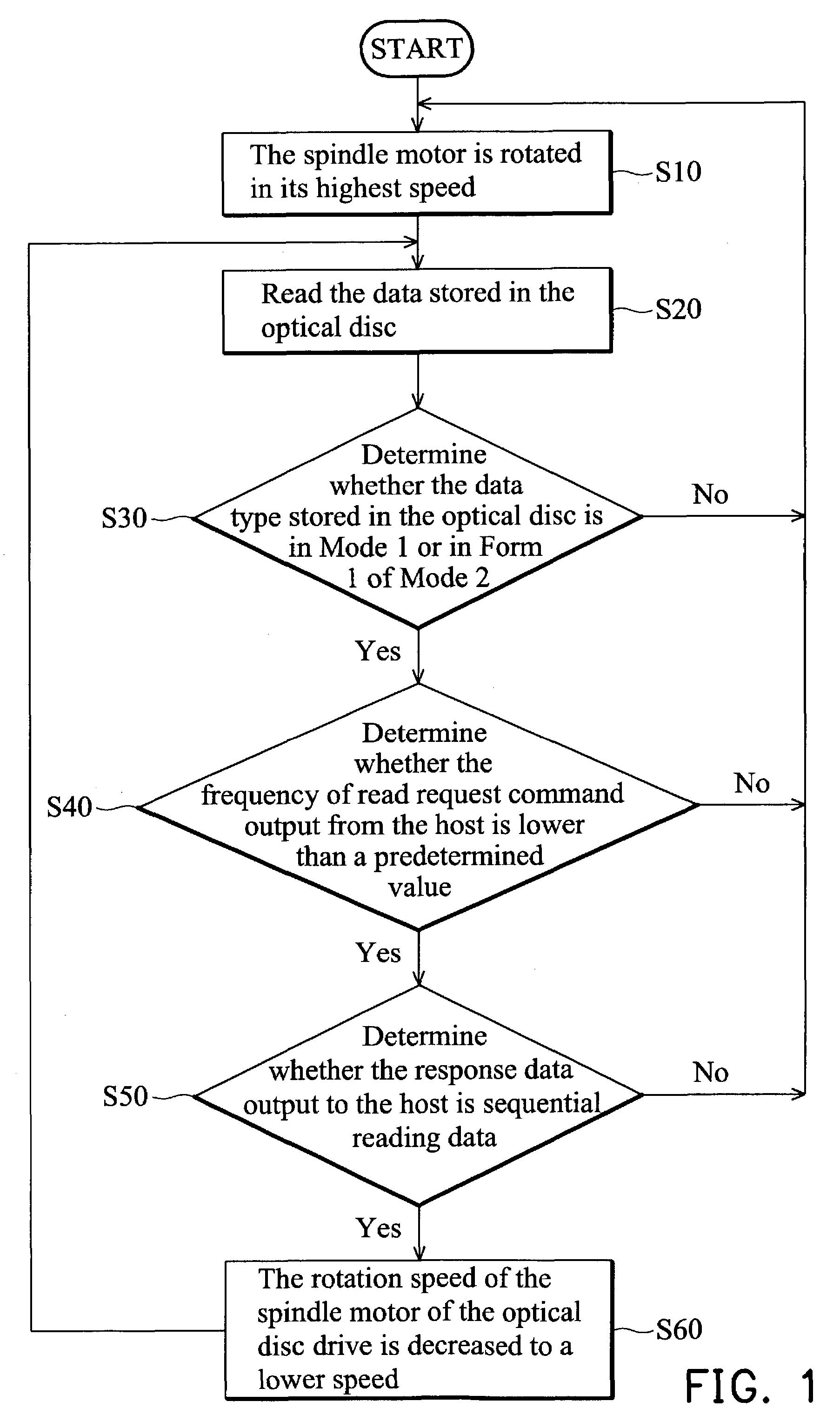

Method of adjusting rotation speed of optical disc drive

InactiveUS6977878B2Poor read performanceHigh speed operationFilamentary/web record carriersRecord information storageData transmissionOptical disc drive

The present invention discloses a method of adjusting a rotation speed of an optical disc drive for a spindle motor controlled by a host to rotate and read an optical disc. First, it is determined whether the data read by the optical disc drive is in Mode 1 or Form 1 of Mode 2. If in Mode 1 or Form 1 of Mode 2, it is determined whether the frequency of read request commands output from the host is lower than a predetermined value or not. If the frequency of read request commands output from the host is lower than the predetermined value, then it is determined whether the response data output to the host is sequential reading data or not. If the three situations mentioned above are all sustained, the data read by the optical disc drive is ascertained as MP3 data. Thus, the rotation speed of the spindle motor is decreased to a lower value. If one of the three situations is not sustained, the optical disc drive rotates at its highest speed to enhance the quantity of data read between the optical disc drive and the host. Thus, the rotation speed of the optical disc drive is adjusted automatically in response to the data transmission rate.

Owner:LITE ON IT

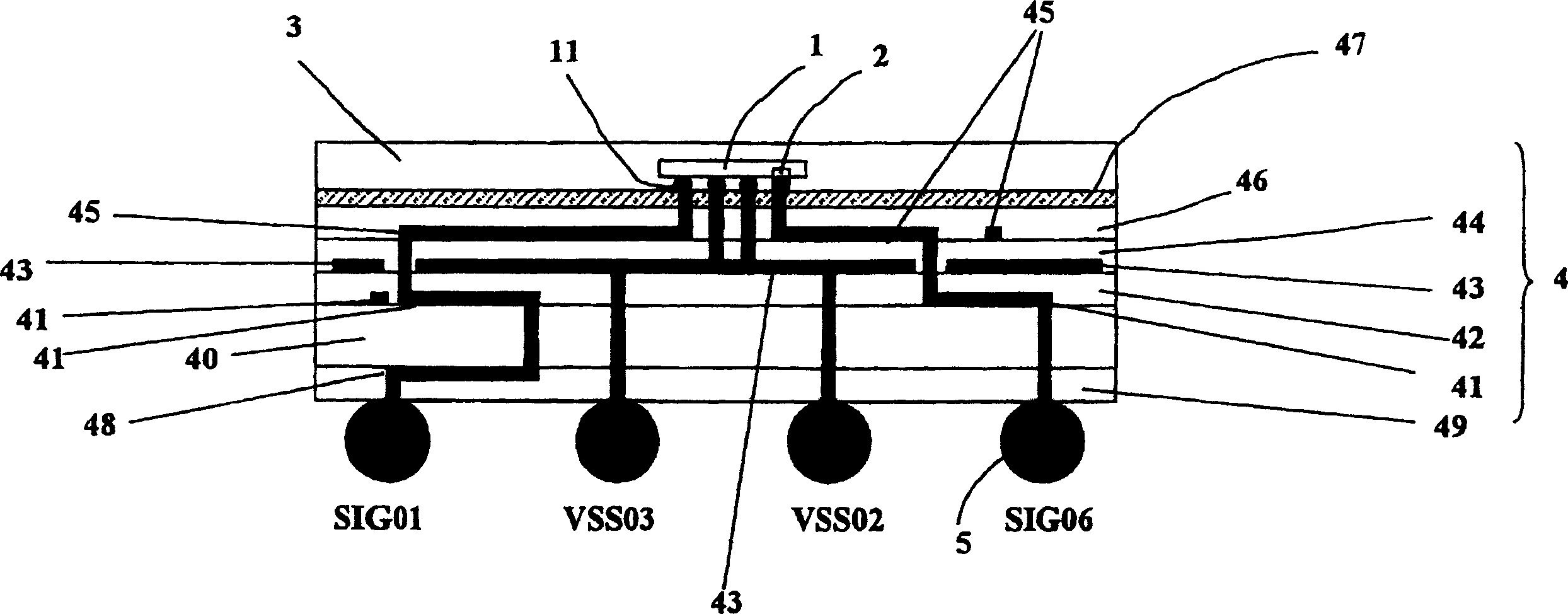

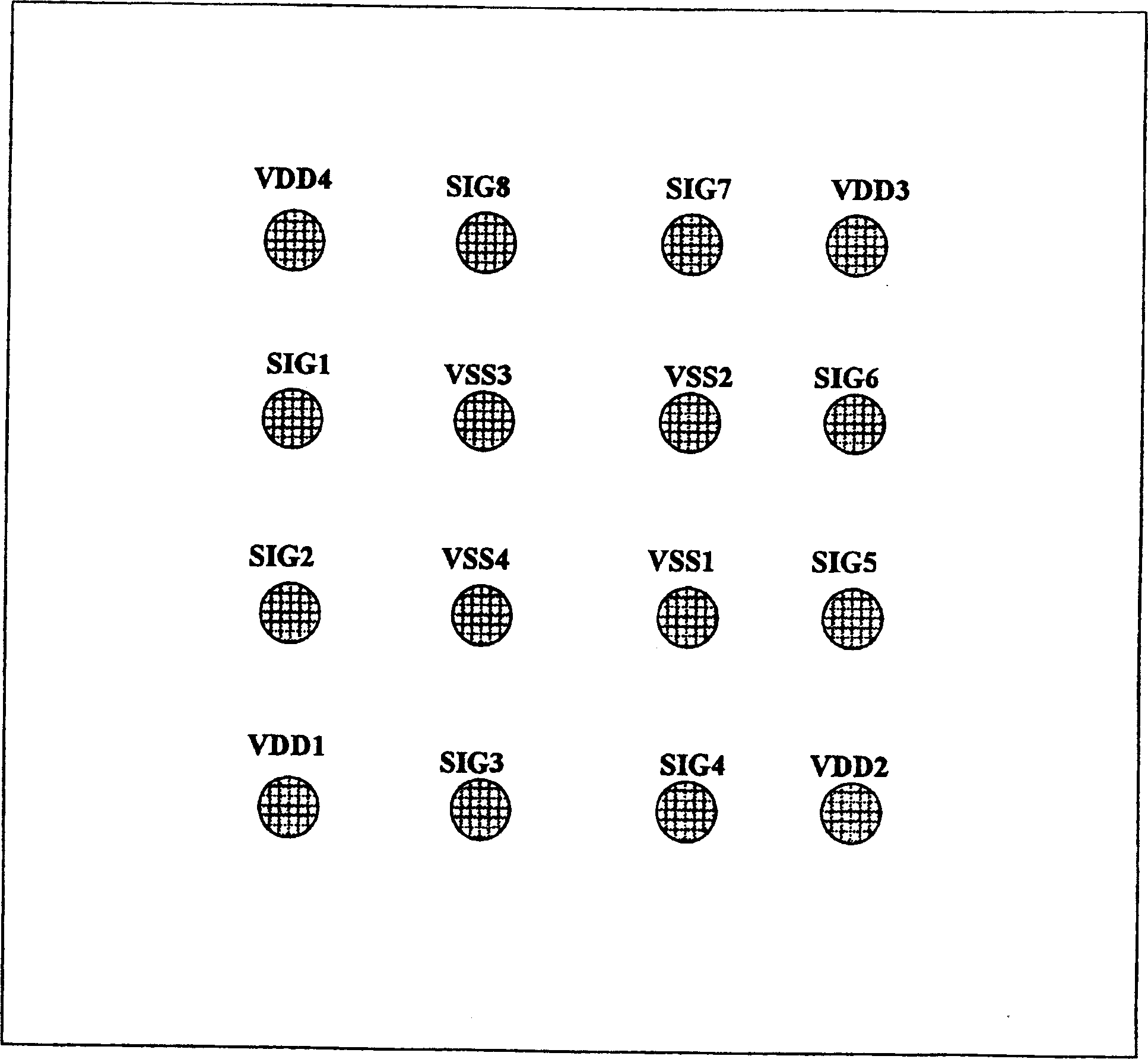

Semiconductor integrated circuit device

InactiveCN1638128AHigh speed operationIncrease freedomSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor integrated circuit device includes: a semiconductor integrated circuit chip installed on a semiconductor substrate, the semiconductor integrated circuit chip is equipped with a plurality of circuit systems, the plurality of circuit systems are separated and driven by different power supply systems, the semiconductor integrated circuit The chip also includes at least one electrostatic protection circuit; and an external connection terminal (5), which is connected to the circuit system of the semiconductor integrated circuit chip through a wiring member (4) having at least one wiring layer, wherein, through the electrostatic protection circuit (2) Power supply lines and ground lines of a plurality of circuit systems of the semiconductor integrated circuit chip (1) are respectively commonly connected to conductive planes (43) provided in the wiring member.

Owner:PANASONIC CORP

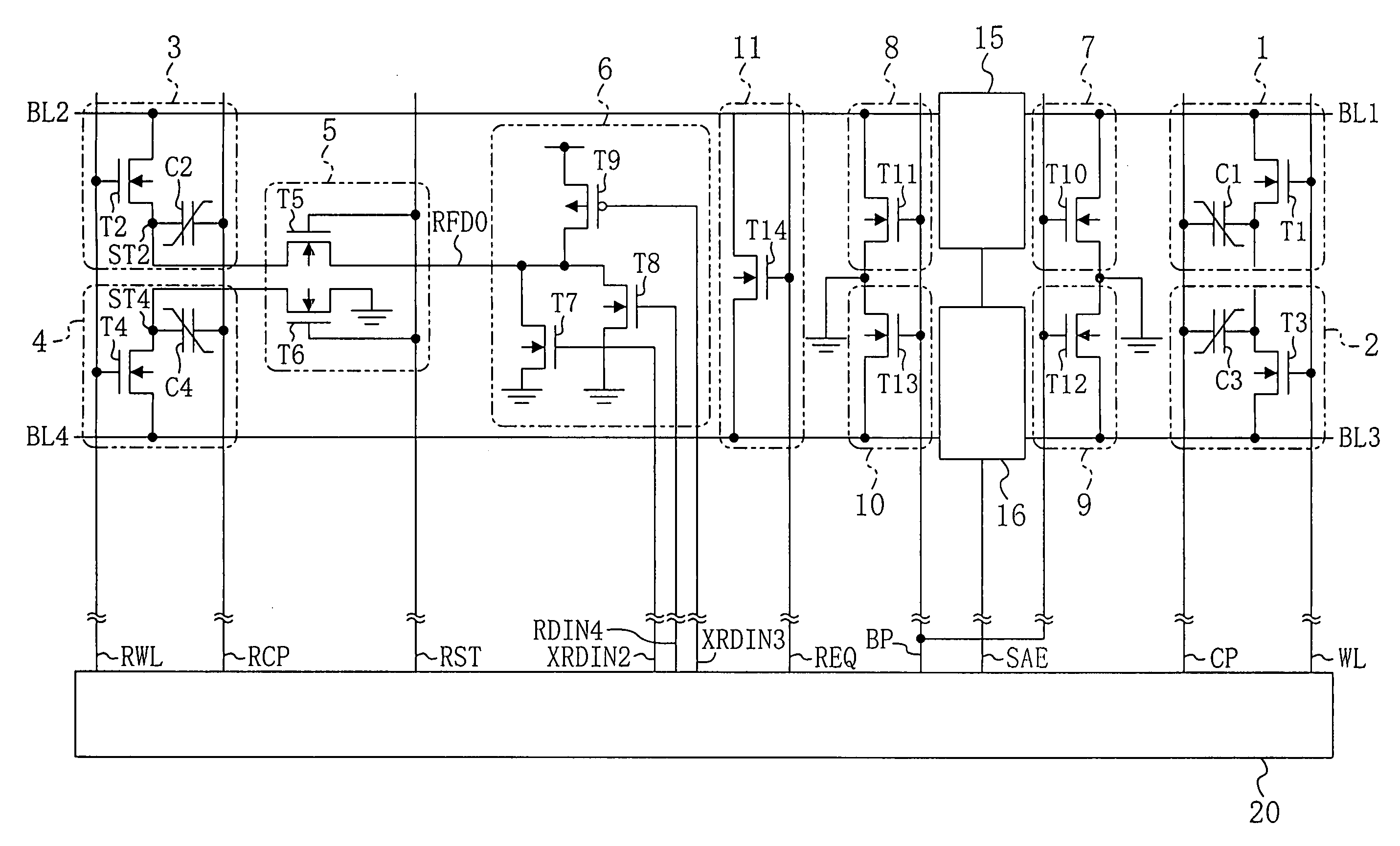

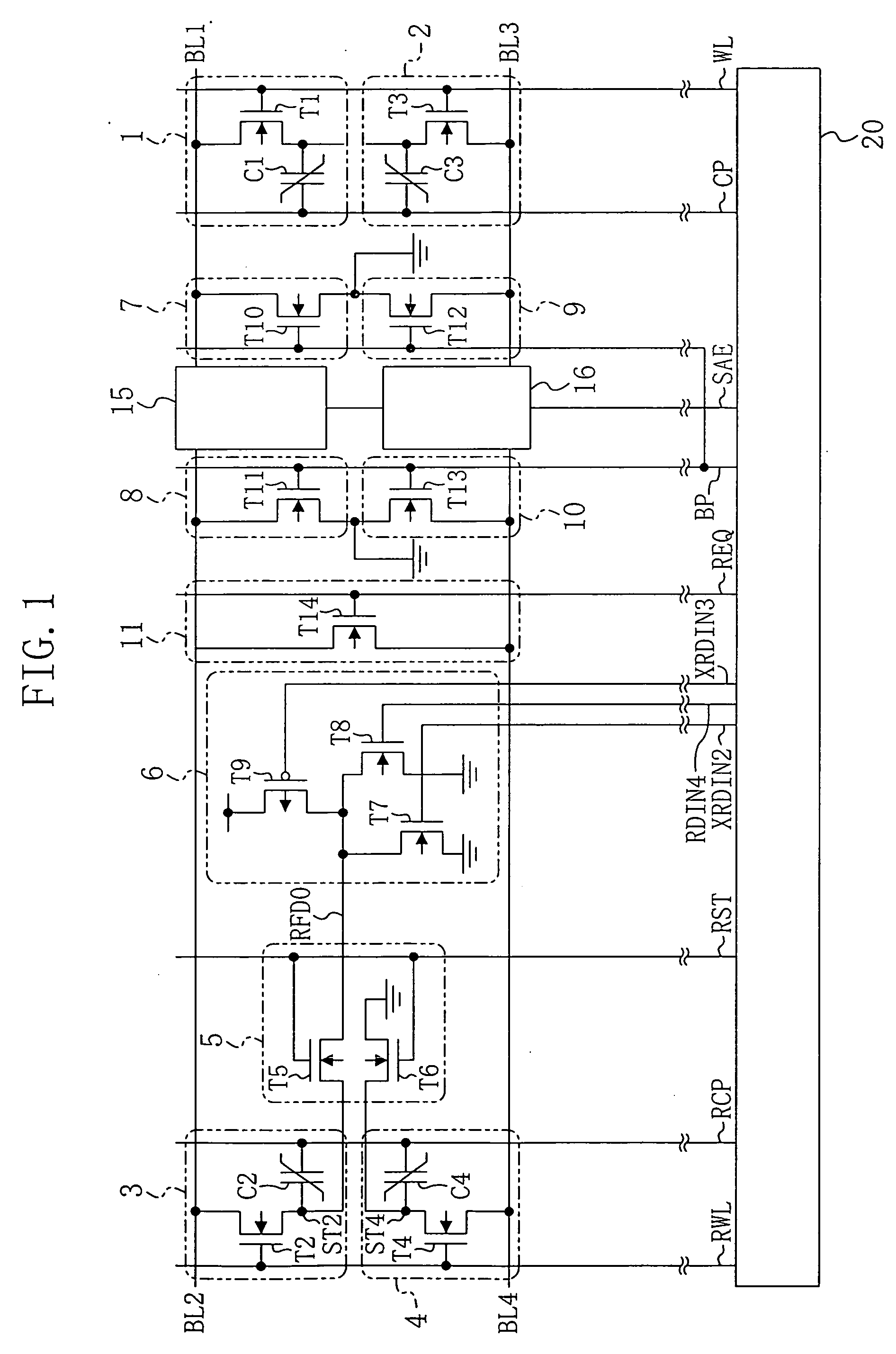

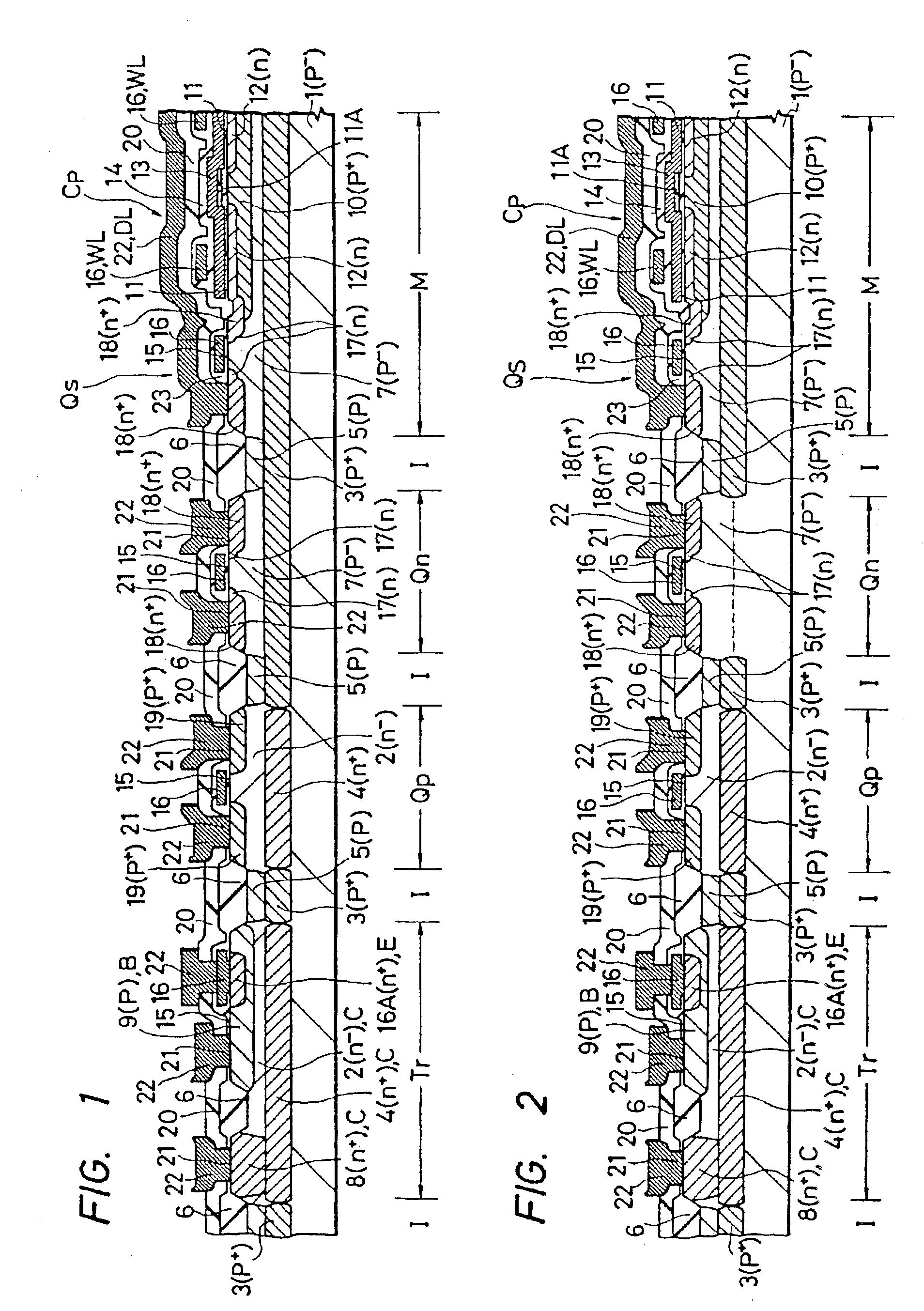

Semiconductor memory device

InactiveUS6864559B2High integration densityHigh speed operationTransistorSolid-state devicesEngineeringVoltage

Disclosed is a semiconductor device, such as a semiconductor memory device, having structure wherein invasion of minority carriers from the semiconductor substrate into components of the device, formed on the substrate, can be avoided. The semiconductor memory device can be an SRAM or DRAM, for example, and includes a memory array and peripheral circuit on a substrate. In one aspect of the present invention, a buried layer of the same conductivity type as that of the substrate, but with a higher impurity concentration than that of the substrate, is provided beneath at least one of the peripheral circuit and memory array. A further region can extend from the buried layer, for example, to the surface of the semiconductor substrate, the buried layer and further region in combination acting as a shield to prevent minority carriers from penetrating to the device elements. As a second aspect of the present invention, first carrier absorbing areas (to absorb minority carriers) are located between the memory array and the switching circuit of the peripheral circuit, and second carrier absorbing areas are provided to surround input protective elements of the device. As a third embodiment of the present invention, a plurality of isolation regions of the same conductivity type are provided, with unequal voltages applied to these isolation regions, or unequal voltages applied to the substrate, on the one hand, and to these isolation regions, on the other.

Owner:RENESAS TECH CORP

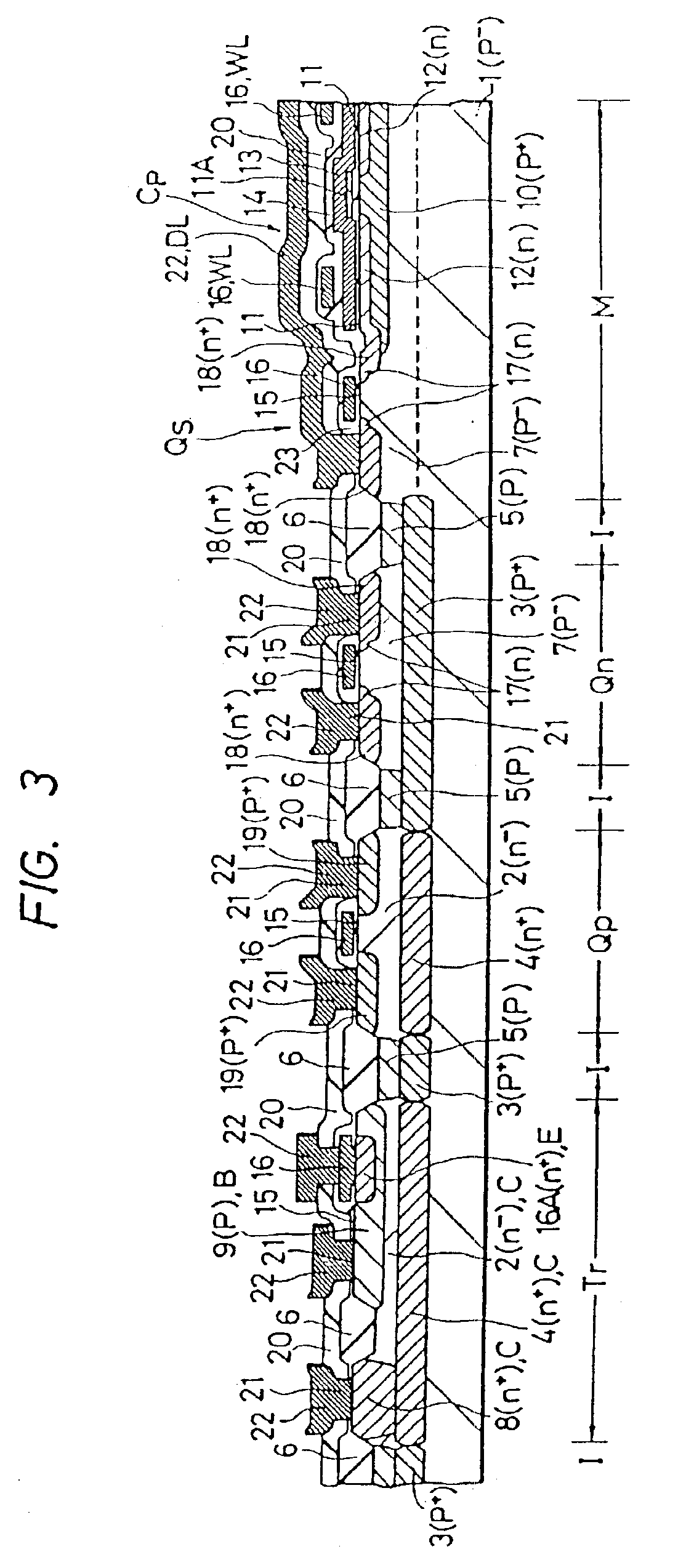

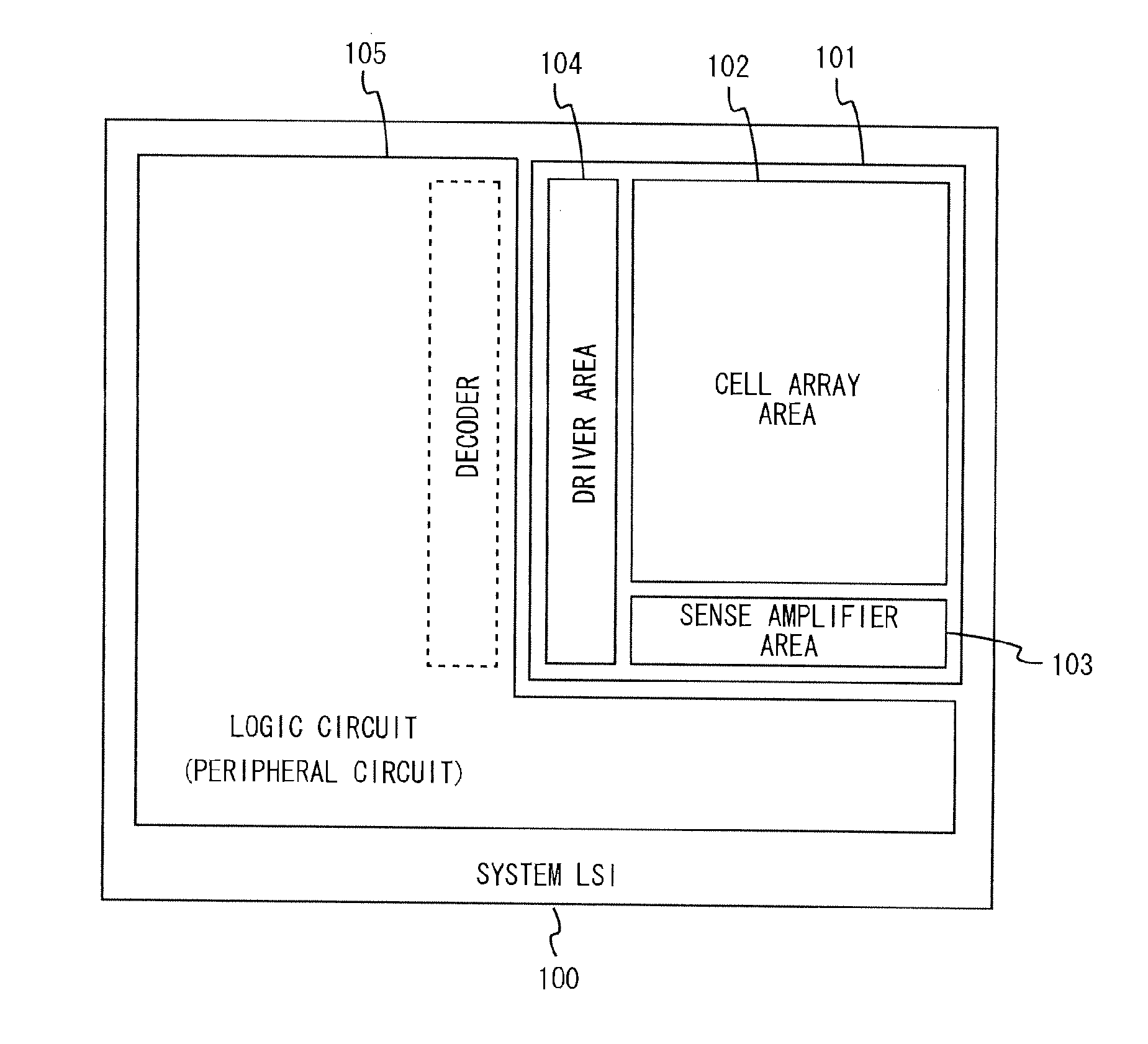

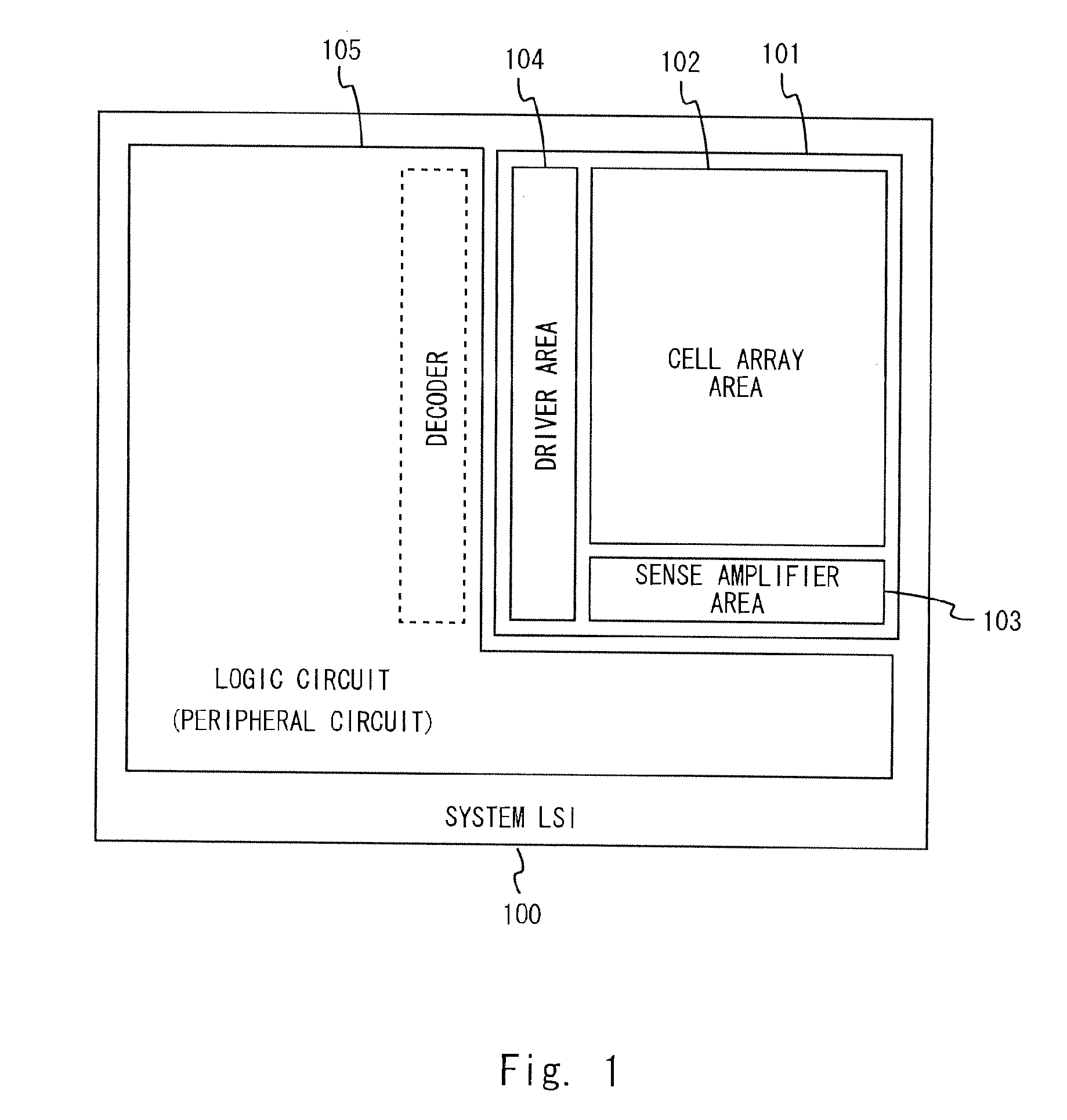

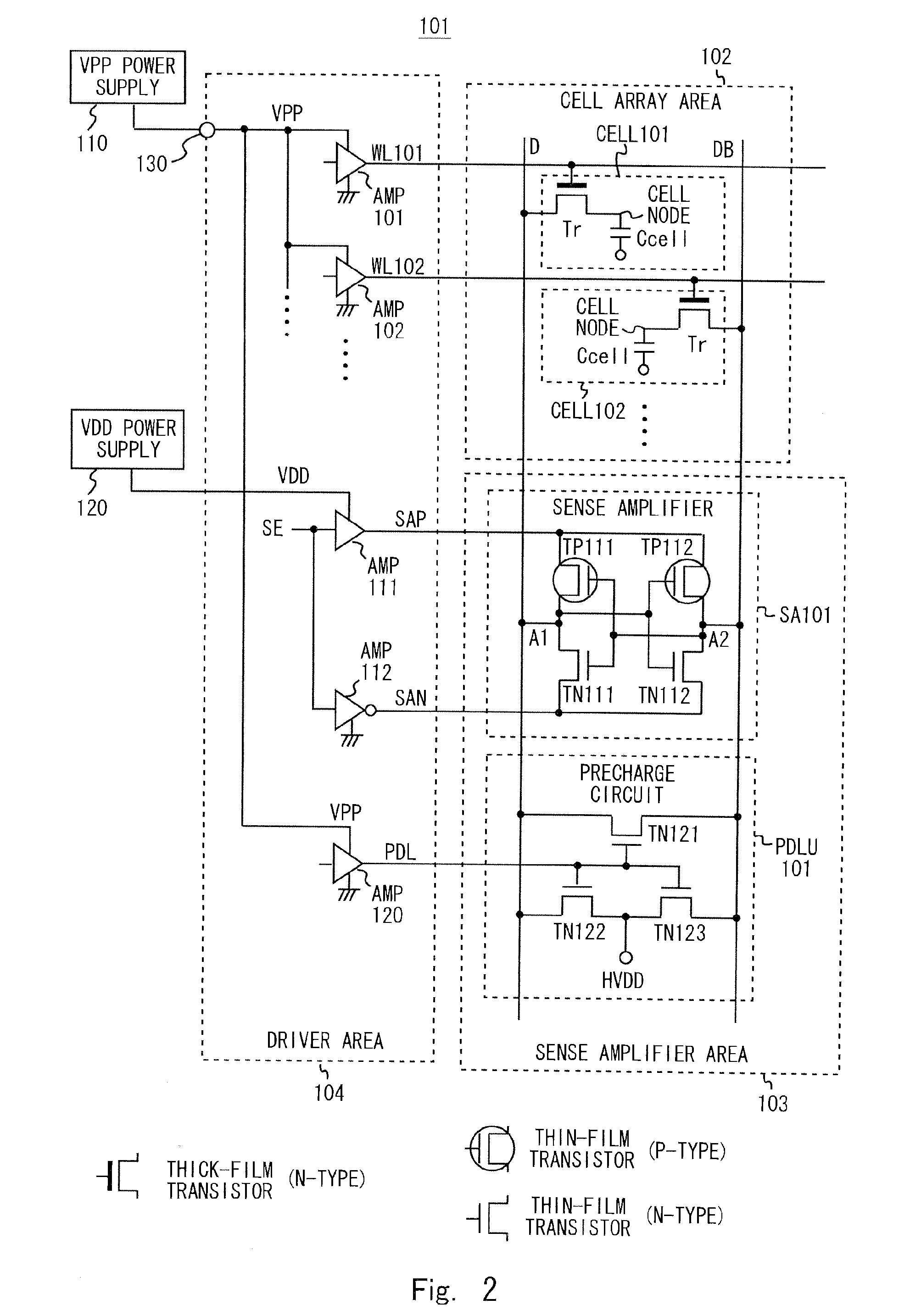

Semiconductor integrated device

InactiveUS20100290300A1High-speed operationRun at high speedDigital storageHemt circuitsIntegrated devices

Provided is a semiconductor integrated device including a semiconductor memory circuit and a peripheral circuit of the semiconductor memory circuit. The peripheral circuit includes a first transistor having a first voltage as a breakdown voltage of a gate oxide film. The semiconductor memory circuit includes a pair of bit lines, one of the pair of bit lines being connected to a gate transistor of a memory cell, and a precharge circuit that includes a transistor having a breakdown voltage substantially equal to that of the first transistor, and precharges the pair of bit lines to a predetermined voltage in response to an activation signal. The activation signal of the precharge circuit is a second voltage higher than the first voltage.

Owner:RENESAS ELECTRONICS CORP

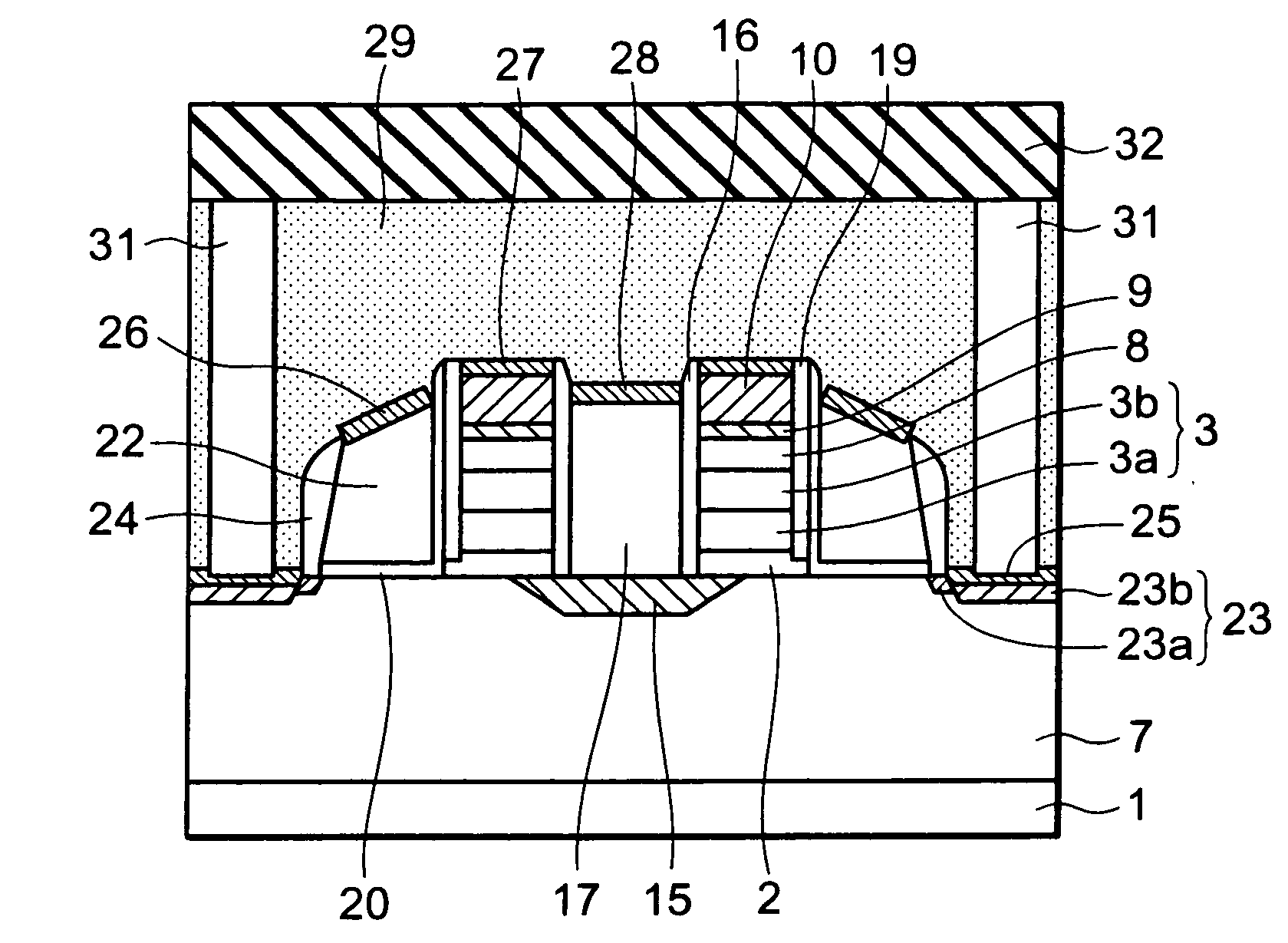

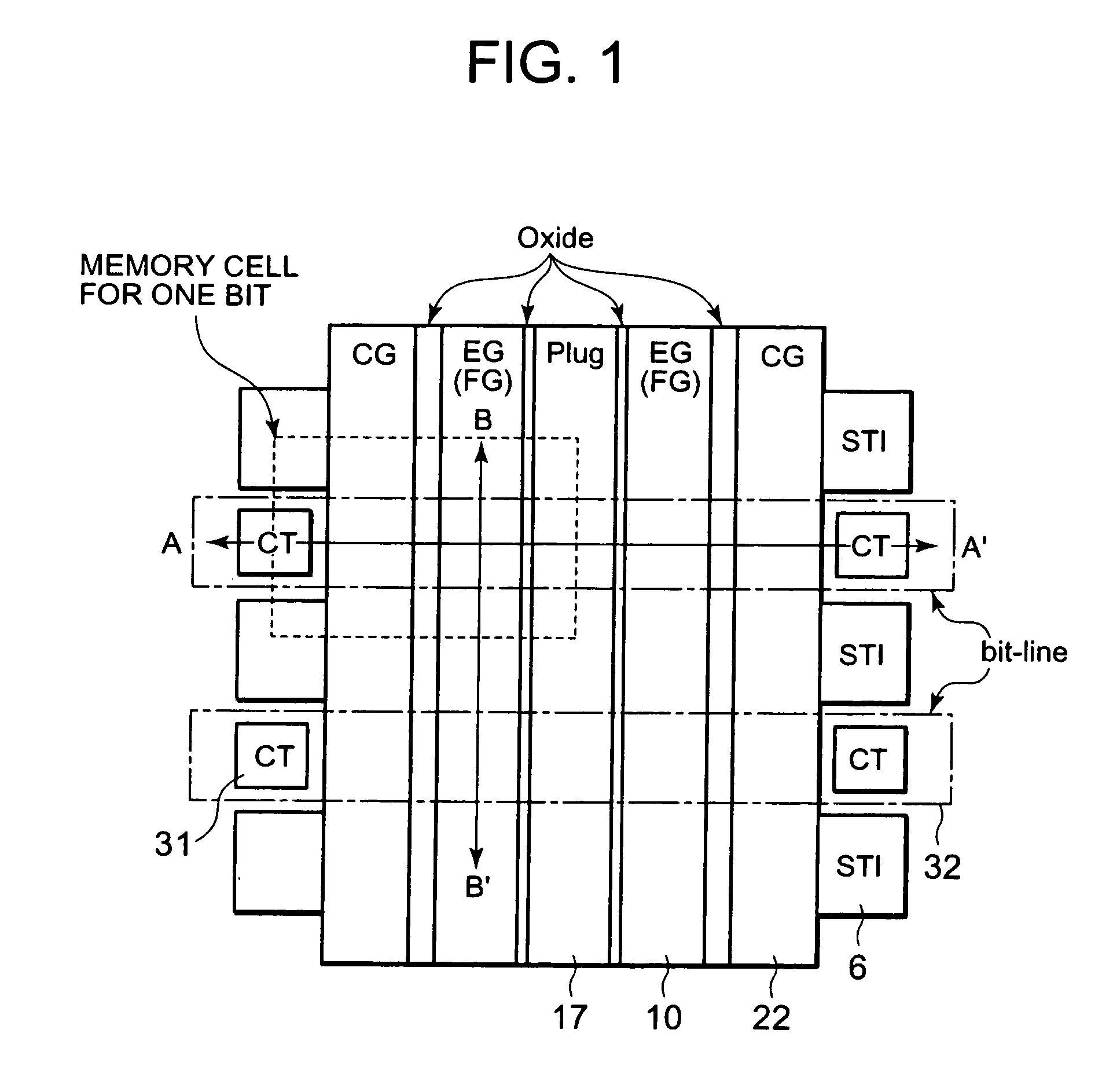

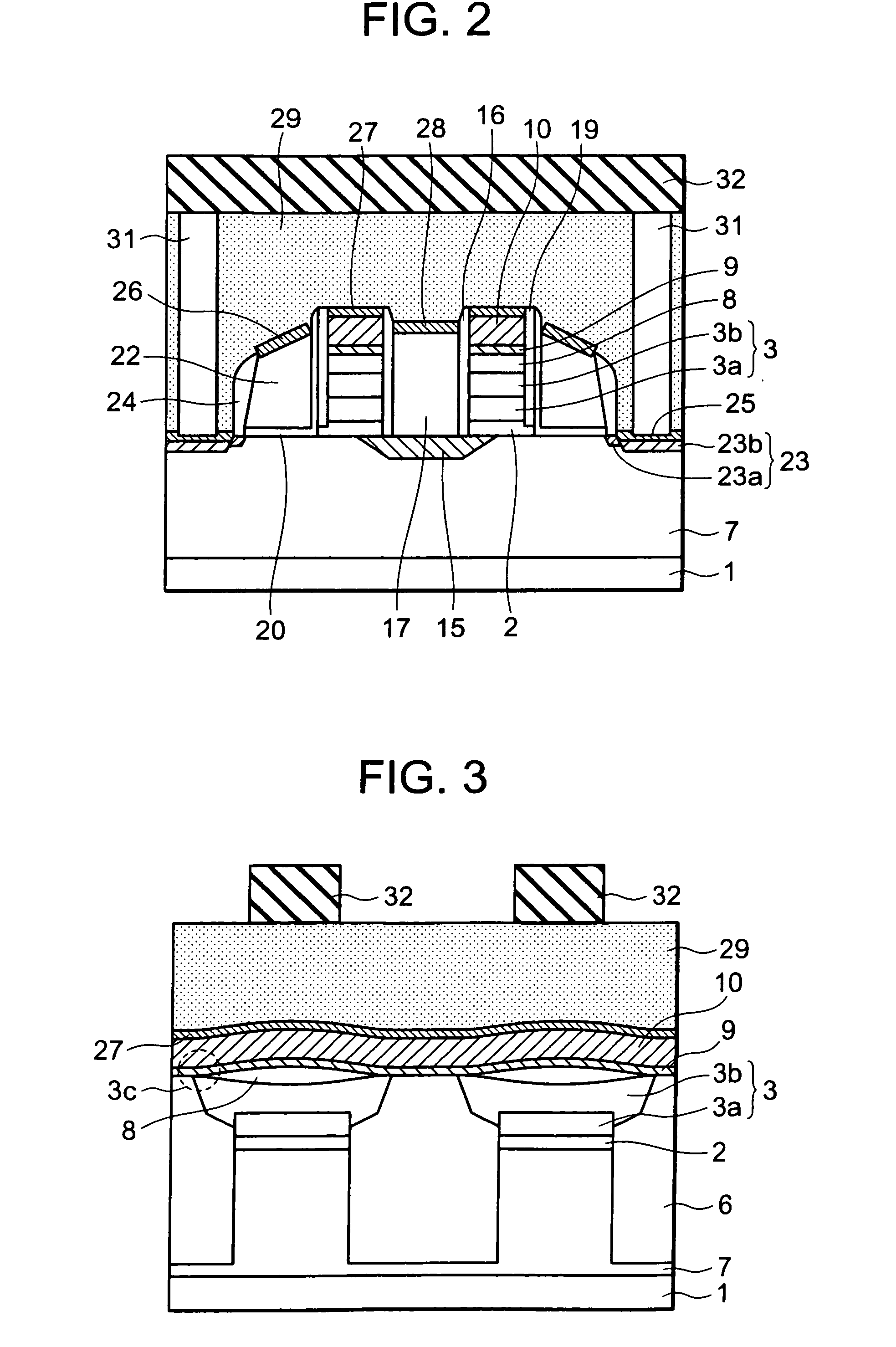

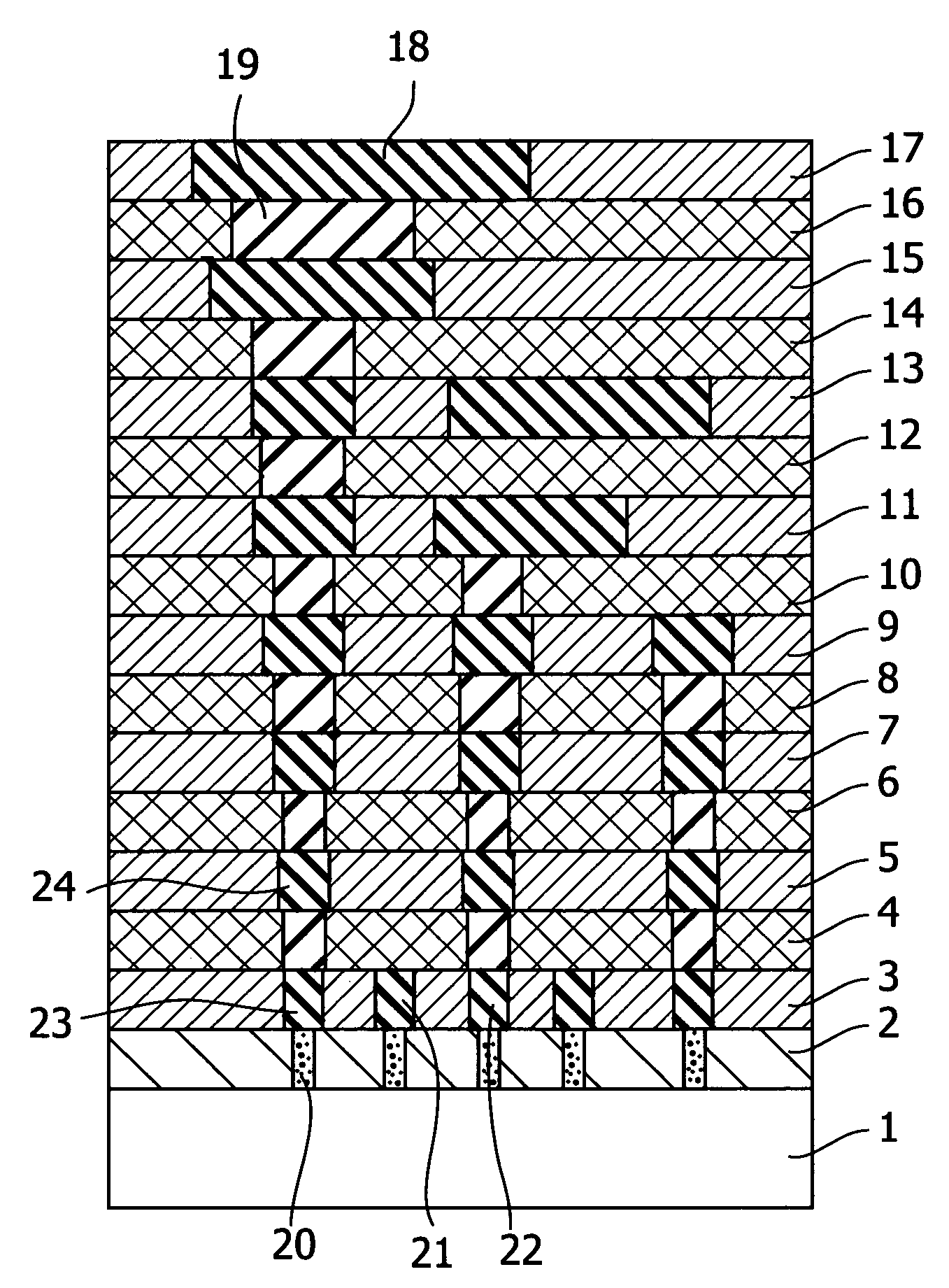

Non-volatile semiconductor memory device having an erasing gate

InactiveUS20090085092A1High speed operationLow voltage operationTransistorSolid-state devicesEngineeringDiffusion layer

A non-volatile semiconductor memory device includes: a floating gate formed above the semiconductor substrate; an erasing gate formed above the floating gate; a control gate formed above a channel region of a surface layer of the semiconductor substrate at a position corresponding to one lateral side of the floating gate and the erasing gate; a diffusion layer formed on the semiconductor substrate at a position corresponding to another lateral side of the floating gate and the erasing gate; a plug formed above the diffusion layer, the plug coupled to the diffusion layer; a first silicide film formed on an upper surface of the erasing gate; and a second silicide film formed on an upper surface of the plug, in which a height of the upper surface of the plug is flush with / or lower than a height of the upper surface of the erasing gate.

Owner:RENESAS ELECTRONICS CORP

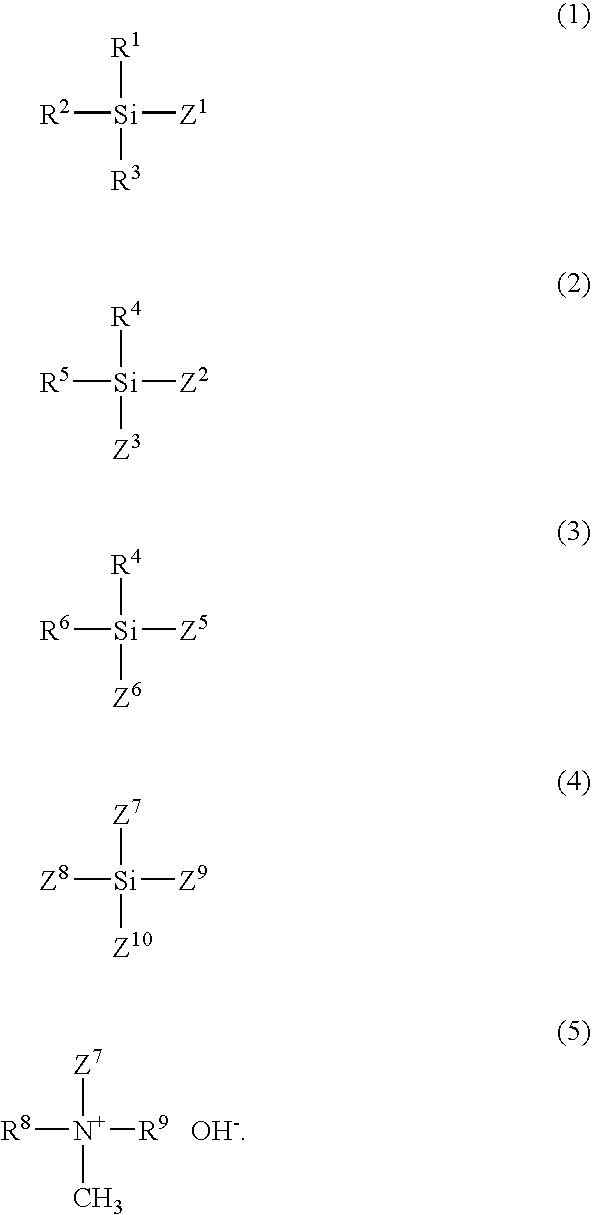

Composition for forming a porous film prepared by hydrolysis and condensation of an alkoxysilane using a trialkylmethylammonium hydroxide catalyst

InactiveUS7239018B2High-speed operationReduce parasitic capacitanceLiquid surface applicatorsSilicaHalogenLow-k dielectric

Provided is a composition formed by hydrolysis and condensation composition of the alkoxysilane, the composition comprising a reduced amount of metallic and halogen impurities and being applicable as electronic material. Also provided is an insulating film having low dielectric constant produced by applying the composition and sintering it. More specifically, a method for manufacturing a composition for forming a film, comprising a step of hydrolysis and condensation of alkoxysilane or a partial hydrolysis product of the alkoxysilane in an organic solvent in the presence of trialkylmethylammonium hydroxide as catalyst, wherein the alkoxysilane is selected from the groups consisting of compounds represented by formulae (1) to (4) below, and the trialkylmethylammonium hydroxide is represented by formula (5) below. Provided are a composition for forming a film obtained by the method, and a low dielectric constant film having low metallic and halogen impurities, the film produced by applying the composition for forming a film on a substrate and sintering it.

Owner:SHIN ETSU CHEM IND CO LTD +1

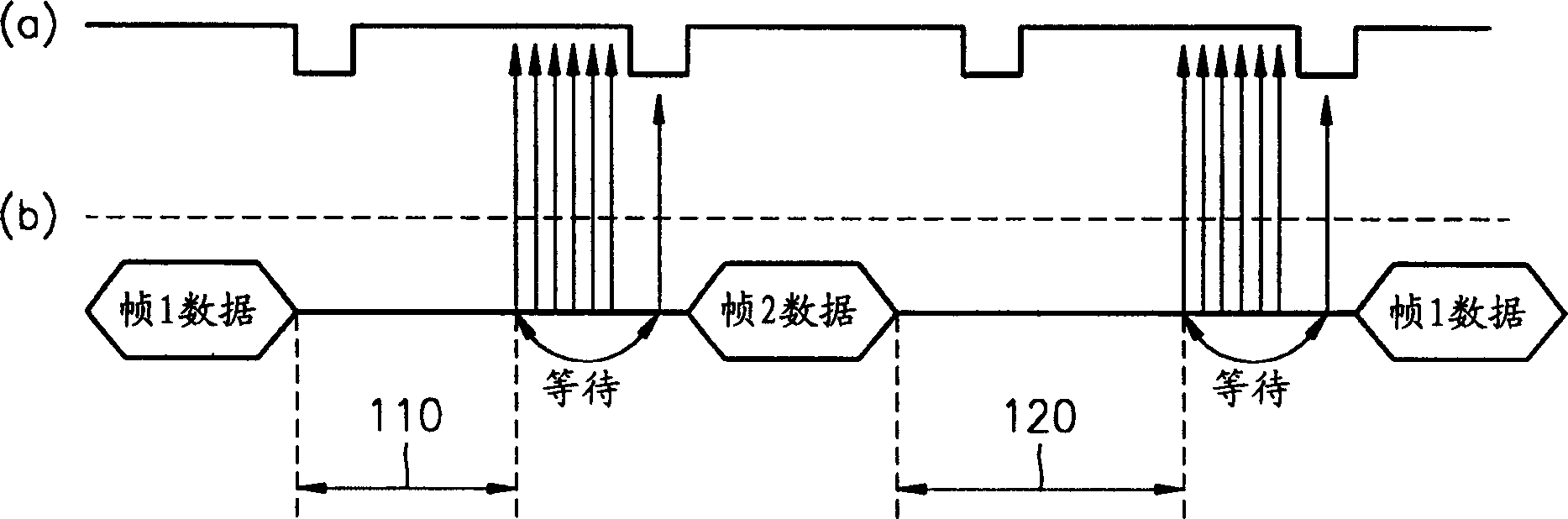

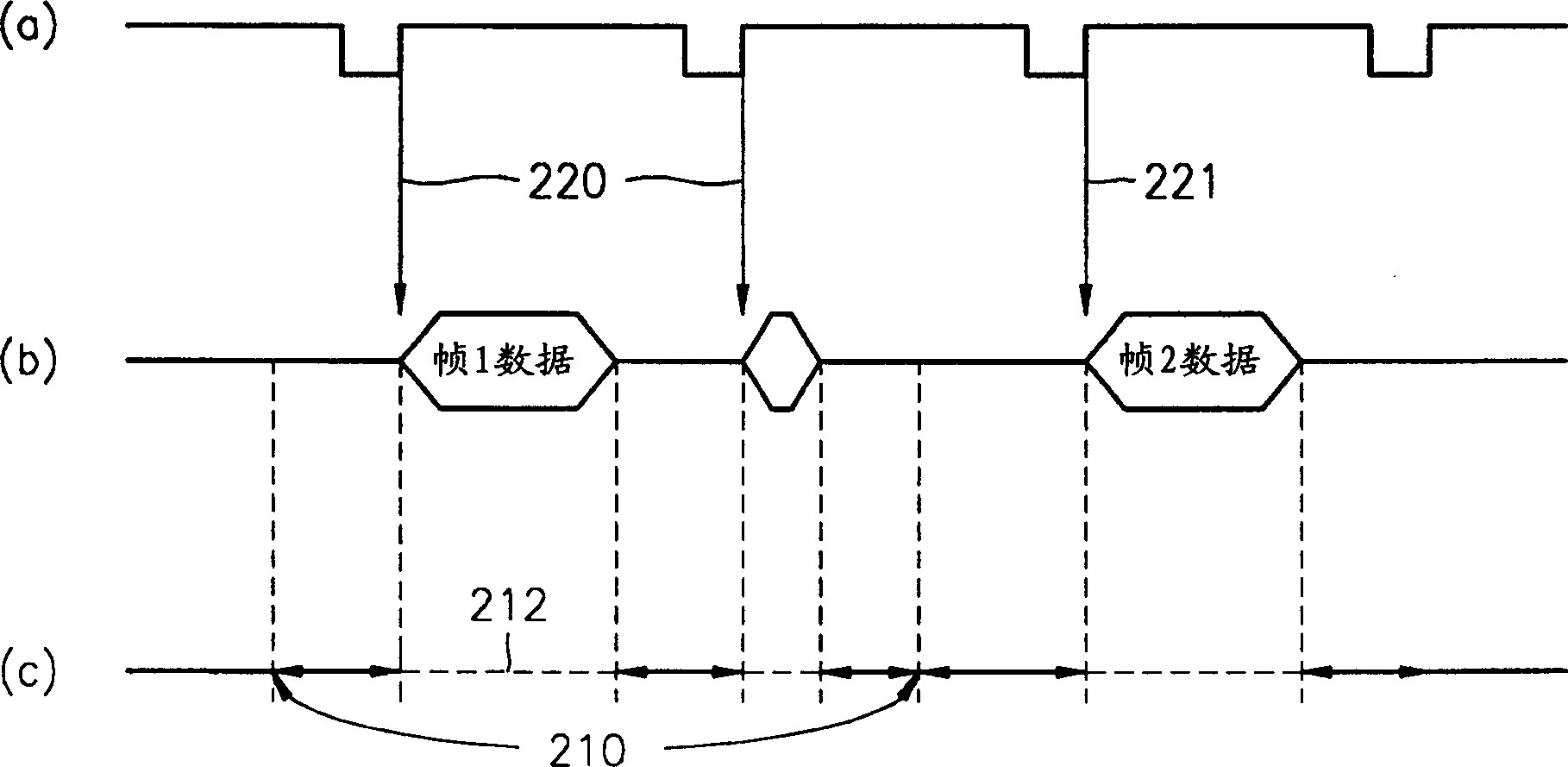

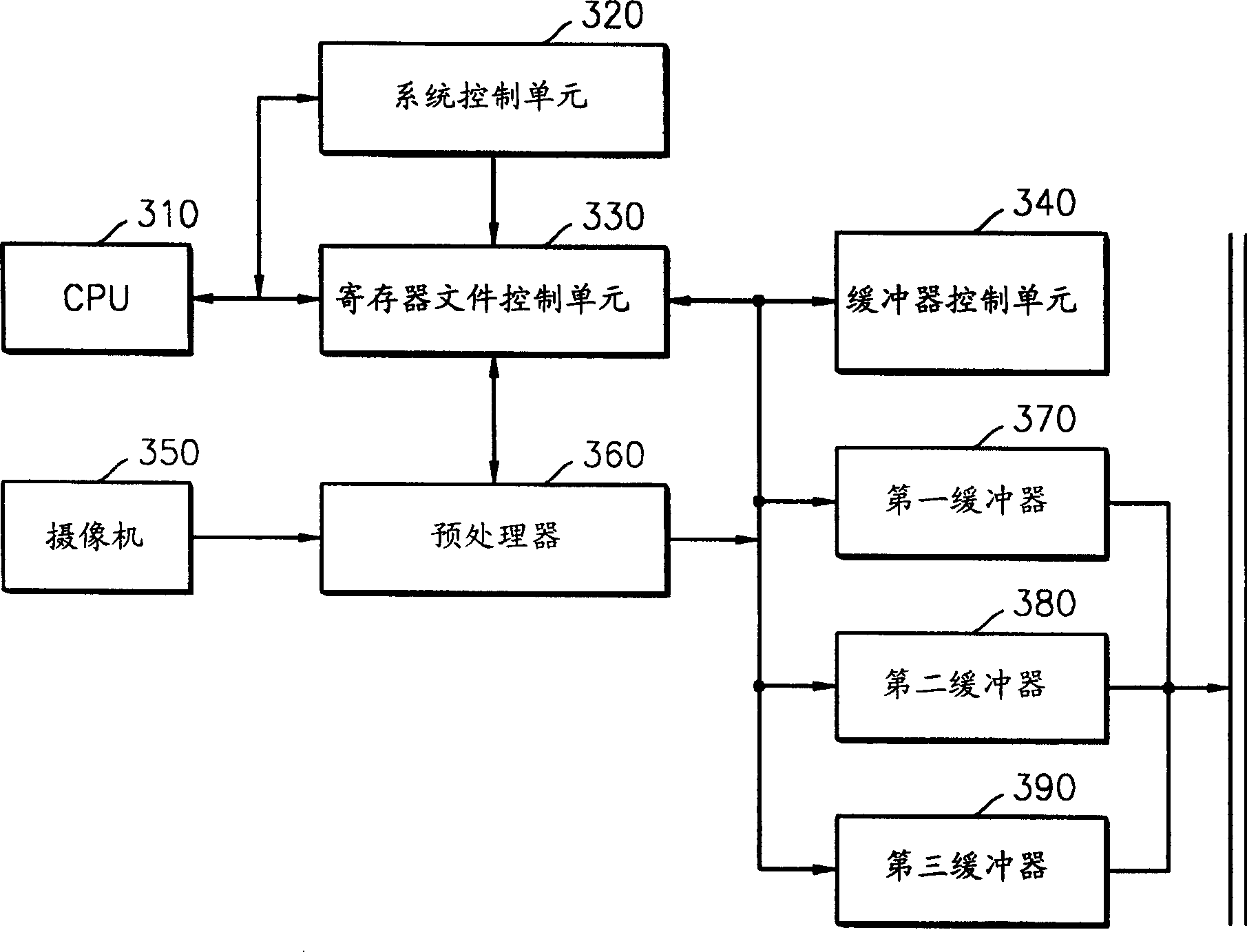

Video preprocess/postprocess method for effective processing video and its device

InactiveCN1381990AHigh speed operationTelevision system detailsImage codingPretreatment methodComputer graphics (images)

It relates to a video preprocessing / postprocessing device capable of stably operating at high speed with a small amount of memory by utilizing a new hardware-software cooperation method, and provides a method used by the device. A video preprocessing method for efficiently capturing video includes the steps of: sequentially assigning a number to a plurality of storage areas, and cyclically incrementing the number in response to a frame synchronization signal; checking the memory area being stored in response to the frame synchronization signal, and capturing incoming video data; And storing the captured video data in a predetermined order in the memory area. A video post-processing method for effectively displaying video includes the steps of: sequentially assigning a number to a plurality of storage areas, and cyclically incrementing the number in response to a frame synchronization signal; displaying the memory area in response to the frame synchronization signal, checking the displayed storage area, and resetting the displayed storage area with a predetermined number; sequentially storing the video data in the memory area; and sequentially displaying the video data stored in the memory area.

Owner:SAMSUNG ELECTRONICS CO LTD

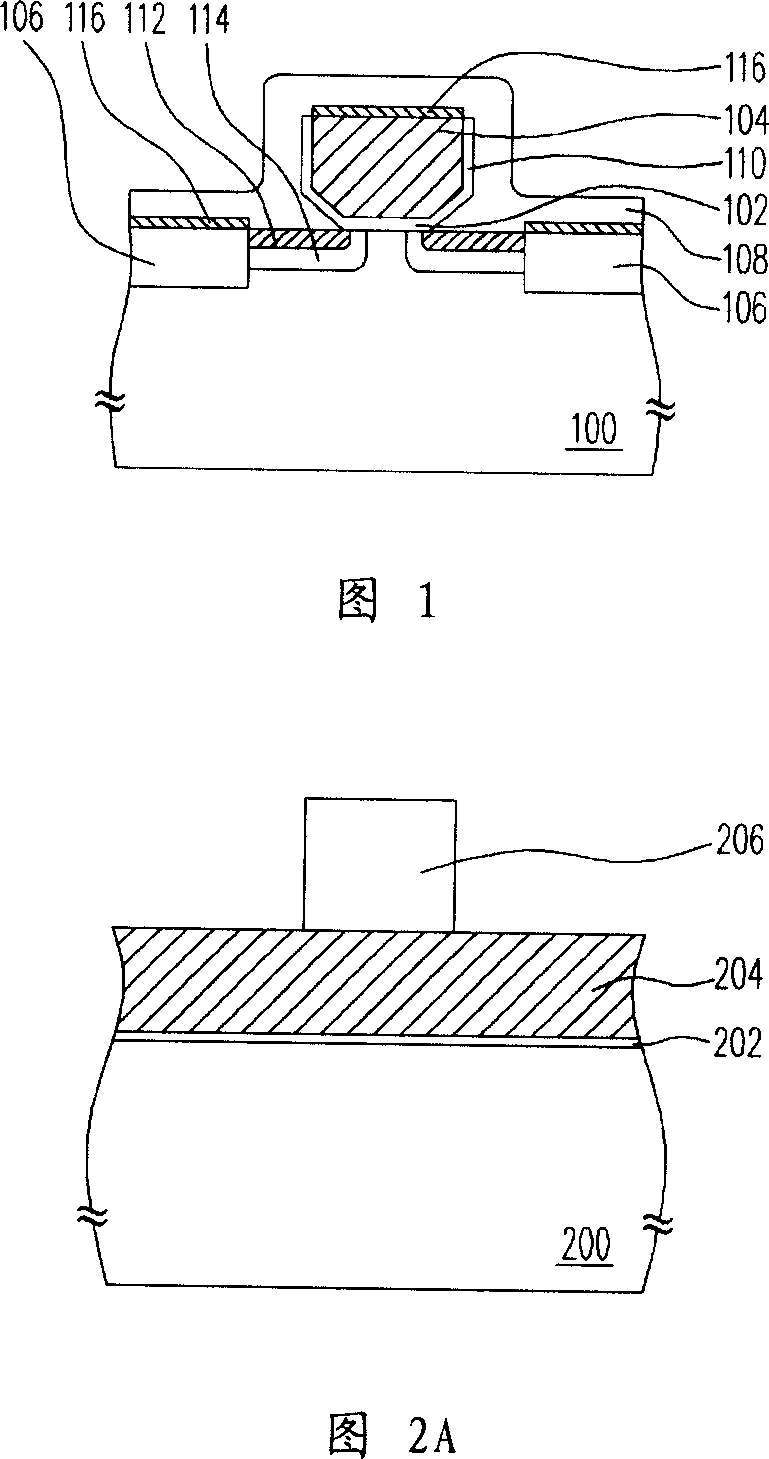

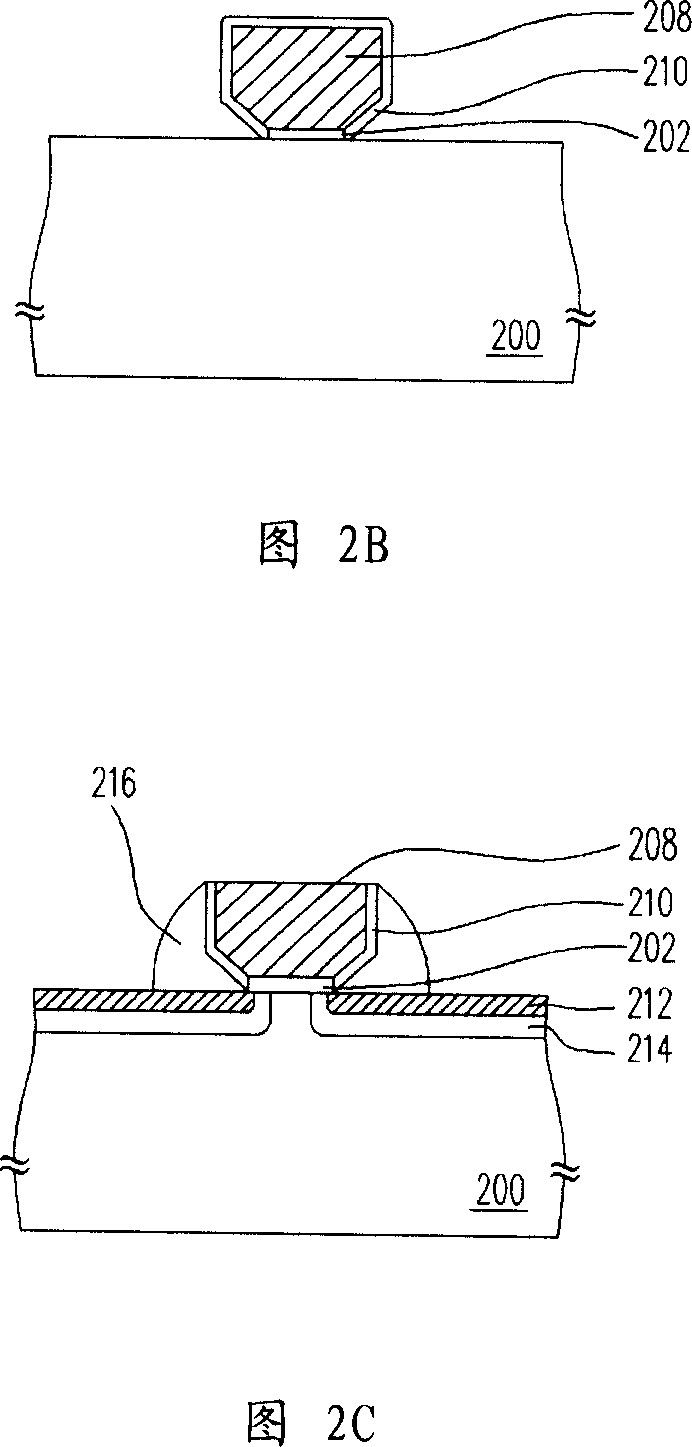

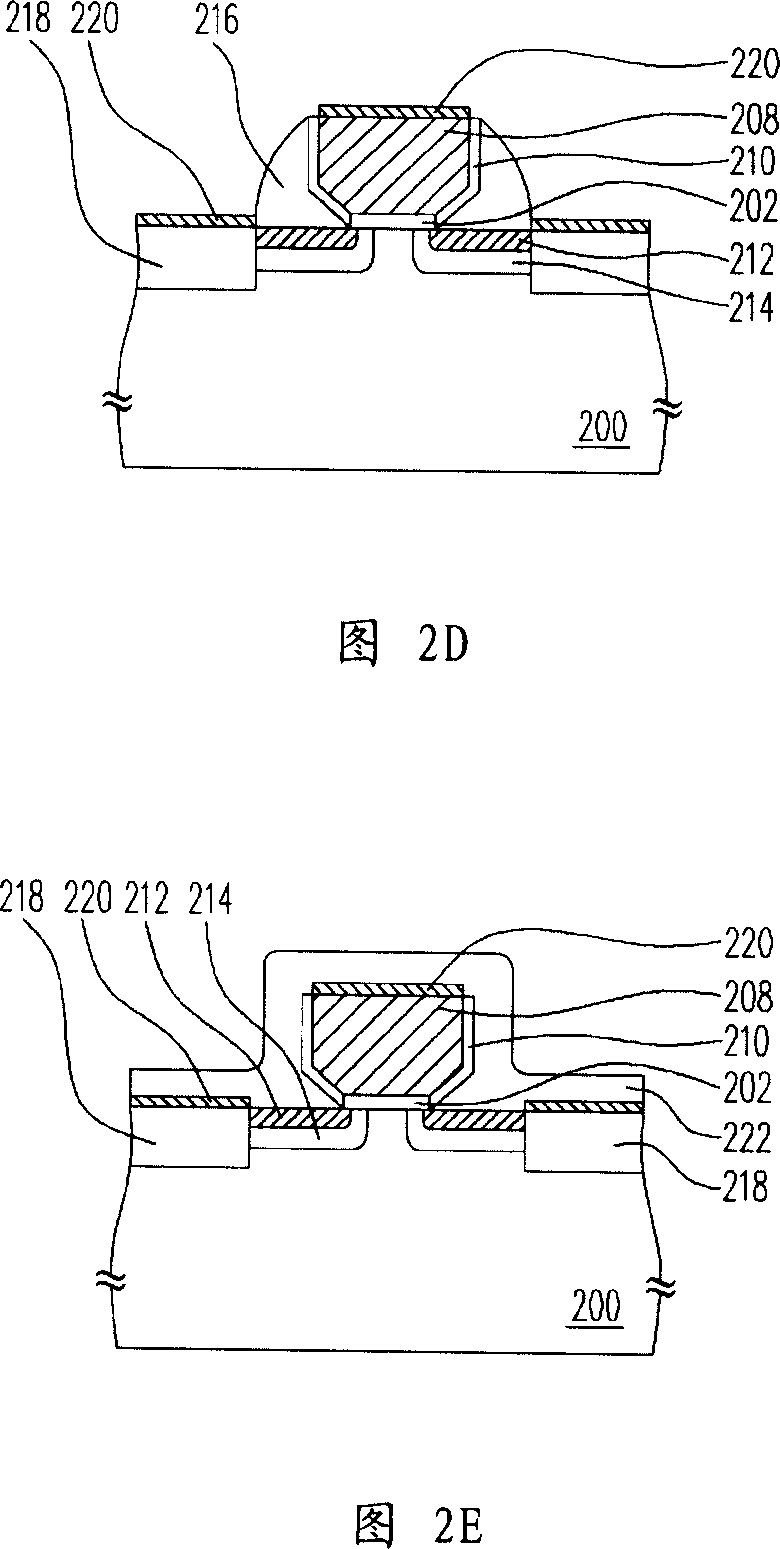

Semiconductor element and its manufacturing method

InactiveCN101071823AIncrease stressReduce contact areaSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricPhysics

The invention is a semiconductor component, comprising a substrate, a gate dielectric layer, a gate, a source / drain region, and a stress layer, where the gate dielectric layer is arranged on the substrate, the gate is arranged on the gate dielectric layer and the area of the top of the gate is more than that of the bottom; in addition, the source / drain region is arranged in the substrate on two sides of the gate, and the stress layer is arranged on the substrate and covers the gate and the source / drain region.

Owner:UNITED MICROELECTRONICS CORP