Semiconductor integrated circuit device

An integrated circuit and semiconductor technology, applied in the field of semiconductor integrated circuit devices, can solve problems such as restrictions on the formation of public buses, and achieve the effects of increased degrees of freedom, noise prevention, and low impedance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

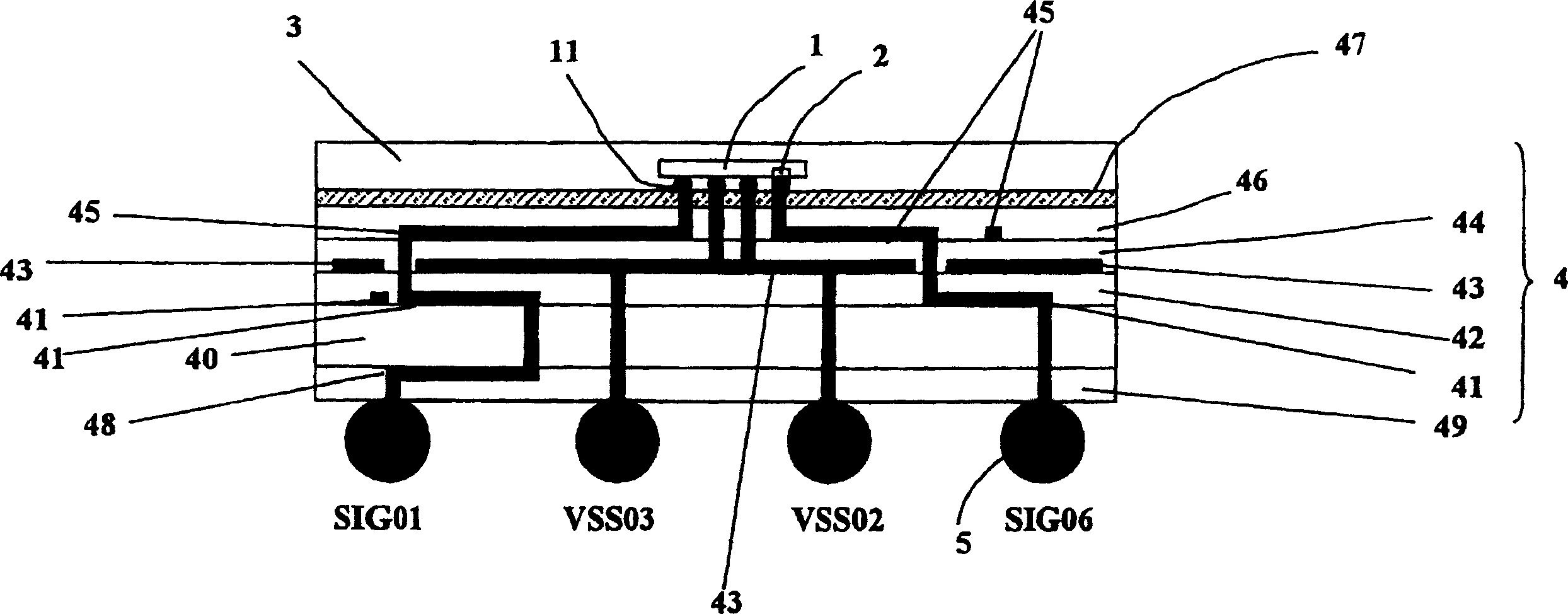

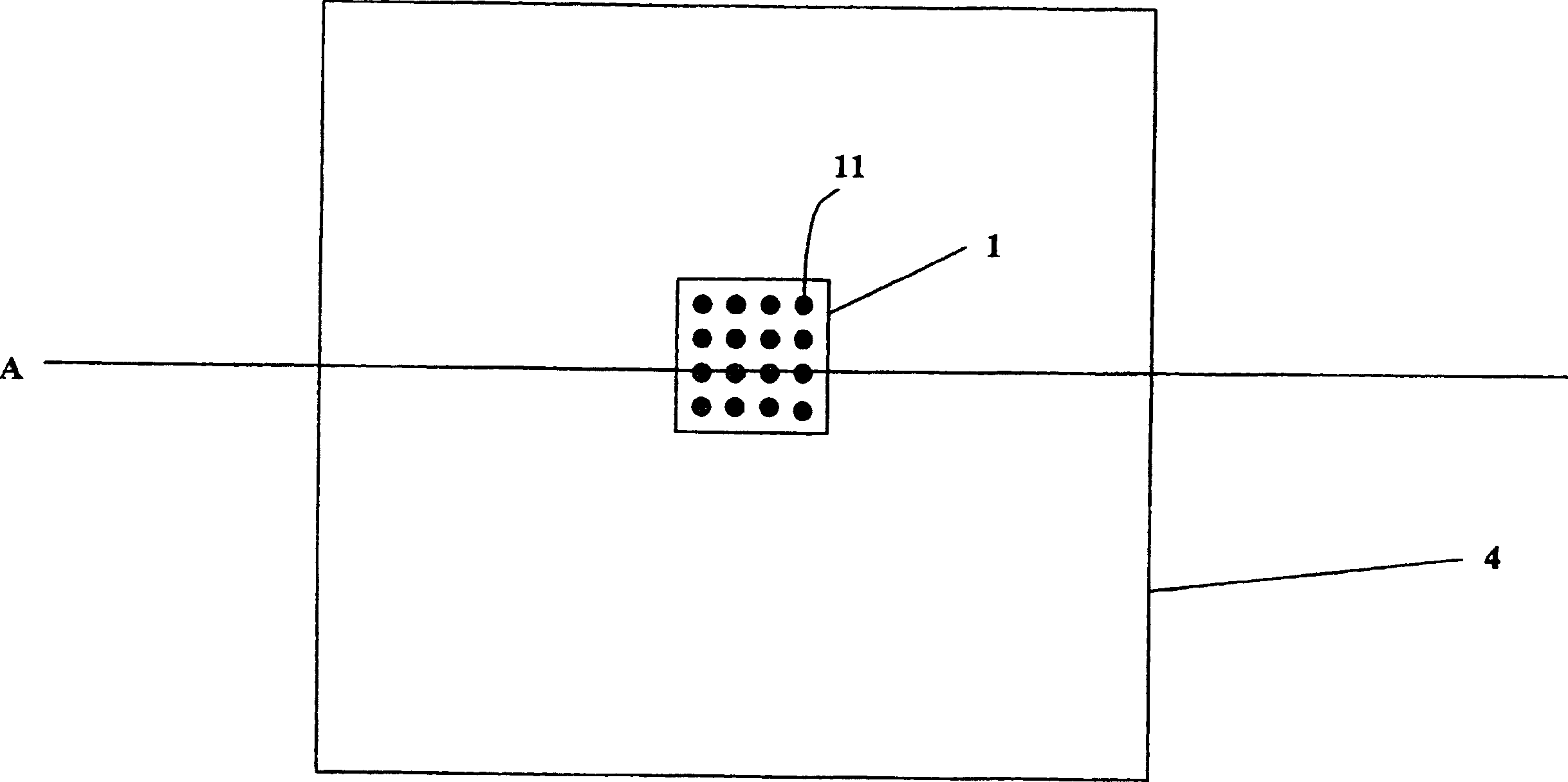

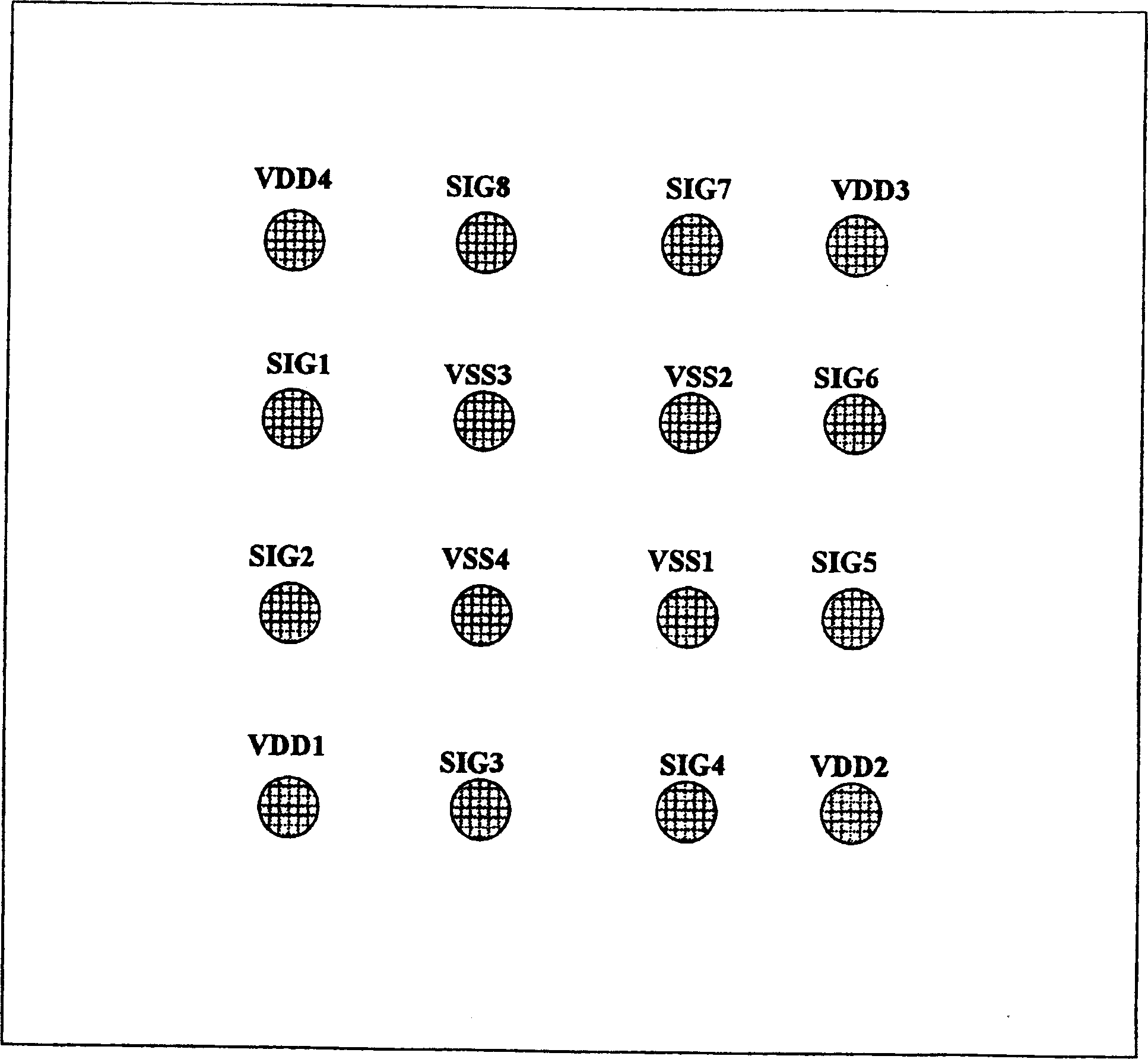

[0068] figure 1 is a cross-sectional view of the structure, Figures 2 to 9 are the plan and cross-sectional views of the semiconductor chip and each layer, such as figure 1 and Figure 2 to Figure 9 As shown, the semiconductor integrated circuit device in this embodiment has the following composition. The semiconductor chip 1 is mounted on a wiring substrate with a multilayer structure having a conductive plane, and is connected to the electrostatic protection circuit 2 provided in the semiconductor chip when the power supply line is connected to the conductive plane 43 . The layers are formed in such a way that when the layers are placed on top of each other, the through-holes overlap each other and the layers are connected to each other via these through-holes.

[0069] Such as figure 1 As shown, the device includes: first to fourth circuit systems separately mounted on a semiconductor chip 1 and respectively driven by different power supply systems; ball grid arrays...

no. 2 example

[0086] In this connection, in the above embodiments, the conductive plane 43 formed on the wiring substrate 4 is used as a ground. However, in this example, if Figure 11 , 12(a) and 12(b), in addition to the ground line composed of the conductive plane 43, a conductive plane 43S and an insulating layer 44S are added, and the conductive plane is formed as a power line. On this conductive plane 43S, power supply lines are connected via contacts CD1 to CD4.

[0087] The other points of this structure are the same as those of the first embodiment described above.

[0088] In this connection, the same reference numerals are used for the same components in the first and second embodiments.

[0089] In this structure, not only the ground line is composed of the conductive plane 43 , but also the power line is composed of the conductive plane 43 . Therefore, it is possible to provide a stable potential, and the generation of noise can be attenuated.

no. 3 example

[0091] In this connection, in the previously described embodiments, the conductive plane is connected to one potential. However, in this example, if Figure 13 , 14 As shown in (a) and 14(b), the conductive plane is divided into two parts, the power plane 43b is formed in the outer C-shaped area, and the inner area is used as the ground plane 43a at a predetermined interval. The ground line is connected to this ground plane 43a through contacts C1 to C4. Power lines are connected to this power plane 43b through CD1 to CD4.

[0092] The other points of this structure are the same as those of the first embodiment described above.

[0093] In this connection, the same reference numerals are used for the same parts in the first and third embodiments.

[0094] In this structure, conductive planes with two potentials can be formed on one conductive layer without increasing the number of stacked layers. Therefore, the device can be miniaturized, and the degree of freedom in circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More