Flip-chip type semiconductor packaging structure and chip bearing member

A technology of flip-chip and packaging structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., which can solve the problems of absorbing thermal stress, inability to solve effectively, and delamination of dielectric layers, etc., to achieve heat absorption Stress, the effect of avoiding uneconomical problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The features and functions of the present invention will be further described below through specific specific embodiments in conjunction with the accompanying drawings.

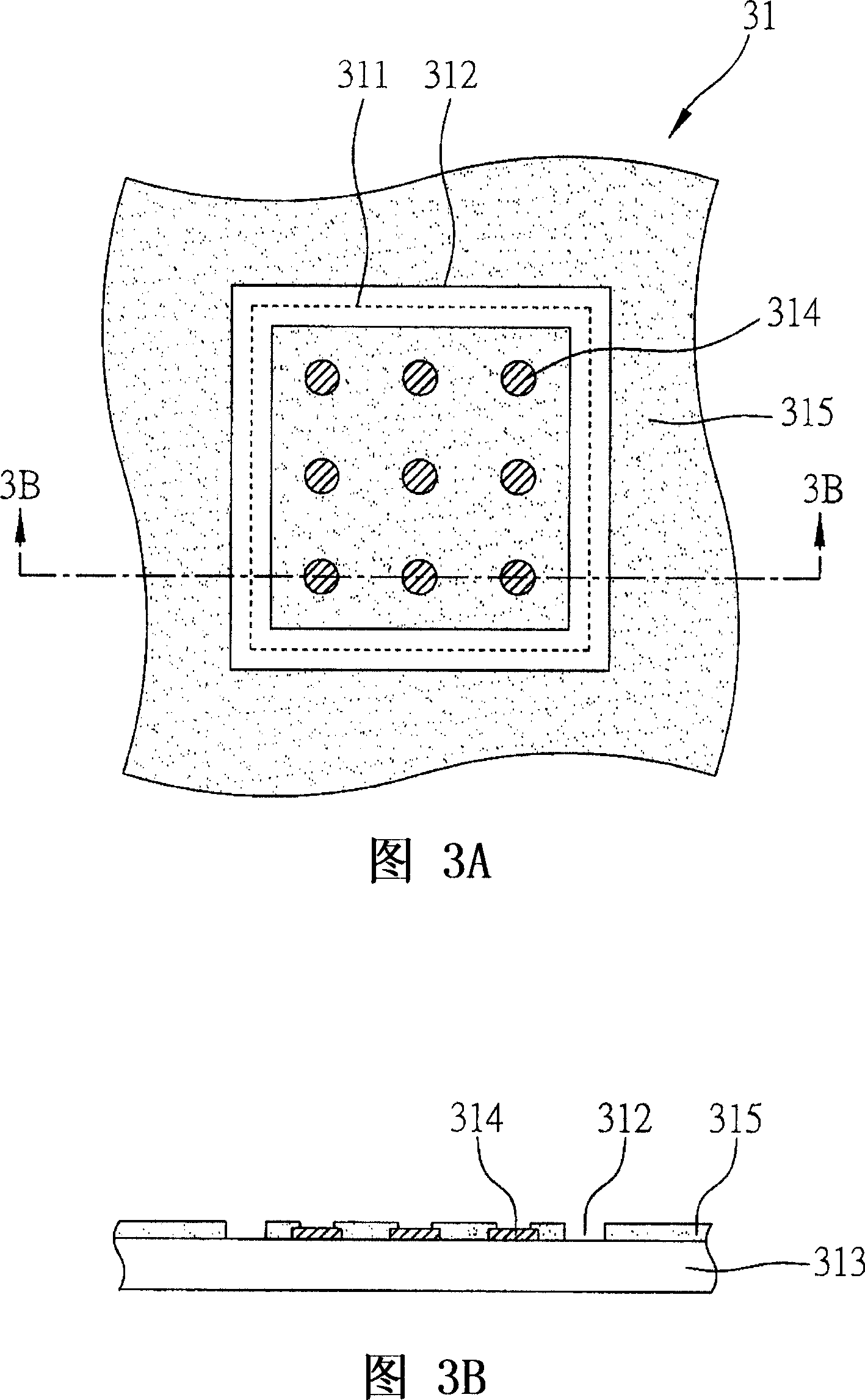

[0046] Referring to FIGS. 3A and 3B , they are schematic diagrams of a chip carrier for a flip-chip semiconductor packaging structure according to the present invention, wherein FIG. 3B is a schematic cross-sectional view corresponding to FIG. 3A .

[0047]The chip carrier is a substrate 31, and the substrate 31 includes a body; a chip connection area 311 preset on the surface of the body for connecting flip-chip semiconductor chips; The outer edge of the area 311 is used for filling with low Young's modulus filler.

[0048] The substrate body may for example consist of a core layer 313 , a plurality of solder pads 314 disposed on the surface of the core layer, and a solder resist layer 315 covering the core layer 313 and exposing the solder pads 314 . The solder pad 314 is disposed in the chip placem...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More