Insulated gate semiconductor device

An insulated gate, semiconductor technology, used in semiconductor devices, electrical components, circuits, etc., can solve problems such as limitations, and achieve the effects of increasing current capacity, reducing device miniaturization, and expanding contact area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

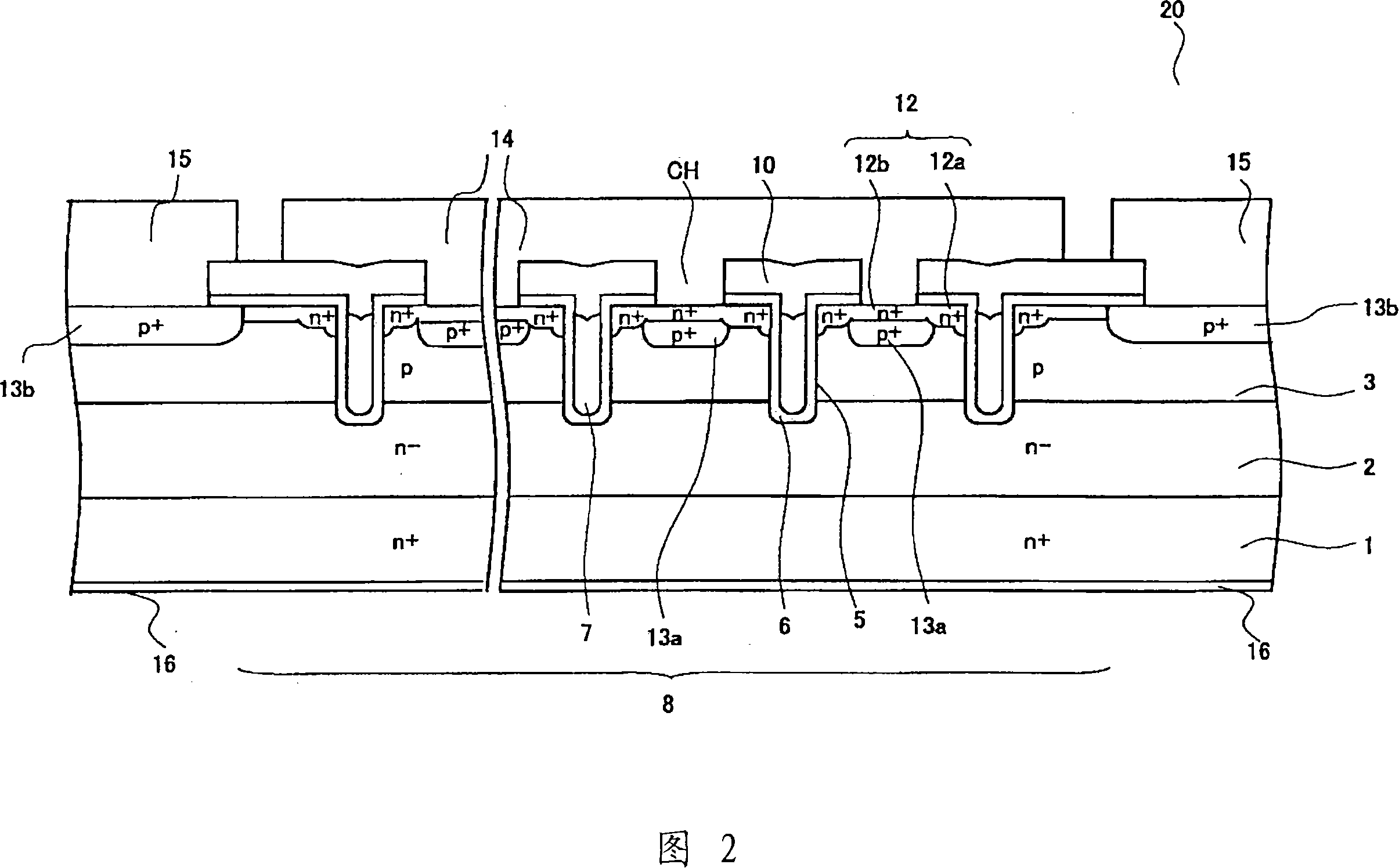

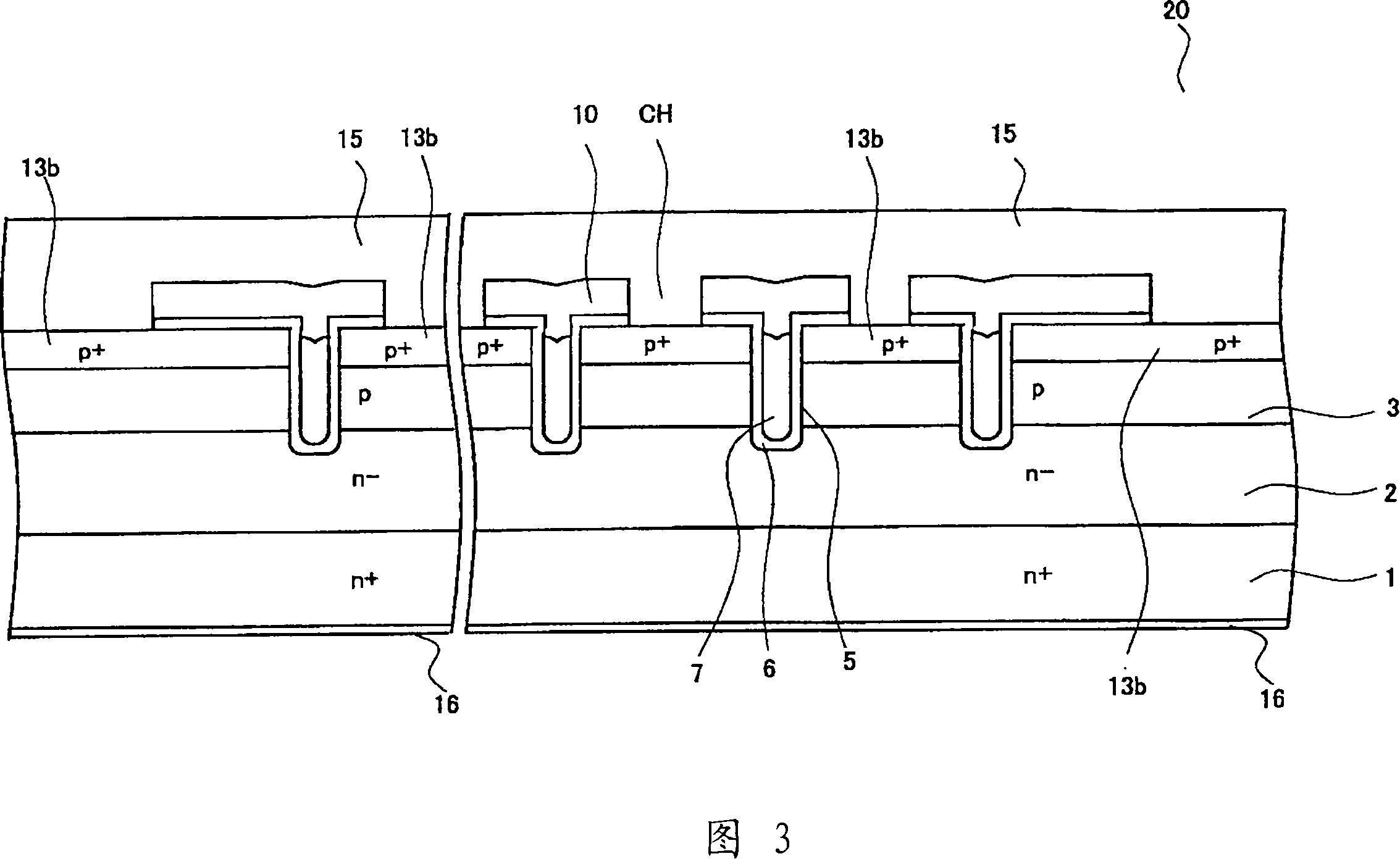

[0078] 1-9, the embodiment of the present invention will be explained by taking an n-channel trench structure MOSFET as an example.

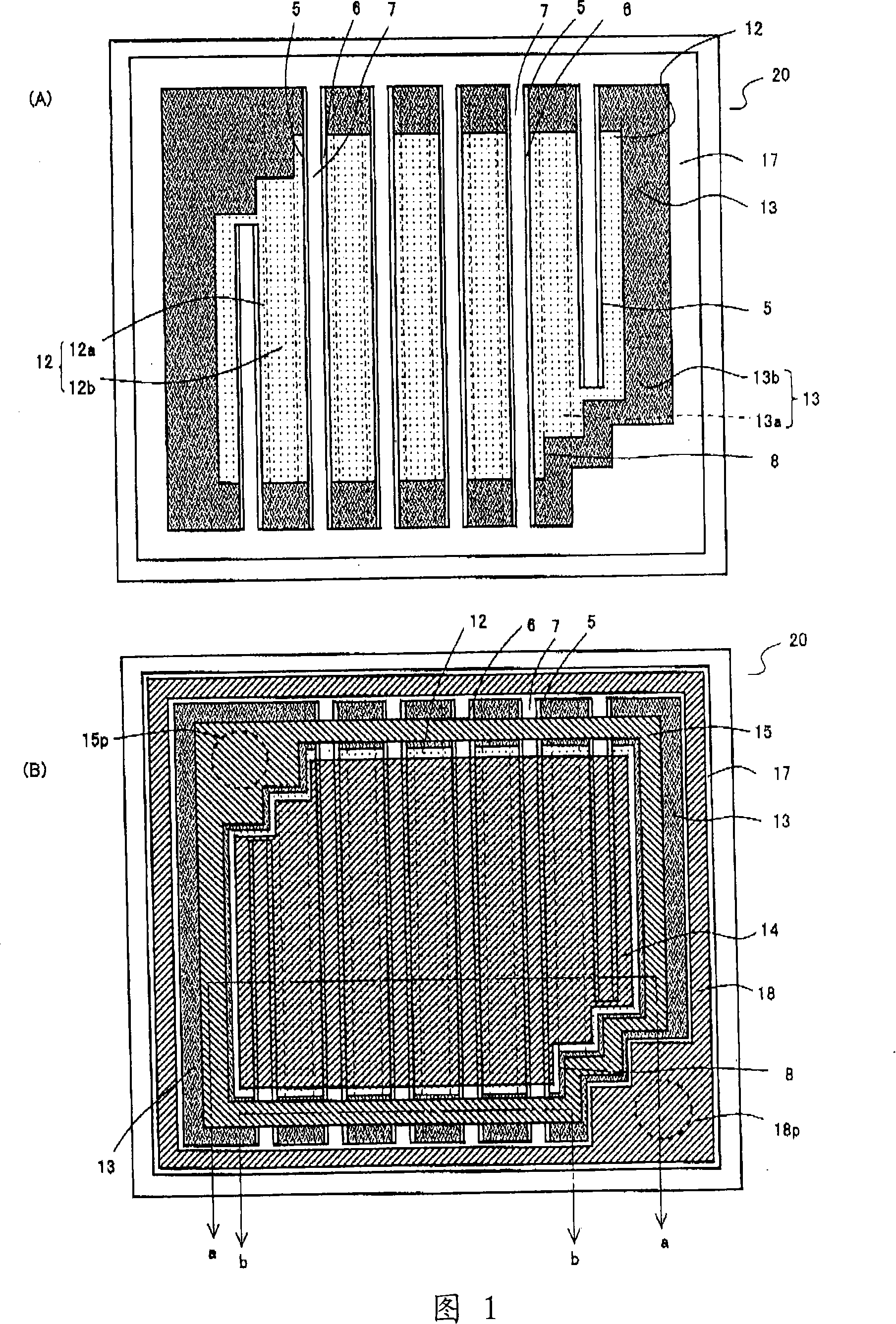

[0079] First, the first embodiment will be described with reference to FIGS. 1 to 8. Fig. 1 is a plan view showing the MOSFET. FIG. 1(A) is a diagram omitting a surface electrode layer and an interlayer insulating film, and FIG. 1(B) is a diagram where a surface electrode layer is arranged.

[0080] MOSFET 20 is composed of semiconductor substrate 1, semiconductor layer 2, channel layer 3, trench 5, gate insulating film 6, gate electrode 7, source region 12, back gate region 13, interlayer insulating film 10, first The electrode layer 14, the second electrode layer 15 and the third electrode layer 16 are constituted.

[0081] On the surface of the substrate where the n- type semiconductor layer is arranged on the n+ type silicon semiconductor substrate, the channel layer 3 as a p-type impurity region is provided. The trench 5 is formed in a pattern ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More