Wafer test card over current protection method and related wafer test system

A chip testing and overcurrent technology, applied in semiconductor/solid-state device testing/measurement, measuring electricity, measuring electrical variables, etc., can solve problems such as test card burnout, probe damage, and test system failure to detect short-circuit conditions, etc., to achieve The effect of preventing damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

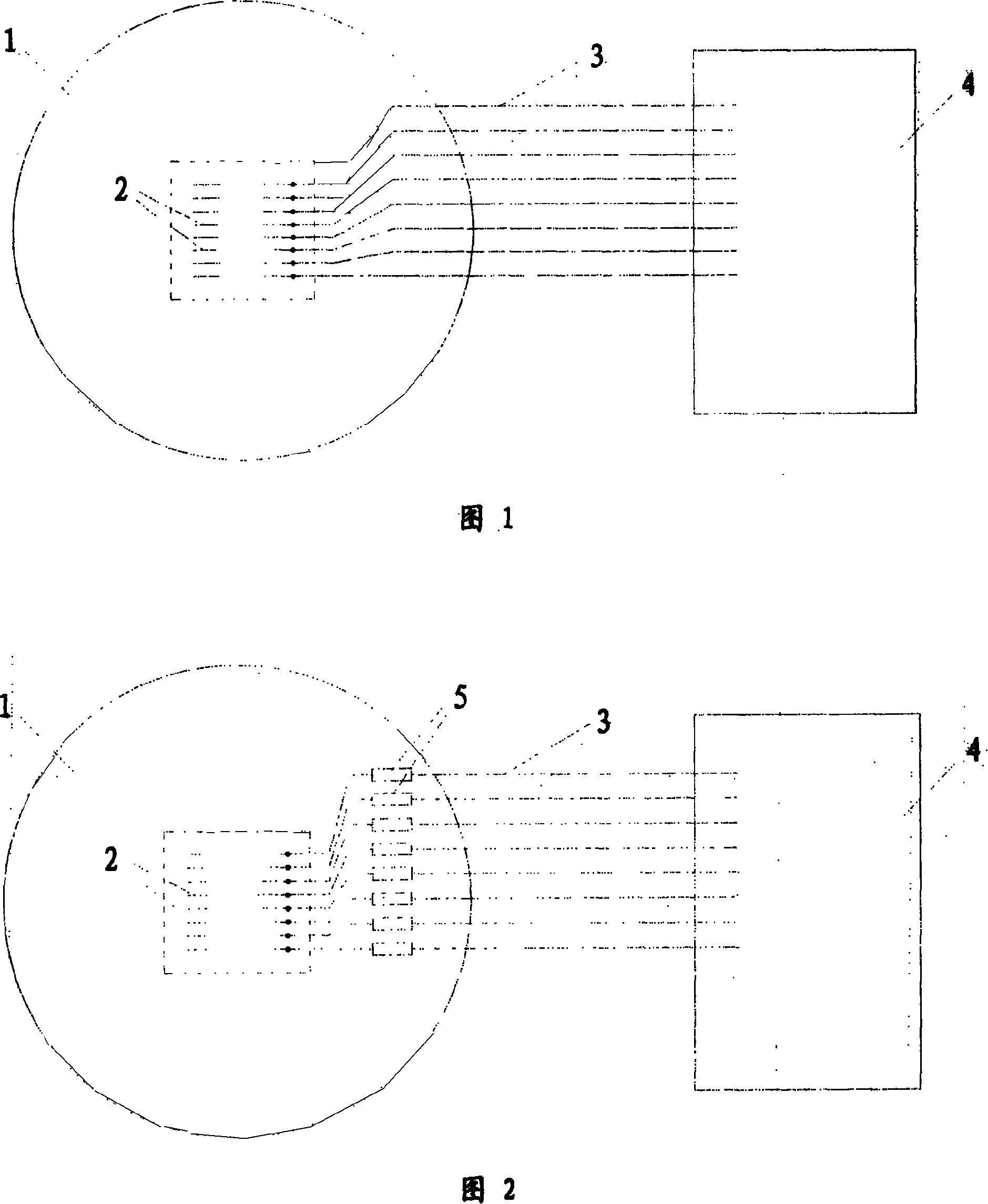

[0014] The overcurrent protection method of the chip test card and the corresponding chip test system of the present invention will be further described in detail below.

[0015] As shown in Figure 2, compared with the existing system, the wafer test system of the present invention adds an overcurrent protection element 5 between the probe 2 and the lead 3, and this protection element 5 can be selected from a fuse or a current limiting element, The material, length, cross-sectional area of the fuse and the parameter value of the current-limiting element can be set according to the safe current that the probe and the test card can withstand. During the wafer testing process, the current on the wafer flows from the probe 2 through the test card 1 , passes through the protection element 5 and the lead wire 3 , and then flows into the test machine 4 . When a certain contact pad on the chip causes the current flowing through the probe 2 to exceed a safe value due to a short circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More