Design method of low-power consumption high performance high speed scratch memory

A high-speed temporary storage and design method technology, which is applied in energy-saving computing, memory systems, instruments, etc., can solve the problems that software cannot control cache data replacement, increase high-speed buffer power consumption, and affect processor performance. System performance enhancement, size reduction, performance enhancement effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

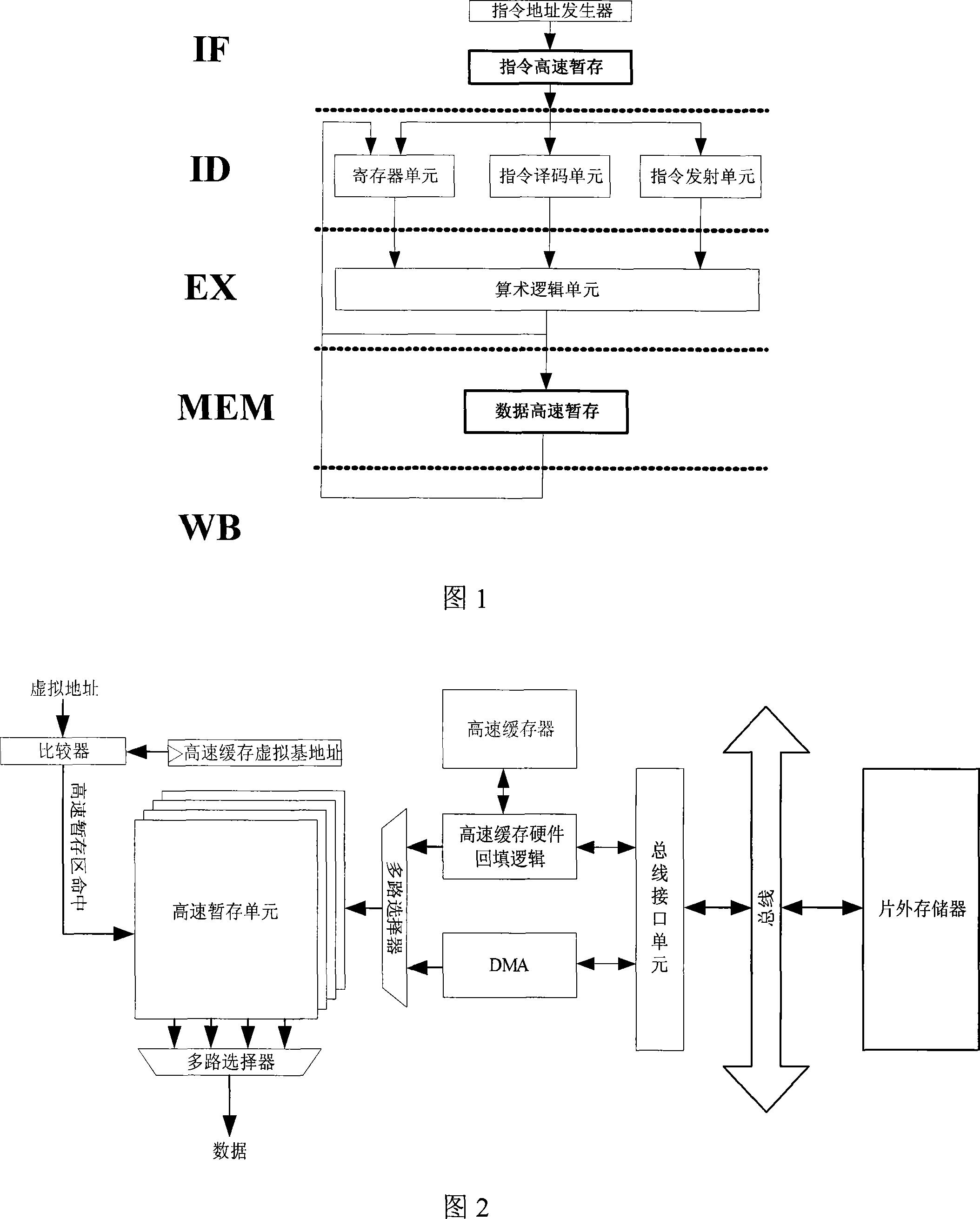

[0033] In the present invention, the high-speed scratchpad is a storage area with continuous storage addresses located on the processor, and is a mapping of an effective part of the memory. Its position and function in the processor pipeline are shown in Figure 1.

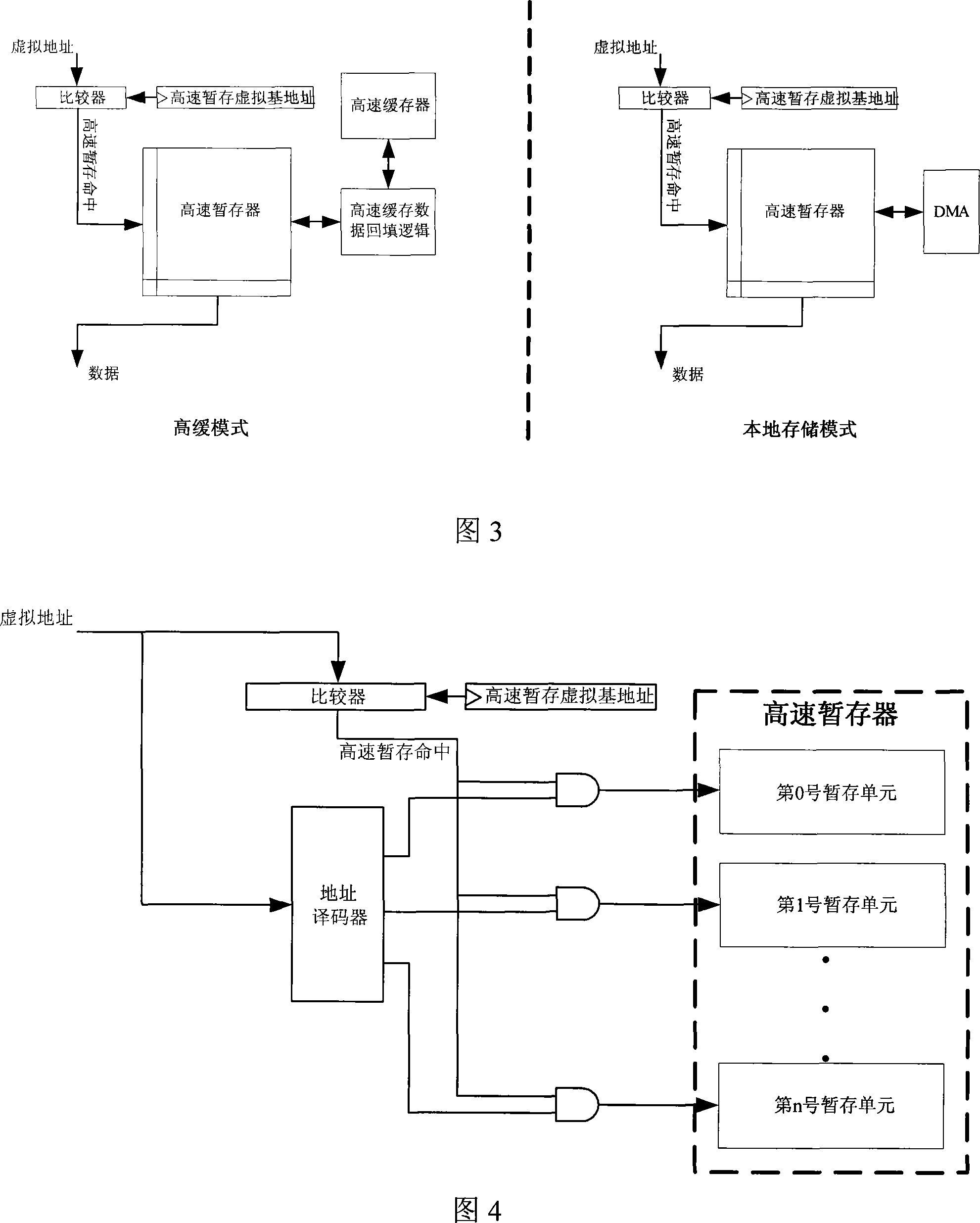

[0034] By designing the access mechanism and physical structure of the high-speed register, the useless power consumption in the process of accessing the high-speed register is avoided, and by increasing the controllability of the data backfill strategy of the high-speed register, the processor system is improved. performance. Its overall architecture and working principle are shown in Figure 2.

[0035] The design method of a kind of low-power consumption high-performance high-speed register that the present invention proposes, its feature comprises as follows:

[0036] 1) The high-speed scratchpad supports two modes of high buffering and local storage;

[0037] 2) The high-speed scratchpad supports dynamic swi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More